跨时钟域操作包括同步跨时钟域操作和异步跨时钟域操作。同步跨时钟域意味着发送时钟和接收时钟是同步的,比如两个时钟是同一个MMCM生成的,在这种情况下,这两个时钟有明确的相位关系。

所以,同步跨时钟域操作重要的是做好约束。无论是从快时钟域到慢时钟域还是从慢时钟域到快时钟域,都可以通过多周期路径约束实现,同时还要注意时钟偏移对跨时钟域路径时序的影响。

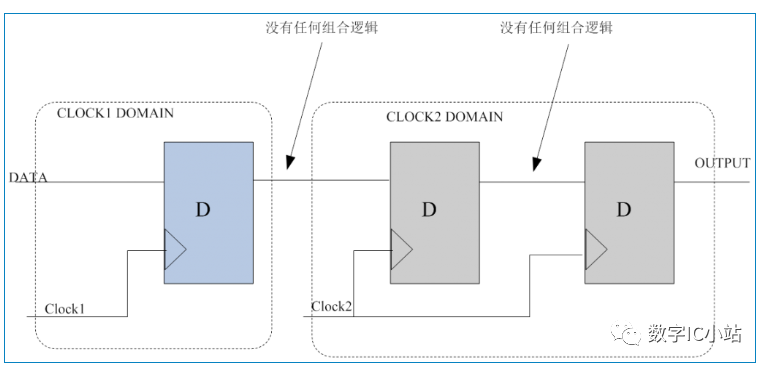

对于异步跨时钟域操作,由于发送时钟和接收时钟是异步的,也就是两者不存在明确的相位关系,这时既要从硬件电路上保证设计是安全的,又要从约束层面确保数据被稳定接收。

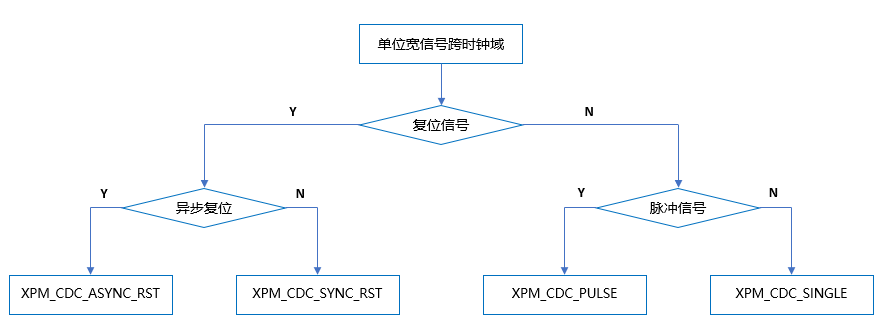

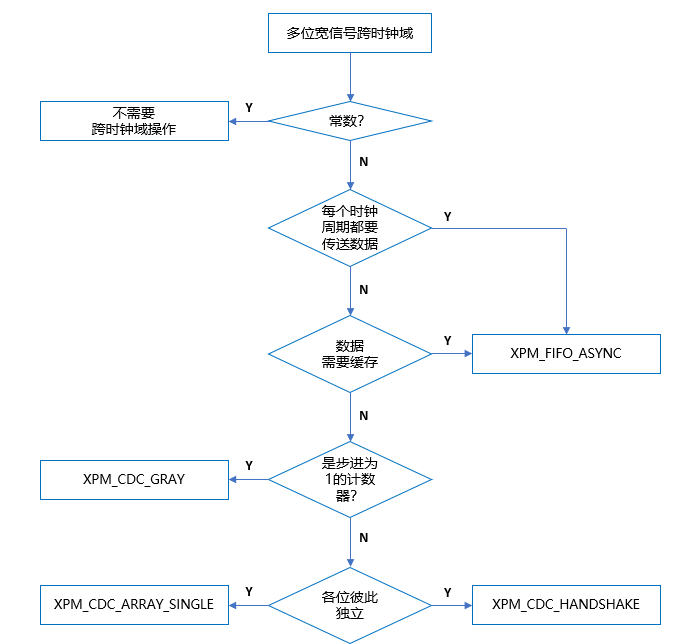

根据数据位宽可分为两种情形:单位宽信号跨时钟域和多位宽信号跨时钟域。此时,可使用XPM_CDC,具体使用哪个模块,可参考如下两个流程。

审核编辑:刘清

-

CDC

+关注

关注

0文章

58浏览量

18506 -

XPM

+关注

关注

0文章

12浏览量

8889

原文标题:跨时钟域电路设计(8):总结

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

从电路的角度出发,提出了一种新的SOC跨时钟域同步电路设计的方法

关于FPGA中跨时钟域的问题分析

跨时钟域电路设计:多位宽数据通过FIFO跨时钟域

跨时钟域电路设计:单位宽信号如何跨时钟域

跨时钟域电路设计总结

跨时钟域电路设计总结

评论