开篇立论

跨时钟域信号的打拍处理往往用于单比特信号或类似于格林码这种信号的跨时钟域处理。其逻辑电路很简单。SpinalHDL提供了BufferCC用于实现这种跨时钟域打拍处理方式:

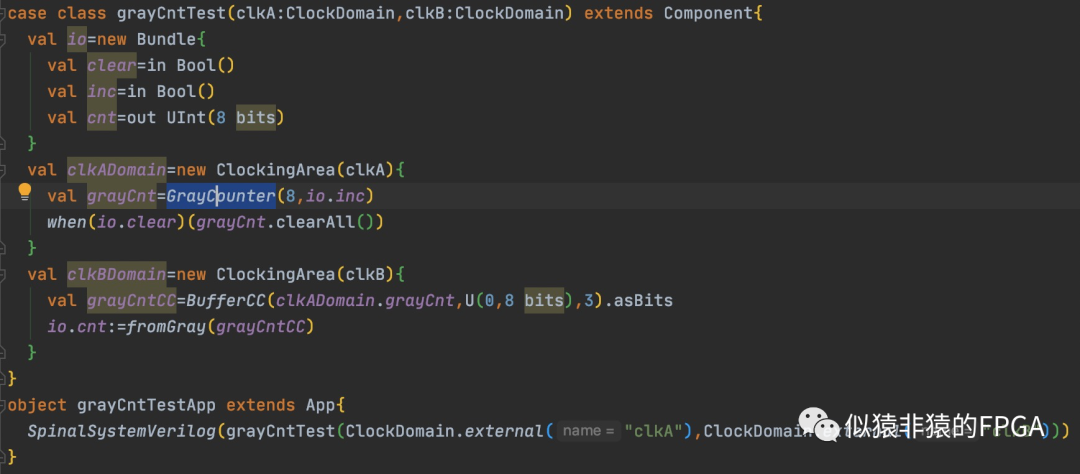

在日常的电路设计里,计数器是常见的DFX信号,有些情况下需要将一个时钟域的DFX信号转换到另一个时钟域进行HPI读取,这种情况也可以通过打拍进行处理,不过前提是需转换成格林码,如此在源时钟域和目的时钟域需分别做一次转换与反转换。但如果计数器采用格林码进行计数则可以少进行一次转换。SpinalHDL有提供一个GrayCounter方法用于生成格林码计数器:

除了StreamCCByToggle,SpinalHDL里还有一个FlowCCByToggle。由于Flow类型没有反压,因而从低时钟域向高时钟域进行传输则没什么问题,但从高时钟域向低时钟域进行转换则存在丢失数据的风险。

FIFO跨时钟域缓存

对于高吞吐的多比特信号跨时钟域处理,则往往采用FIFO的形式进行处理。在SpinalHDL里则有StreamFifoCC供使用:

每一个做数字逻辑的都绕不开跨时钟域处理,谈一谈SpinalHDL里用于跨时钟域处理的一些手段方法。

打拍处理跨时钟域信号的打拍处理往往用于单比特信号或类似于格林码这种信号的跨时钟域处理。其逻辑电路很简单。SpinalHDL提供了BufferCC用于实现这种跨时钟域打拍处理方式:

BufferCC(input: T, init: T = null, bufferDepth: Int = 2)

bufferDepth可用于指定打拍级数。input信号的时钟域为源时钟域,BUfferCC调用的地方的时钟域为目的时钟域。在日常的电路设计里,计数器是常见的DFX信号,有些情况下需要将一个时钟域的DFX信号转换到另一个时钟域进行HPI读取,这种情况也可以通过打拍进行处理,不过前提是需转换成格林码,如此在源时钟域和目的时钟域需分别做一次转换与反转换。但如果计数器采用格林码进行计数则可以少进行一次转换。SpinalHDL有提供一个GrayCounter方法用于生成格林码计数器:

GrayCounter(width: Int, enable: Bool)

提供一个小demo,GtayCounter+BufferCC:

:Bool,clockIn:ClockDomain,clockOut:ClockDomain):Bool

握手处理

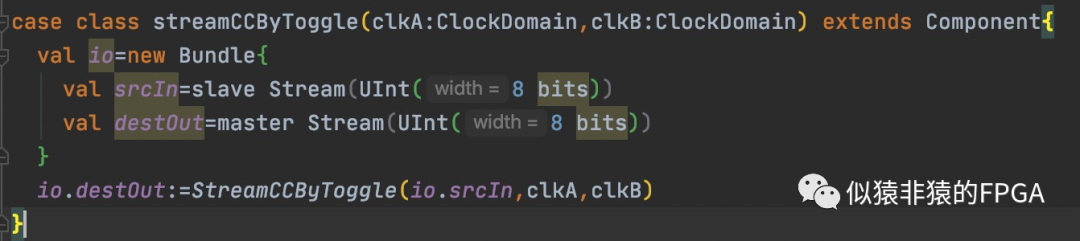

对于吞吐要求不是特别高的场合,跨时钟域信号采用握手形式进行处理也是一种不错的选择。SpinalHDL有两个抽象类型个人一直很喜欢:Stream,Flow。这两种形式基本囊括了所有的信号交互行为,其也可以说是SpinalHDL lib库的基石。针对跨时钟域的握手处理,SpinalHDL有一个StreamCCByToggle可以使用:

StreamCCByToggle(input: Stream[T], inputClock: ClockDomain, outputClock: ClockDomain): Stream[T]

其输入参数包含源时钟域信号,源时钟域,目的时钟域,其返回一个目的时钟域的Stream信号:

除了StreamCCByToggle,SpinalHDL里还有一个FlowCCByToggle。由于Flow类型没有反压,因而从低时钟域向高时钟域进行传输则没什么问题,但从高时钟域向低时钟域进行转换则存在丢失数据的风险。

FIFO跨时钟域缓存

对于高吞吐的多比特信号跨时钟域处理,则往往采用FIFO的形式进行处理。在SpinalHDL里则有StreamFifoCC供使用:

val myFifo = StreamFifoCC(dataType = Bits(8 bits),depth = 128,pushClock = clockA,popClock = clockB)<< streamAmyFifo.io.pop>>streamB

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

信号处理

+关注

关注

49文章

1095浏览量

104882 -

时钟

+关注

关注

11文章

1953浏览量

134543 -

数字逻辑

+关注

关注

0文章

74浏览量

17369

原文标题:跨时钟域那点事儿

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

看看Stream信号里是如何做跨时钟域握手的

一些,适用于追求高吞吐的场景。写在最后逻辑处理里很多总线都是基于Stream这种信号来实现的(如AXI4家族),通过上面的方法,可以很容易根

发表于 07-07 17:25

基于FPGA的跨时钟域信号处理——MCU

问题,不过请注意,今后的这些关于异步信号处理的文 章里将会重点从工程实践的角度出发,以一些特权同学遇到过的典型案例的设计为依托,从代码的角度来剖析一些特权同学认为经典的

发表于 11-01 16:24

•11次下载

SpinalHDL里用于跨时钟域处理的一些手段方法

SpinalHDL里用于跨时钟域处理的一些手段方法

评论