逻辑芯片输入的低电平有效和高电平有效

- 编码器(141819)

- 电平(41392)

- 数字电路(83193)

- 逻辑芯片(31956)

相关推荐

热点推荐

一个MOSFET电平转换电路原理

电路原理很简单,分两种情况:

1.从A到B

A为高电平时,MOS管关断,B端通过上拉,输出高电平;

A为低电平时,MOS管内的体二极管导通,使MOS管的S极被拉低,从而使Vgs

2025-12-04 06:27:31

单片机TTL和CMOS电平知识

输入电平:高电平Uih >= 2.0v,低电平 Uil <= 0.8v

TTL电压:一般为5V,现在也有LVTTL支持3.3V、2.5V、1.8V。为了方便,后面统称

2025-12-03 08:10:03

力芯微逻辑类IC电平转换系列芯片助力网络传输

数字化时代,网络传输作为信息传递的核心手段,其稳定性和高效性至关重要。而电平转换芯片作为网络传输中的关键组件,能够确保不同电压域电路模块之间的信号正常传输。力芯微授权代理商南山电子认为,力芯微逻辑类

2025-11-11 15:39:26 981

981

981

981

浅谈DDR的逻辑电平标准

总所周知,一般我们在对通信芯片互连的时候,要求两者的IO接口电平标准是一样的,而在学习FPGA与DDR互连的时候,查看网上的资料却很少提及这方面,都是直接教你怎么连接,不明所以,所以这里简单做了下笔记。

2025-10-29 11:09:33 3012

3012

3012

3012

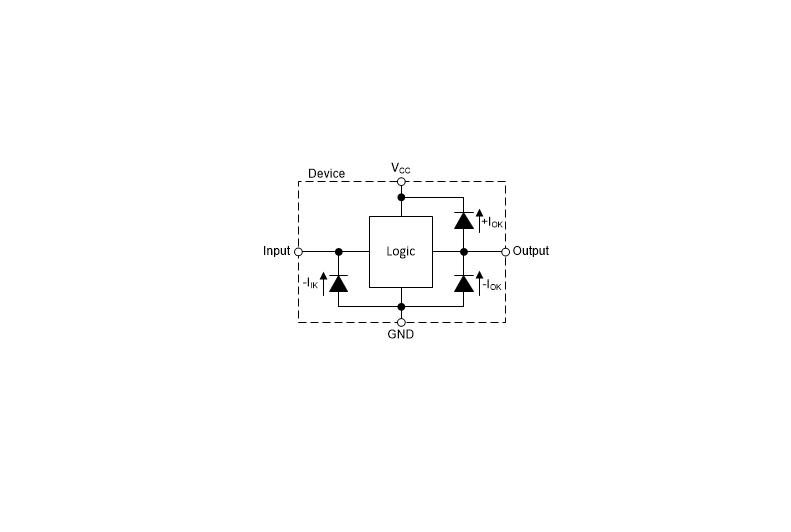

MDD 逻辑IC的逻辑电平不兼容问题与解决方案

)不断被引入市场,它们具有各自的优势,但也带来了逻辑电平不兼容的问题,尤其是在多个不同类型的逻辑IC互联时,电平不匹配的问题显得尤为突出。作为FAE,帮助客户理解

2025-10-29 09:39:07 241

241

241

241

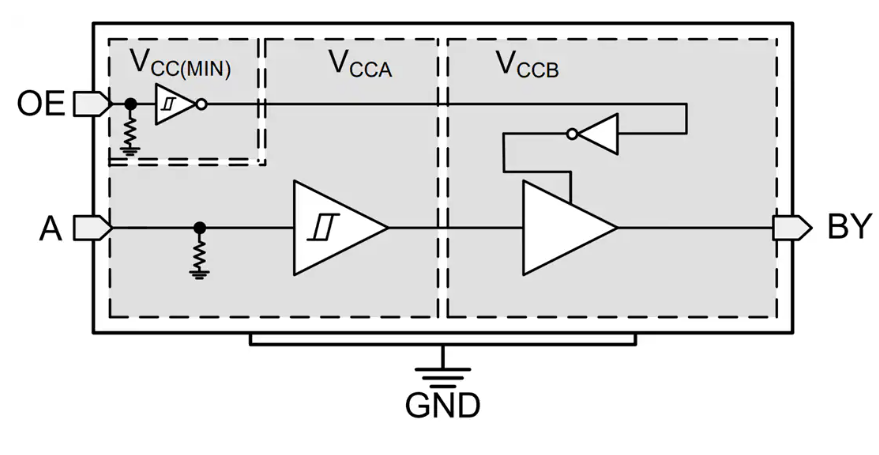

SN54SC1G125-SEP 文档总结

SN54SC1G125-SEP 是一款具有 3 态输出的单线驱动器。当输出使能(OE)输入引脚处于逻辑高电平时,输出被禁用。当 (OE) 处于逻辑低电平时,真实数据从 A 输入传递到 Y 输出。

2025-09-28 14:12:30 1010

1010

1010

1010

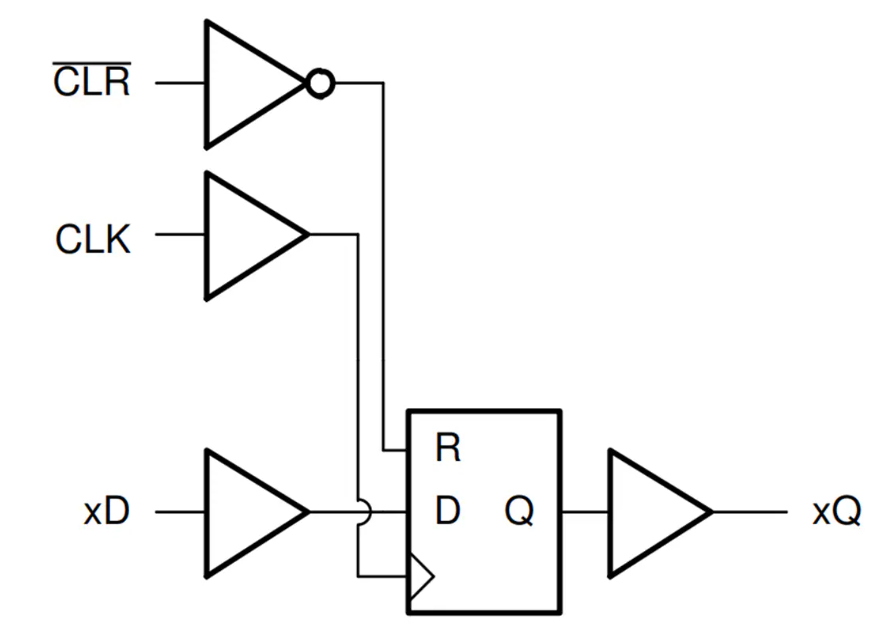

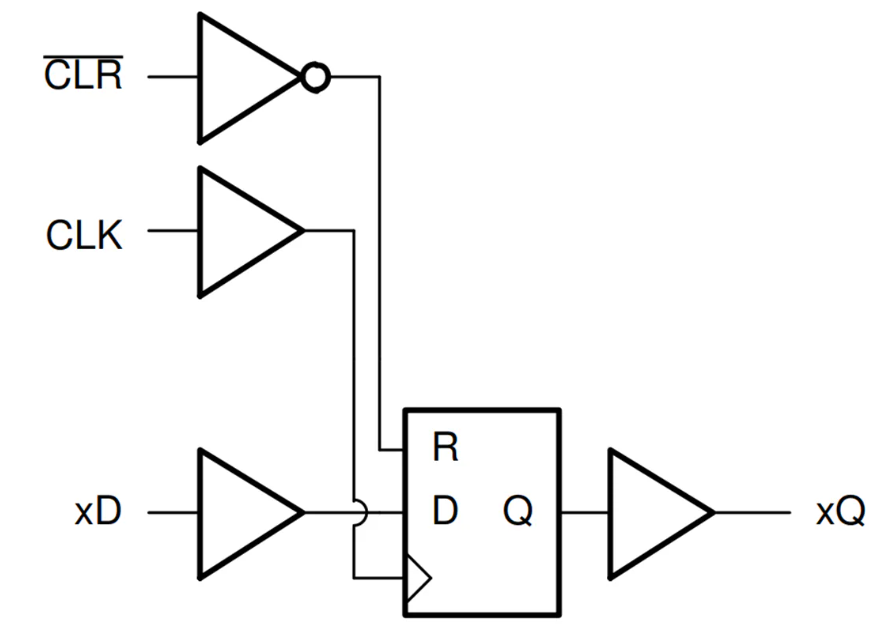

SN74LV8T273-Q1 汽车级八路D型触发器数据手册总结

SN74LV8T273-Q1 包含 8 个正边沿触发的 D 型触发器,具有直接低电平有效清除 (CLR) 输入。

满足建立时间要求的数据 (D) 输入端的信息传输到时钟 (CLK) 脉冲正向沿

2025-09-28 13:40:48 1015

1015

1015

1015

SN74LV8T273 八路D型触发器技术文档总结

该SN74LV8T273包含八个正边沿触发的D型触发器,具有直接的低电平有效清除(CLR)输入。

满足建立时间要求的数据 (D) 输入端的信息传输到时钟 (CLK) 脉冲正向沿的 Q 输出

2025-09-28 10:30:09 742

742

742

742

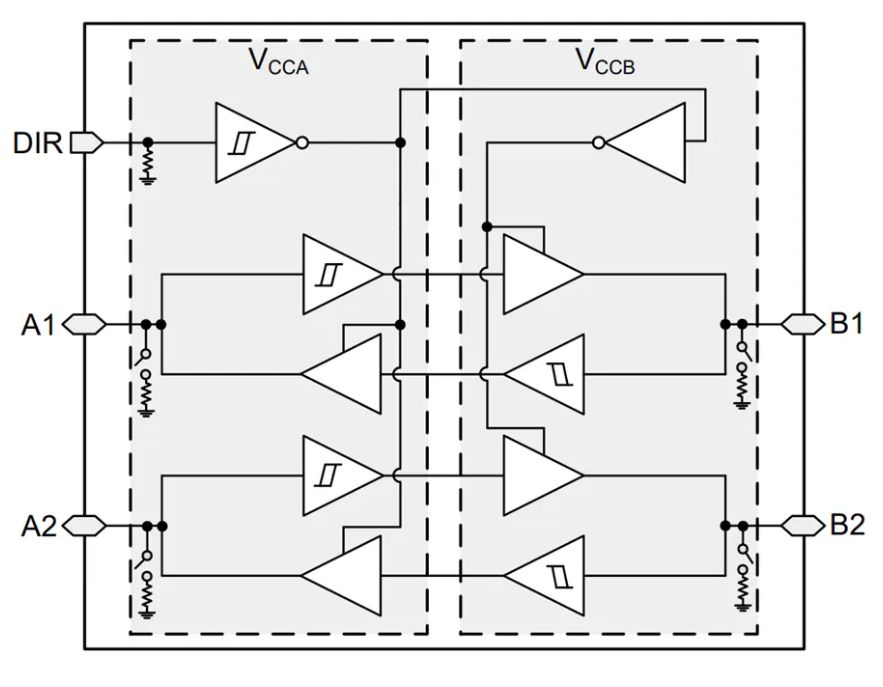

SN74LCX2T45双向电平转换器技术解析

5.5V I/O电压。DIR上的高电平允许从A传输到B,DIR上的低电平可允许B至A数据传输。SN74LXC2T45-Q1器件符合AEC-Q100标准,适用于汽车应用。

2025-09-24 09:22:41 684

684

684

684

Texas Instruments TXU0101/Q1电压电平转换器技术解析

V~CCB~逻辑电平为基准,B引脚以V~CCB~逻辑电平为基准。A端口可接受1.1V至5.5V的输入电压,而B端口也可接受 1.1V至5.5V的输入电压。当电源OE设为高电平时,则允许数据沿固定方向从

2025-09-16 15:21:50 646

646

646

646

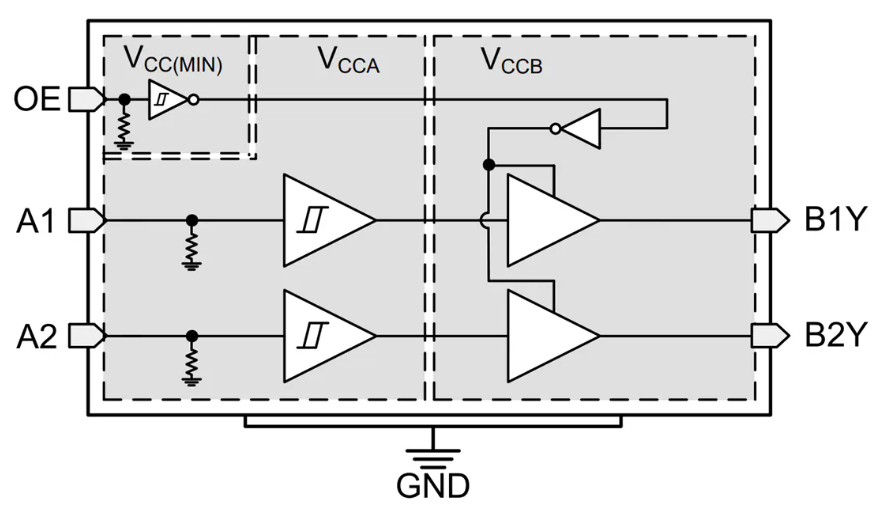

TXU0102双比特电压电平转换器技术解析与应用指南

为基准,Bx引脚以V~CCB~逻辑电平为基准。A端口可接受1.1V至5.5V的输入电压,而B端口也可接受 1.1V至5.5V的输入电压。当电源OE设为高电平时,则允许数据沿固定方向从A传输到B

2025-09-16 14:57:44 635

635

635

635

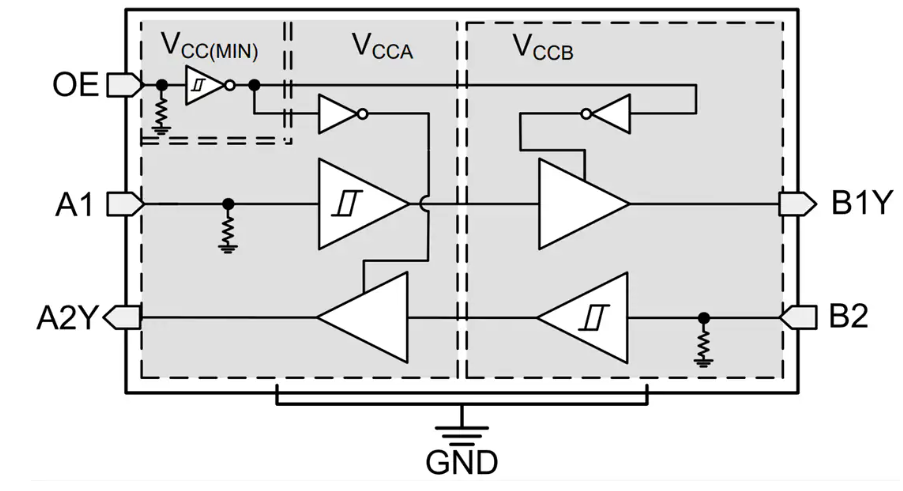

Texas Instruments TXU0202电压电平转换器技术解析与应用指南

~或V~CCB~逻辑电平为基准,Bx引脚以V~CCB~逻辑电平为基准。A端口可接受1.1V至5.5V的输入电压,而B端口也可接受 1.1V至5.5V的输入电压。当电源OE设为高电平时,则允许数据沿固定

2025-09-16 14:53:06 620

620

620

620

光模块TTL电平是什么?

TTL电平信号规定,+5V等价于逻辑“1”,0V等价于逻辑“0”(采用二进制来表示数据时)。这样的数据通信及电平规定方式,被称做TTL(晶体管-晶体管逻辑电平)信号系统。这是计算机处理器控制的设备

2025-08-27 18:13:57 855

855

855

855请问为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

2025-08-27 15:00:23

什么情况会导致BUFFER_RYD一直为低电平?

一直为低电平

按照“Detailed LVDS transaction diagram”中的流程,在完成“PHY and LINK training”后,BUFFER_RDY信号应该从低电平拉升

2025-08-14 06:21:46

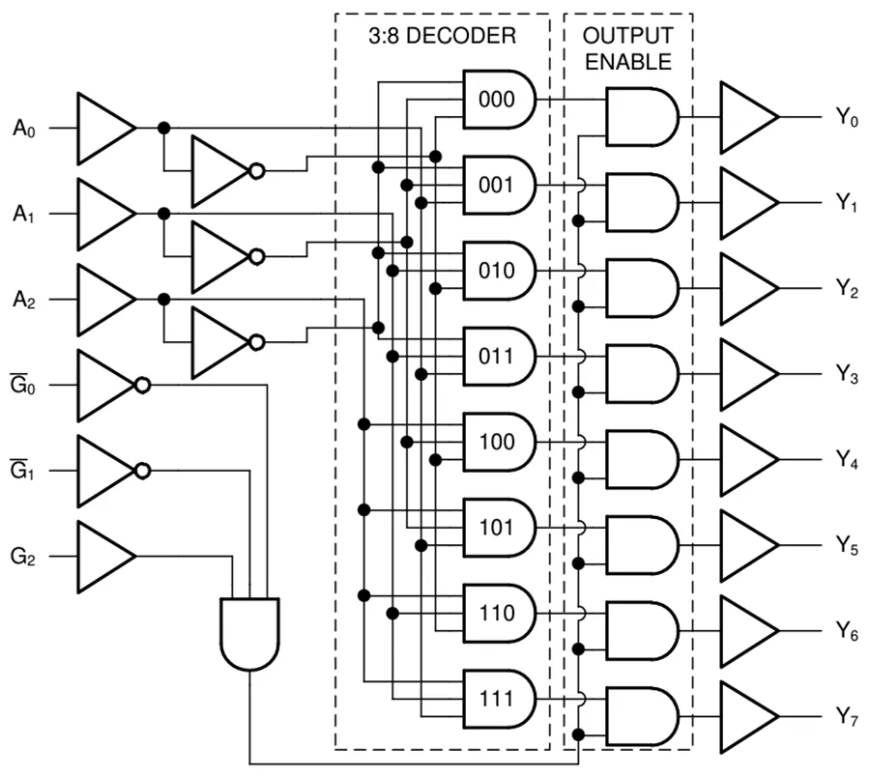

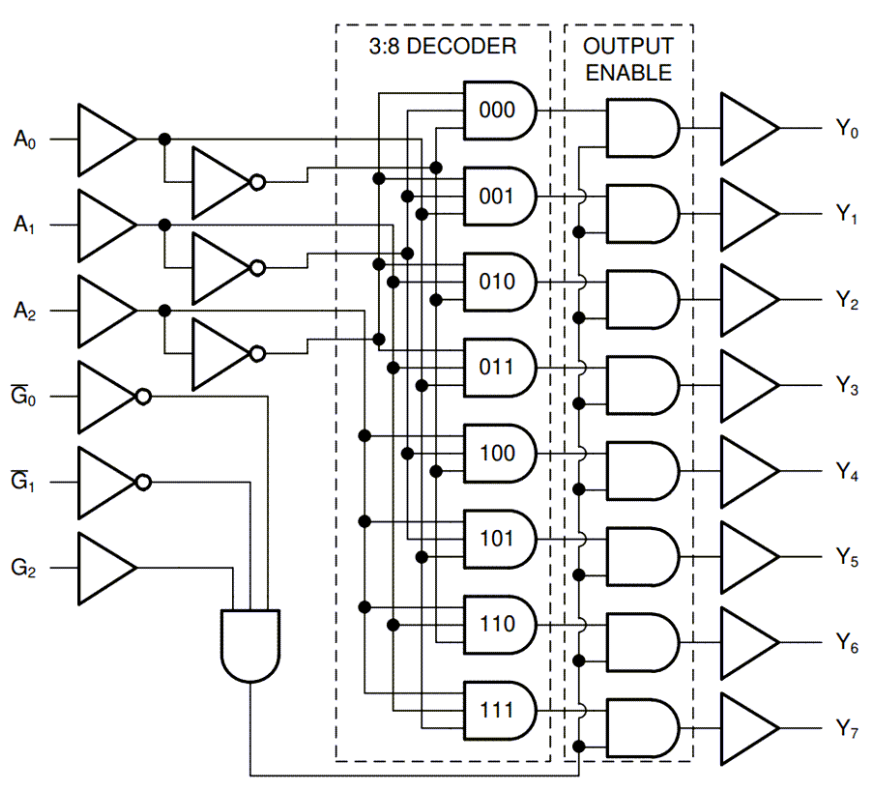

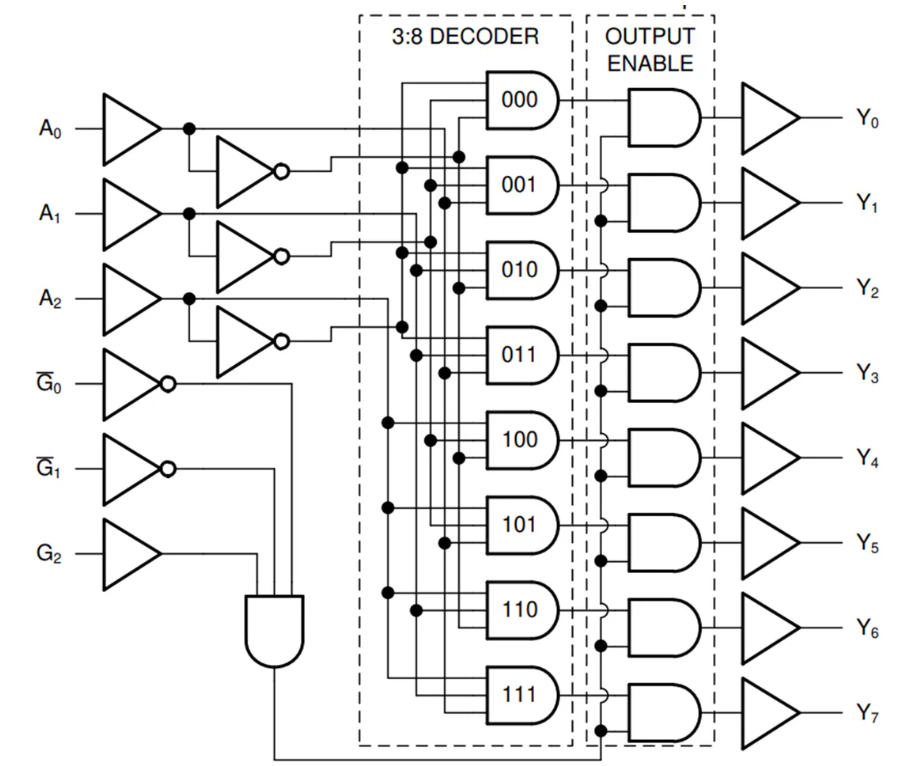

Texas Instruments SN74AHC238/SN74AHC238-Q1 3线至8线解码器/解复用器数据手册

和G0)。当输出被任何选通输入选通时,器件都会强制进入低电平状态。 当选通输入未禁用输出时,只有选定的输出为高电平,所有其他输出均为低电平。Texas Instruments SN74AHC238-Q1器件符合AEC-Q100标准,适用于汽车应用。

2025-08-01 11:43:15 1048

1048

1048

1048

微源半导体推出14通道电平转换芯片LP6274

LP6274是一款专为GOA(Gate On Array)TFT-LCD面板设计的14通道电平转换芯片。它能够将由显示时序控制器(TCON)生成的逻辑电平控制信号转换为LCD面板所需的高低电压电平信号。

2025-07-24 17:43:23 862

862

862

862

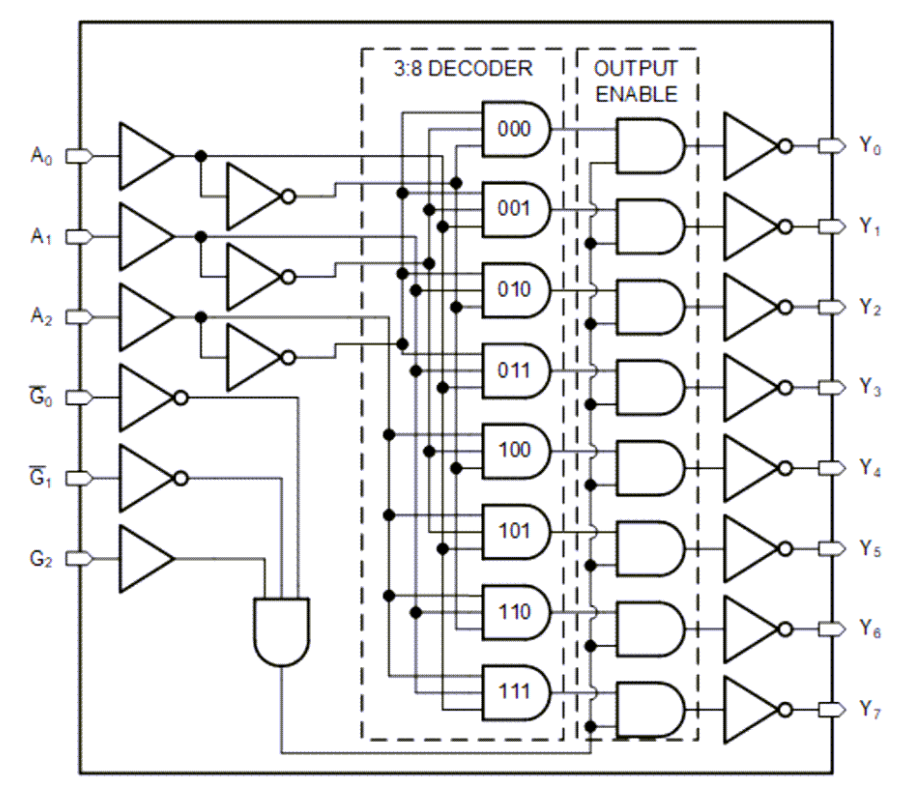

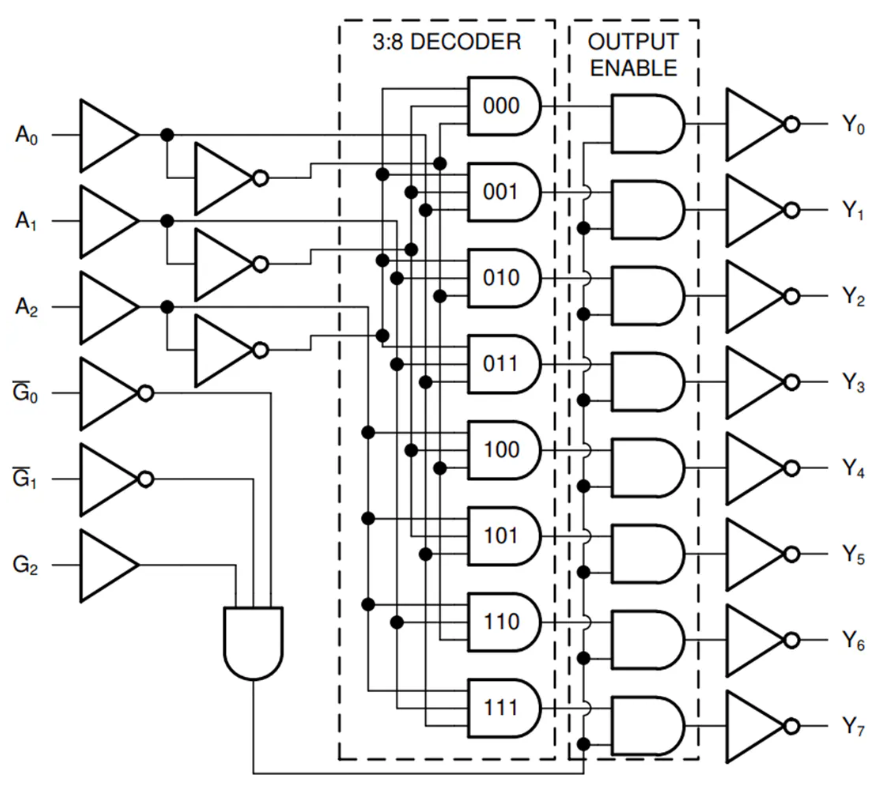

Texas Instruments SN74AC138-Q1 3线至8线反相解码器/解复用器数据手册

Instruments SN74AC138-Q1的输出被任何选通输入选通时,所有输入都会强制进入高电平状态。当选通输入未禁用输出时,所选输出为低电平,而所有其他输出为高电平。

2025-07-24 15:28:21 546

546

546

546

Texas Instruments SN74AC238-Q1 3线至8线反相解码器/解复用器数据手册

Instruments SN74AC238-Q1输出被任何选通输入控制时,所有输入都会被强制转为低电平状态。当选通输入不禁用输出时,所选输出为高电平,而所有其他输出为低电平。

2025-07-24 15:14:58 554

554

554

554

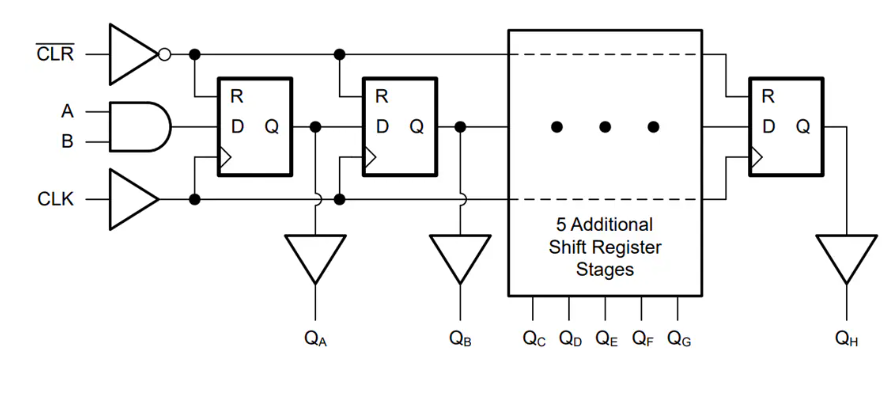

Texas Instruments CD74AC164/CD74ACT164 8位SIPO移位寄存器数据手册

信号,才能将输入数据线设置为高电平;其中任何一个低电平信号都会将输入数据线设置为低电平。在CLK为高电平或低电平时,只要满足最短设置时间要求,就可以更改A和B的数据。

2025-07-17 10:43:35 588

588

588

588

Texas Instruments SN74ACT174-Q1六路D型触发器数据手册

Texas Instruments SN74ACT174-Q1六路D型触发器包含六个D型触发器,具有共享低电平有效清除 (CLR) 和上升沿触发 (CLK) 输入。数据 (D) 输入端符合设置时间

2025-07-16 10:26:12 622

622

622

622

Texas Instruments SN74AC174-Q1六路D型触发器数据手册

Texas Instruments SN74AC174-Q1六路D型触发器包含六个D型触发器,具有共享低电平有效清除 (CLR) 和上升沿触发 (CLK) 输入。数据 (D) 输入端符合设置时间要求

2025-07-16 10:18:23 594

594

594

594

Texas Instruments SN74ACT238/SN74ACT238-Q1 3线至8线解码器/解复用器特性/应用/功能图

Texas Instruments SN74ACT238/SN74ACT238-Q1 3线至8线解码器/解复用器包含一个标准输出选通(G2)和两个低电平有效的输出选通(G1和G0)。当通道选通输入

2025-07-07 15:19:13 572

572

572

572

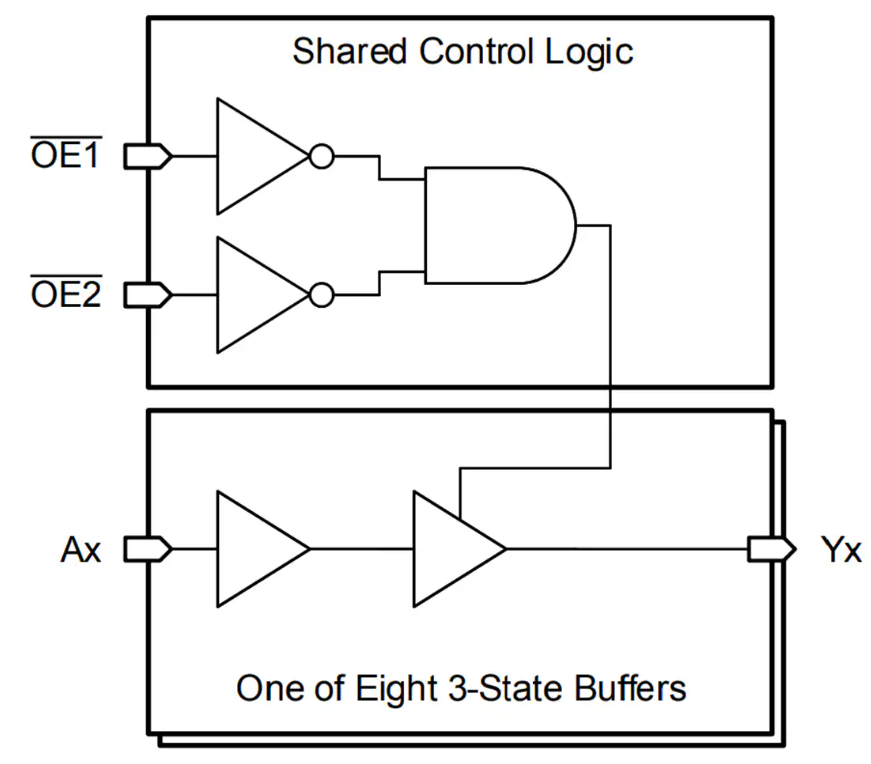

Texas Instruments SN74LV8T541-EP八通道缓冲器和线路驱动器数据手册

Texas Instruments SN74LV8T541-EP八路缓冲器/线路驱动器包含八个具有3态输出的缓冲器。低电平有效输出能够使引脚(OE1和OE2)配置为使输出都必须为低电平才能有效,并

2025-07-05 10:15:18 615

615

615

615

Texas Instruments SN74LV8T138-EP 3对8线路解码器/解复用器数据手册

Texas Instruments SN74LV8T138-EP 3对8线路解码器/解复用器具有两个低电平有效输出选通(G1和G0)和一个标准输出选通 (G2)。当输出被任一选通输入限制时,输出均

2025-07-05 09:20:00 638

638

638

638

ADCMP354YKSZ-REEL7内置0.6 V基准电压源、开漏高电平有效输出比较器 高集成度低功耗比较器解决方案

),避免外部电平转换电路。

开漏高电平有效输出 :支持灵活上拉至外部电压(最高22V),可直接驱动数字逻辑或MOSFET。

能效与精度优化

超低功耗 :静态电流仅10μA(典型值),延长电池供电设备寿命

2025-06-20 08:51:18

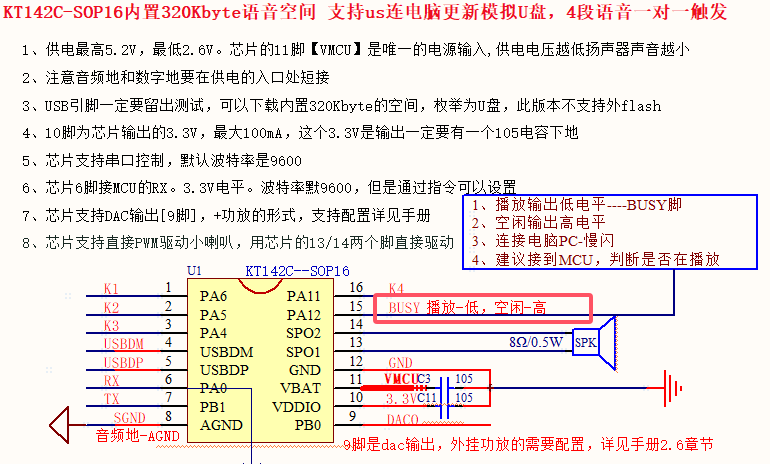

为什么 KT142C 芯片 BUSY 脚空闲高电平仅 0.2V?附低功耗模式配置指南

文档围绕 KT142C 芯片 busy 引脚展开,该引脚为 15 脚 PA12,播放时输出低电平,空闲时本应输出 3.3V 高电平,但芯片空闲 5 秒进入 2μA 超低功耗状态后,busy 脚呈高阻

2025-06-16 09:38:26 995

995

995

995

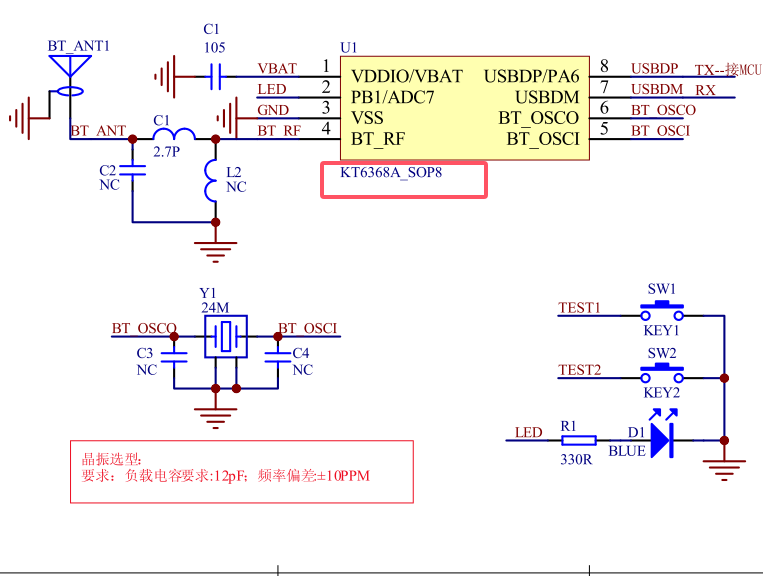

抖音蓝牙遥控器芯片方案、自拍器蓝牙芯片方案 简易版 io控制

1、蓝牙名称:默认KT6368A-EDR-KEY,没有休眠,不用按键唤醒,开机通电直接启动

2、蓝牙芯片2脚=PA9 开机默认高电平,正常广播就是低电平 === 其实这个脚要不要没关系,蓝牙芯片

2025-06-14 15:45:33 1159

1159

1159

1159

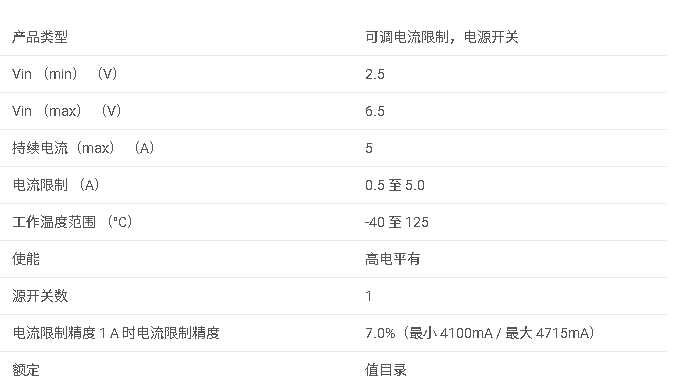

TPS2557 0.5-5A 可调 ILIMIT,2.5-6.5V,22mΩ USB 电源开关,高电平有效数据手册

控制,以最大限度地降低 导通和关断期间电流浪涌。

TPS255x 器件通过切换到 恒定电流模式,当输出负载超过限流阈值时。FAULT 逻辑输出在过流和过热期间保持低电平 条件。

2025-05-26 15:23:37 601

601

601

601

NCA9555 具有16位通用并行I²C总线数输入输出GPIO扩展功能

。NCA9555由两个8位配置(输入或输出选择)组成。输入,输出和极性反转(高电平有效或低电平有效)寄存器。通过写入I/O配置位,系统主机可以将I/O启用为输入或输出。每个输入或输出的数据都保存在相应的输入或

2025-05-19 18:02:29 0

0

0

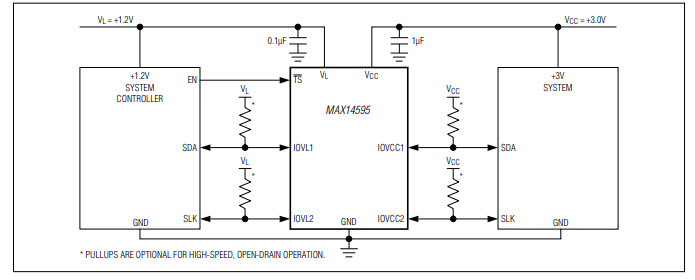

0MAX14595高速、漏极开路逻辑电平转换器技术手册

MAX14595为双通道、双向逻辑电平转换器,设计用于手持设备和电池供电等低功耗应用。 外部电压V~CC~和V~L~设置器件两侧的逻辑电平。 将V~L~侧的逻辑信号转换成V~CC~侧相同的逻辑信号,反之亦然。

2025-05-15 15:37:46 719

719

719

719

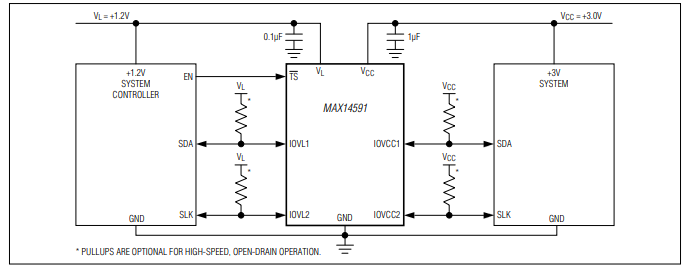

MAX14591高速、漏极开路逻辑电平转换器技术手册

MAX14591为双通道、双向逻辑电平转换器,为多电压供电系统的数据传输提供必要的电平转换。外部电压V~CC~和V~L~设置器件两侧的逻辑电平。V~L~侧的逻辑信号被转换成V~CC~侧相同的逻辑信号,反之亦然。

2025-05-15 15:28:19 711

711

711

711

MAX14611 4通道双向逻辑电平转换器技术手册

逻辑信号,反之亦然。

器件理想用于漏极开路I²C总线和MDIO总线,具有三态输出模式(/TS)。将/TS上拉至I/O口电源,置于逻辑高电平,从而在关闭电平转换功能时支持供电侧的连续、不间断I²C的工作。MAX14611采用TDFN封装,是MAX3378E引脚兼容的升级版本。

2025-05-15 15:22:31 676

676

676

676

电平转换电路设计原理和常见问题及解决办法

原理分析 当输入端3.3V为低电平时,D1导通,输出端 1.8V为低电平,实现两端都为低电平。当输入端 3.3V为高电平时,D1截止,输出端被 R1 上拉至 1.8V ,为高电平,实现两端都为高电平。 二

2025-04-27 15:54:19

纳祥科技74HC164D中文规格书,移位寄存器,替代SN74HC164DR

纳祥科技74HC164D是一款8位移位寄存器芯片,具有与门控串行输入和异步清除(CLR)输入,门控串行(A和B)输入允许完全控制输入数据,任一输入端的低电平抑制输入新数据,并在下一个时钟(CLK

2025-04-19 08:57:36 2

2

2

2DS1232LPS-2+T&R,在什么情况下,5脚RST会一直输出高电平?

DS1232LPS-2+T&R,这款芯片在什么情况下,5脚RST会一直输出高电平?(正常时序是上电有个400多ms的高电平后,一直处于低电平,如果7脚没有及时喂狗,会触发复位,也就是重复400多ms的高电平后,一直处于低电平)

2025-04-18 07:51:16

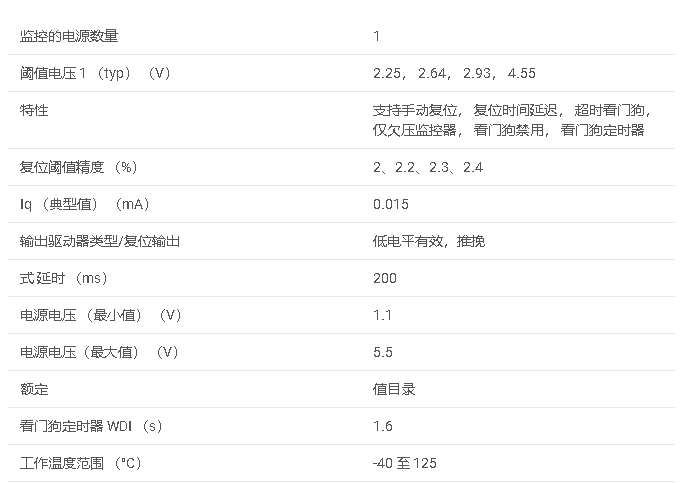

TPS3823 低电平,推挽式,电压监控器(复位IC),带1.6秒看门狗和手动复位数据手册

VIT−,电源电压监控器就会监控 VDD 并保持 RESET 低电平。内部定时器延迟输出返回到非活动状态(高),以确保系统正确复位。延迟时间 td 在 VDD 上升到阈值电压 (VIT− + VHYS) 以上后开始。当电源电压降至阈值电压 VIT− 以下时,输出再次变为有效 (低电平)。无需外部组件。

2025-04-12 17:20:16 2407

2407

2407

2407

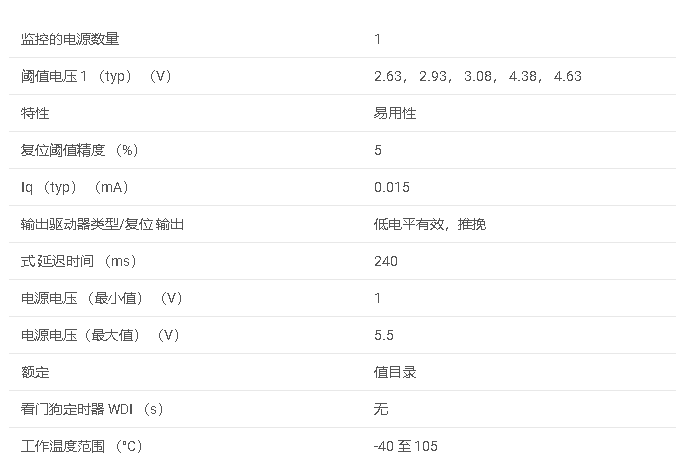

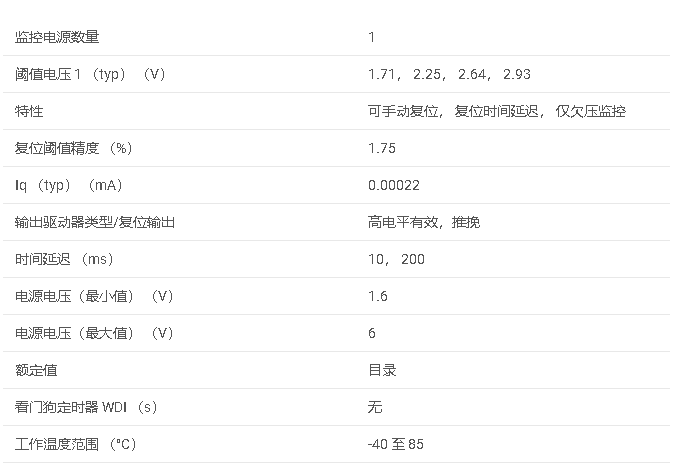

LM809系列 3 引脚电压监控器(复位 IC),具有低电平有效、推挽式复位功能,用于电源监控数据手册

,并在此电压降至工厂编程的电压以下时触发复位信号 reset 阈值。复位信号在 V 后保持 240 ms~抄送~上升到阈值以上。LM809 具有 /RESET 输出,而 LM810 具有高电平有效 RESET 输出。

2025-04-12 17:06:41 1191

1191

1191

1191

TPS3123 低电平,推挽式,电源电压监控器,带看门狗定时器和手动复位数据手册

RESET 输出。阈值电压被编程到器件中,以最大限度地减少外部元件。内置磁滞可防止误触发。RESET 输出对于低于 0.9V 的电源电压 (VDD) 无效。TPS312x 系列包括具有高电平有效输出(用于在故障期间用作禁用)和低电平有效输出(适用于高输出表示系统正常运行的大多数系统)的器件。

2025-04-12 15:43:27 933

933

933

933

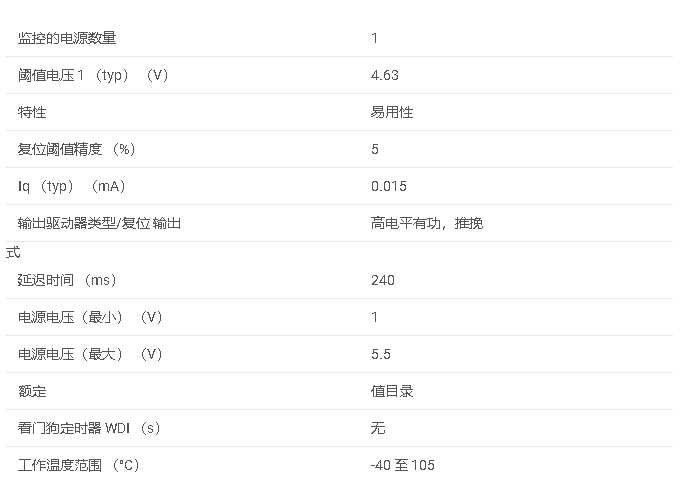

LM810系列 3 引脚电压监控器(复位 IC),带高电平有效、推挽式复位,用于电源监控数据手册

,并在此电压降至工厂编程的电压以下时触发复位信号 reset 阈值。复位信号在 V 后保持 240 ms~抄送~上升到阈值以上。LM809 具有 /RESET 输出,而 LM810 具有高电平有效 RESET 输出。

2025-04-12 15:17:58 789

789

789

789

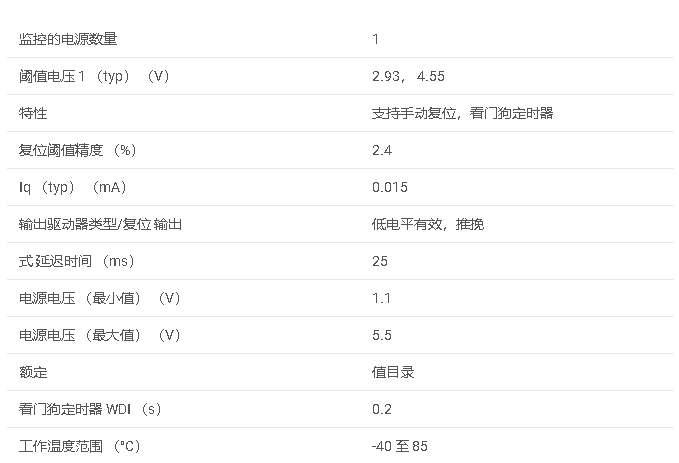

TPS3820 低电平,推挽式,电压监控器(复位IC),带0.2秒看门狗和手动复位数据手册

VIT−,电源电压监控器就会监控 VDD 并保持 RESET 低电平。内部定时器延迟输出返回到非活动状态(高),以确保系统正确复位。延迟时间 td 在 VDD 上升到阈值电压 (VIT− + VHYS) 以上后开始。当电源电压降至阈值电压 VIT− 以下时,输出再次变为有效 (低电平)。无需外部组件。

2025-04-12 15:12:36 1155

1155

1155

1155

TPS3837 高电平有效、推挽式、毫微功耗监控器,带手动复位功能数据手册

1.1 V。此后,监控电路监控 V DD 系列 并保持 RESET 输出有效,只要 V DD 系列 保持在阈值电压 V 以下 它 .一个内部定时器延迟输出返回到非活动状态 (高电平),以确保系统正确

2025-04-12 15:02:31 765

765

765

765

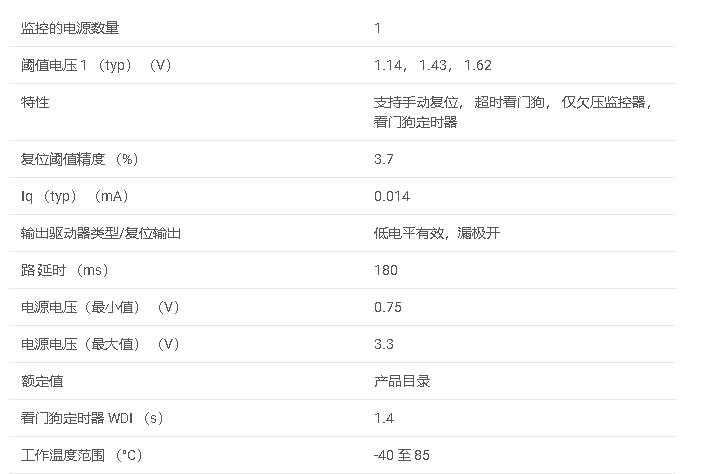

TPS3128 低电平,开漏,电源电压监控器,带看门狗定时器和手动复位数据手册

RESET 输出。阈值电压被编程到器件中,以最大限度地减少外部元件。内置磁滞可防止误触发。RESET 输出对于低于 0.9V 的电源电压 (VDD) 无效。TPS312x 系列包括具有高电平有效输出(用于在故障期间用作禁用)和低电平有效输出(适用于高输出表示系统正常运行的大多数系统)的器件。

2025-04-12 11:36:23 689

689

689

689

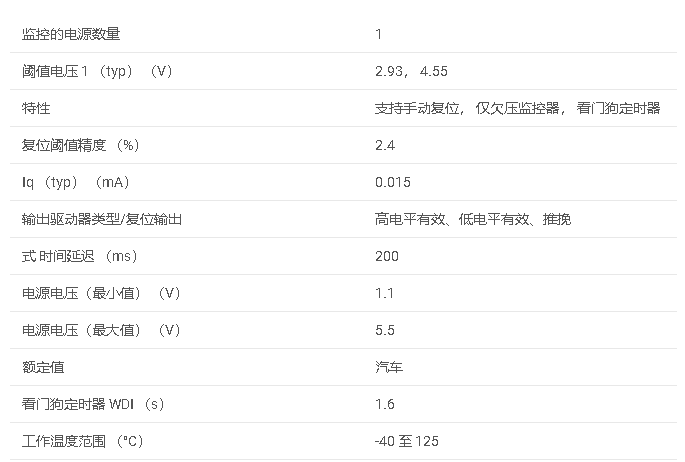

TPS3824-Q1 高电平和低电平有效,汽车电压监控器(复位IC)带看门狗和手动复位技术手册

阈值电压 VIT− 以下,电源电压监控器就会监控 VDD 并保持 RESET 低电平。内部定时器延迟输出返回到非活动状态 (高),以验证系统复位是否正确。延迟时间 td 在 VDD 上升到阈值电压 VIT - 以上后开始。当电源电压降至阈值电压 VIT− 以下时,输出再次变为有效 (低电平)。

2025-04-11 18:01:11 807

807

807

807

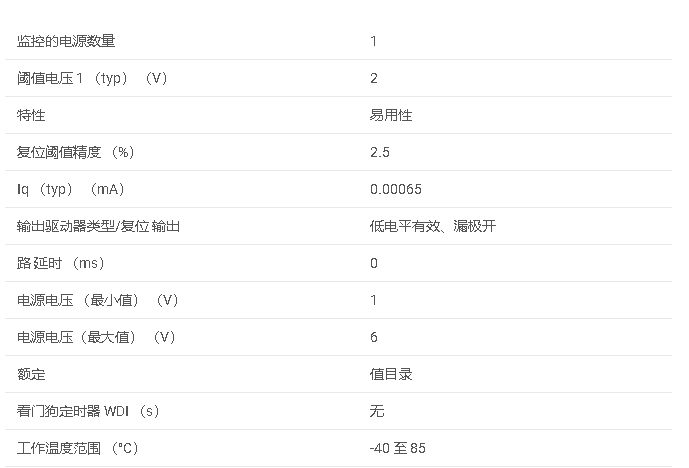

LM8364系列 具有低静态电流和2.5%阈值精度的低电平有效监视器数据手册

LM8364 系列是微功率欠压传感电路,非常适合用于 基于电池供电的微处理器系统,其中延长电池寿命是关键 要求。

阈值电压范围为 2.0V 至 4.5V,低电平有效开路 drain 输出。这些

2025-04-11 16:41:34 698

698

698

698

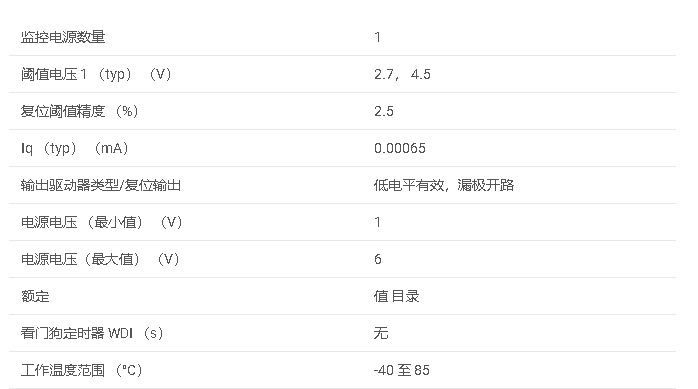

LM8365系列 低电平有效复位IC,具有低静态电流和可编程输出延迟数据手册

LM8365 器件是一款微功率欠压感应电路,非常适合用于 基于电池供电的微处理器系统,其中延长电池寿命是关键 要求。 2.7 V 和 4.5 V 阈值电压可用于低电平有效、漏极开路 输出。这些器件

2025-04-11 16:36:49 731

731

731

731

NS2202X系列40V输入OVP保护IC中文手册

不会被损坏,提高系统的应用可靠性。 NS2202 外置有EN 使能和限流调节ILIMT引脚。在 EN 引脚接入低电平时芯片处于工作模式;在EN引脚接入高电平时则进入关断模式。通过调节ILMT引脚电阻可以调节限流

2025-04-08 14:38:50 0

0

0

0为什么T4240的HRESET引脚总是低电平?

验证:

(1) 我们擦除了 CPLD 中的所有 logic 并使用 CPU 的默认值进行 RCW_SRC,全部设置为 1。上电后,我们测得 PORESET 信号为高电平,但 HRESET 保持低电平

2025-04-04 08:10:47

IO拓展芯片PCAL9722的P1_7引脚设置为上拉输入读取不到正确电平怎么解决?

问题1:IO拓展芯片PCAL9722的P1_7引脚设置为上拉输入读取不到正确电平,默认读取到为1高电平,但是当我给低电平时,读取到的依然是1高电平(通过万用表测量该引脚确为低电平);

问题2:当设置

2025-04-01 06:11:18

如何在不使用DMA的情况下减少ECSPI CS高电平时间?

我遇到了一个问题,即 Chip Select (CS) 在大约 5 μs 内保持高电平。

最初,在使用 DMA 时,我观察到在 SCLK (串行时钟)开始之前,CS 低电平时间延长了约 2.2 μs

2025-03-31 06:56:37

模电与数电的基本知识 (学习备用)

类似TTL和CMOS区别的基础面试题1,TTL电平:输出高电平>2.4V,输出低电平=2.0V,输入低电平Vih,输入低电平Vih>Vt>Vil>Vol。6:Ioh:逻辑门

2025-03-26 19:32:54 1786

1786

1786

1786

硬件基础篇——TTL与CMOS电平

一、电平规范 1、名称解释Uoh -> 输出高电平,Uol -> 输出低电平;Uih -> 输入高电平,Uil -> 输入低电平。2、TTL

2025-03-22 15:21:36

PT2022AT6电容式触摸控制ASIC规格书

前AHLB的输入状态决定 ➢ AHLB管脚接VDD(高电平)上电,上电后OUT输出高电平 ➢ AHLB管脚接GND(低电平)上电,上电后OUT输出低电平• 触摸有效时OUT脚输出状态翻转,松开后恢复初始状态,实现同步开关• 因有物体覆盖触摸盘或环境突

2025-03-17 17:27:06 0

0

0

0DLPC350上电后DMD_PWR_EN始终为低电平是怎么回事?

DLPC350上电后DMD_PWR_EN始终为低电平测试芯片电压正常,请问这个管脚电平在什么情况下高?电路是根据官方参考自己做的。PWRGOOD和POSENSE都为高电平。

2025-02-27 06:32:31

THS1206测试data_av信号输出的高电平和低电平都是mv级别的,请问是什么情况呢?

您好,我在使用THS1206,AVDD=5V,BVDD=DVDD=3.3V;

输入时钟为3MHZ,和FPGA进行连接;

测试data_av信号输出的高电平和低电平都是mv级别的,请问是什么情况呢?

2025-02-14 08:25:17

THS1206写使能是下降沿有效,还是低电平有效?

在向THS1206写控制字时,要写四次。

开始按照写使能,然后连续写四次数据,结果控制字没写进去;

写使能,写一次数据后关闭写使能,第二次写时再打开写使能,这样依次写四次,控制字才写入。

请问为什么呢?不知道写使能是下降沿有效,还是低电平有效?

谢谢!

2025-02-14 08:09:58

ADS1278的SYNC引脚不使用,可以一直上拉到高电平吗?

数据手册看了好几遍,关于ADS1278的SYNC引脚使用还是不很明白。想问下,如果我不用这个引脚的话,可以一直上拉到高电平吗?还有看到如果把他接低电平,AD就停止转换,接到高电平后就恢复转换,这样的话,我可以把他当成一个启动停止转换的开关吗?希望指点。。。谢谢

2025-02-14 06:57:55

ADS1298如果使用寄存器命令RESET去复位,那么其RESET管脚是接高电平还是低电平,还是悬空?

我想问一下ADS1298如果使用寄存器命令RESET去复位,那么其RESET管脚是接高电平还是低电平,还是悬空

2025-02-10 06:00:14

ADS1246芯片上电后,DRDY上一直为低电平,根本没有变化,为什么?

芯片上电后,保证复位时序,给1246的START 脚输入高电平,然后一直发送时钟(cs为低),DRDY上一直为低电平,根本没有变化,请TI工程师多多指教!

2025-02-07 07:33:41

ADS1198 DRDY并没有自动变成高电平,而是一直维持在低电平,为什么?

手册上说DRDY会在SCLK的下降沿自动变成高电平(DRDY s pulled high at the falling edge of SCLK),但为什么我做了几次后发现DRDY并没有自动变成高电平,而是一直维持在低电平。

2025-02-06 07:14:10

ADS1274的DRDY一直是高电平,为什么?

引脚还是一直是高电平。通过DIN和sclk输入数据时,DRDY输出高电平脉冲。DOUT有数据。ADS1274坏了吗?

2025-02-06 07:07:12

ADS7864上电之后是不是BUSY脚为高电平(没有开启转换)?

ADS7864 上电之后是不是BUSY 脚为高电平(没有开启转换)? 为什么我的ADS7864的BUSY 一直是低电平呢?是硬件问题?

2025-02-06 06:33:17

国产替代SN74HC164DR,纳祥科技8位移位寄存器74HC164D时钟速率可达 25MHz

74HC164D是一款8位移位寄存器芯片,具有与门控串行输入和异步清除(CLR)输入,门控串行(A和B)输入允许完全控制输入数据,任一输入端的低电平抑制输入新数据,并在下一个时钟 (CLK) 脉冲将

2025-02-05 17:22:04 928

928

928

928

DAC7565 SYNC这个IO脚在常态应该置为低电平还是高电平?

手册中关于SYNC的描述是:SYNC低电平时使能输入移位寄存器,SYNC需要保持低电平到接收玩24个SCLK周期才能更新DA输出,如果没到24个SCLK周期就变为高电平,输入移位寄存器将复位。

我

2025-02-05 09:31:01

ADS1211 DRDY在上电之后,也就是初始化后,是保持高电平还是低电平?

请问一下,DRDY在上电之后,也就是初始化后,是保持高电平还是低电平?在传送指令结束后,是不是会自动跳为高电平?麻烦用过ADS1211的给说一说,并且在用的过程中要注意的问题给我讲一下,在这里先谢谢大家啦!

2025-02-05 09:26:39

怎样测量TTL电平电压 TTL电平信号的特性分析

。 使用示波器的垂直灵敏度(Volts/Division)和水平时间(Time/Division)旋钮调整显示范围,使得信号稳定地显示在屏幕上。 连接探头 : 将示波器的探头连接到TTL信号输出端,注意探头的地线接示波器的地端,以确保测量的准确性。 测量高电平和低电平 : 在垂直方向上,使用

2025-01-31 10:05:00 2713

2713

2713

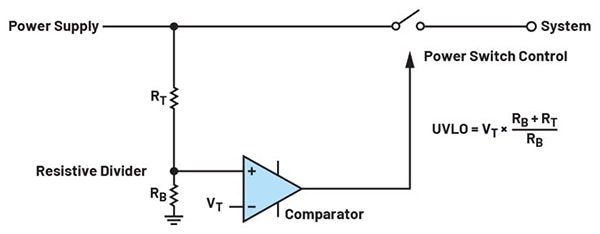

2713用于系统功率循环的高压侧 MOSFET 输入开关选择

活动或系统挂起而失去响应的系统。一种有效且广泛使用的功率循环方法是利用监控电路的低电平有效输出来驱动高压侧 MOSFET 输入开关。 电压监视器或监控电路可为其逻辑电平输出提供两种选择:低电平有效和高电平有效输出信号。这适用于推挽输出拓扑或带有上

2025-01-25 17:26:00 1121

1121

1121

1121

数字电路中常见组件

) AND门 :只有当所有输入都为高电平时,输出才为高电平。 OR门 :只要有一个输入为高电平,输出就为高电平。 NOT门 (反相器):输出是输入的反相。 NAND门 :AND门的反相。 NOR门 :OR门的反相。 XOR门 (异或门):当输入不同(一个高电平,一个低电平

2025-01-24 09:40:33 1643

1643

1643

1643ADS1254上电启动,DOUT/DRDY总是高电平,一直为高电平是怎么回事?

ADS上电,DOUT/DRDY总是高电平,一直为高电平,多插几次电源,偶尔能正常启动DOUT/DRDY有正常的下降沿。

到底是怎么回事?

下面是启动顺序:

InitSPI3SEL();//设置

2025-01-23 07:01:19

ADS1274有DRDY周期信号,DOUT1,2,3,4都是低电平这是什么情况?

SPIdiscrete的,PWDN4为高电平,PWDN1~3都为低电平,实际上就让第四路工作,DRDY的波形图如下,输入经过差分器件OPA1632,当输入为直流信号时,DOUT1~4都为低电平,好奇怪,DRDY信号输出波形显示挺正常的呀,请问这是什么情况?

2025-01-23 06:45:45

adc08d1020的控制线接入xilinx V5电平为3.3V的IO BANK,没有办法换FPGA的IO电平,怎么解决?

adc08d1020的所有控制线(1.9V电平)接入xilinxV5芯片 电平为3.3V的IOBANK,现板子已做好,没有办法换FPGA的IO电平。

控制线有三种:

1)可以直接接高电平(1.9v

2025-01-22 08:20:59

TTL电平与信号降噪技术的区别

TTL电平是一种数字电路中使用的电压标准,它定义了逻辑电平的高低状态。TTL电平的特点是: 电压范围 :TTL电平的高电平(逻辑1)通常在2.4V到5V之间,而低电平(逻辑0)则在0V到0.8V之间

2025-01-16 10:34:04 1133

1133

1133

1133使用TTL电平时的常见问题

问题 问题描述: 在不同TTL电路或TTL与CMOS电路之间进行接口时,可能会出现电平不兼容的问题。 解决方案: 使用电平转换器或逻辑缓冲器来匹配不同逻辑电平。例如,TTL到CMOS的电平转换可以通过专门的芯片来实现,这些芯片可以将TTL的输出电平

2025-01-16 10:31:12 1601

1601

1601

1601TTL电平与高电平信号的转换

和特点 TTL电平是一种数字逻辑电平标准,最初由德州仪器(Texas Instruments)开发。它定义了逻辑“0”(低电平)和逻辑“1”(高电平)的电压范围。在TTL电平中,逻辑“0”通常在0V到0.8V之间,而逻辑“1”在2.0V到5V之间。TTL电平的优点包括简单的设

2025-01-16 10:28:42 1594

1594

1594

1594TTL电平噪声容忍度分析

定了高电平和低电平的具体范围。在计算机处理器控制的设备内部的数据传输中,TTL电平信号是理想的,其电平标准通常如下: 输出高电平(H):大于2.4V,典型值为3.5V(室温下)。 输出低电平(L):小于0.4V,典型值为0.2V(室温下)。 输入高电平(VIH):

2025-01-16 10:26:58 2321

2321

2321

2321TTL电平在嵌入式系统中的应用

晶体管来实现逻辑门的功能。TTL电平因其简单、可靠和成本效益高而在嵌入式系统中得到了广泛的应用。 TTL电平的定义和特性 TTL电平是一种数字信号电平标准,它定义了高电平和低电平的具体电压值。在TTL电平中,一个逻辑“1”(高电平)通常对应于2.4V到5V的电压范围,而一个逻辑“

2025-01-16 10:22:31 1653

1653

1653

1653TTL电平与低电平信号的区别

在数字电子学中,信号的传输和处理依赖于电压水平来表示逻辑状态。TTL电平和低电平信号是两种常见的电压水平,它们在数字电路中扮演着重要的角色。 TTL电平 TTL电平是一种广泛使用的数字逻辑标准,由

2025-01-16 10:21:08 2010

2010

2010

2010TTL电平的传输距离限制

在数字电子领域,TTL电平是一种非常重要的信号标准,它规定了电路中逻辑高和逻辑低的电压范围。TTL电平的稳定性和可靠性使其成为许多电子系统的首选。然而,即使是最稳定的信号,在长距离传输时也会遇到挑战

2025-01-16 10:15:17 1998

1998

1998

1998TTL电平与RS-232接口的联系

挥着重要作用。 TTL电平简介 TTL电平是一种数字电路的电压标准,它基于晶体管-晶体管逻辑(TTL)技术。TTL电平通常使用5V供电,其逻辑“0”(低电平)约为0.8V,逻辑“1”(高电平)约为2.4V。这种电平

2025-01-16 10:13:33 1512

1512

1512

1512TTL电平在数字电路中的作用

电平是一种双极型晶体管逻辑电平,它由两个晶体管构成,一个是输入晶体管,另一个是输出晶体管。TTL电平的标准电压定义如下: 低电平(逻辑0):电压范围在0V到0.8V之间。 高电平(逻辑1):电压范围在2.0V到5V之间。 这些电压范围确保了数字信号的清晰

2025-01-16 09:56:25 3456

3456

3456

3456TTL电平标准的介绍与解析

逐渐成熟,并成为数字电路设计中的一个标准。 TTL电平标准的定义 TTL电平标准定义了数字信号的高低电平电压范围。在TTL电平标准中,高电平(逻辑1)通常定义为2.7V至5V,而低电平(逻辑0)则定义为0V至0.8V。这些电压范围确保了数字信号的清晰区

2025-01-16 09:46:44 3501

3501

3501

3501TTL电平的应用场景和实例

TTL电平作为一种数字电路中的基本逻辑电平标准,广泛应用于各种电子设备和计算机系统中。 一、TTL电平的基本概念 TTL电平是一种数字电路中常用的逻辑电平标准,它基于晶体管-晶体管逻辑

2025-01-16 09:45:17 3859

3859

3859

3859TTL电平与CMOS电平的区别是什么

在数字电子领域,逻辑电路的设计和实现是构建复杂电子系统的基础。TTL和CMOS是两种广泛使用的逻辑电路技术,它们各自有着独特的优势和局限性。 1. 电平标准 TTL电平标准是基于双极型晶体管

2025-01-16 09:43:59 2836

2836

2836

2836ADS1271 PDWN管脚接高电平时,发现RDRY、DOUT管脚均有波形输出,为什么?

我把MODE接高电平 FORMAT接地工作在SPI低功耗模式下。当PDWN管脚接高电平时,发现RDRY、DOUT管脚均有波形输出。

请问:

1、当PDWN管脚为高电平时,ADC转换就启动了;

2

2025-01-15 07:00:21

使用STM32进行ADS1274的数据读取,SCLK一直为低电平,为什么?

我使用STM32进行ADS1274的数据读取

ADS1274的CLK由STM32的通用定时器提供,我使用的频率是72/128Mhz。ADS1274的各个电压均测正常。

CLKDIV接高电平

2025-01-15 06:45:16

使用ADS7815时,数据端口输出比较混乱,即使被采样信号为0,输出端口也会有高电平,为什么?

ADS7815数据输出端口在转换的期间为三态,转换完成后为高电平或低电平,但为什么我使用的时候,数据端口输出比较混乱,即使被采样信号为0,输出端口也会有高电平

2025-01-14 07:58:18

为什么ISO7230M输入高电平时输出确偶发了低电平?

示波器通道1监测输入通道A(input)一直为高电平,高电平时偶尔有干扰,但是示波器通道2监测输出通道A(output)由高电平变为了低电平。而低电平的脉宽在2us~17us不等,请大神们解答

2025-01-13 06:52:06

TLV1544的EOC输出始终是高电平,输入其他端口的信号都是对的,是怎么回事?

TLV1544的EOC输出始终是高电平,输入其他端口的信号都是对的,是怎么回事,是芯片换了吗?这个芯片应该可以用51单片机来控制吧?

2025-01-08 06:28:45

电子发烧友App

电子发烧友App

评论