CC1200低功耗、高性能射频收发器:特性、应用及设计要点解析 在无线通信领域,低功耗、高性能的射频收发器一直是工程师们追求的目标。TI推出的CC1200射频收发器,凭借其出色的性能和丰富的功能,在

2026-01-05 16:50:15 33

33 深入解析SN75176A差分总线收发器:特性、应用与设计要点 在电子工程师的日常工作中,选择合适的总线收发器对于实现高效、稳定的数据通信至关重要。SN75176A差分总线收发器凭借其出色的性能和广泛

2026-01-05 09:50:12 35

35 SNx5HVD1x 3.3-V RS-485 收发器:从特性到应用的深度解析 在电子工程师的日常工作中,选择合适的收发器对于实现可靠的数据通信至关重要。今天,我们就来深入探讨一下 SNx5HVD1x

2025-12-30 16:50:07 399

399 3.3V CAN总线收发器SN65HVD23x:特性、应用与设计要点 在工业、汽车等众多领域,CAN(Controller Area Network)总线凭借其高可靠性、抗干扰能力强等优点,成为

2025-12-30 10:25:07 113

113 8通道半双工M-LVDS线路收发器SN65MLVD080/082的特性与应用 在高速数据传输领域,M-LVDS(多点低压差分信号)标准凭借其高速、低功耗等优势,成为了许多应用的首选。德州仪器(TI

2025-12-30 09:45:12 91

91 探索TJA1042高速CAN收发器:特性、应用与设计要点 在汽车电子领域,CAN(Controller Area Network)总线作为一种可靠的通信协议,被广泛应用于各种车载系统中。而

2025-12-29 15:05:12 104

104 Renesas R9A02G021:32位RISC-V MCU的全方位解析 作为一名电子工程师,在日常的硬件设计开发中,选择合适的微控制器(MCU)至关重要。今天,我们就来深入探讨一下Renesas

2025-12-29 09:50:13 87

87 RISC-V 作为开源、模块化的精简指令集架构,其异常中断机制是保障系统可靠运行、响应外部事件与处理内部错误的核心支撑。

2025-12-28 14:41:01 1067

1067

深入剖析TLK1221千兆以太网收发器:特性、功能与设计要点 在高速数据传输的今天,以太网收发器扮演着至关重要的角色。TI公司的TLK1221千兆以太网收发器凭借其出色的性能和特性,成为了众多工程师

2025-12-27 09:25:05 472

472 探索L9615 CAN总线收发器:特性、参数与应用 在电子工程师的日常设计中,CAN(Controller Area Network)总线收发器是实现可靠通信的关键组件。今天,我们就来深入探讨一款

2025-12-26 16:40:02 104

104 SN65HVD1050A-Q1 CAN 收发器:特性、应用与设计要点 在汽车和工业领域,CAN(Controller Area Network)总线凭借其高可靠性和实时性,成为了设备间通信的主流选择

2025-12-25 16:55:16 296

296 ISO308x隔离式RS - 485收发器:特性、应用与设计要点 引言 在工业自动化、安防系统等众多领域,可靠的数据传输至关重要。RS - 485作为一种常用的串行通信标准,在长距离、多节点通信

2025-12-25 16:55:11 291

291 探索ISOx5隔离型RS-485收发器:特性、应用与设计要点 引言 在工业自动化、安全系统等领域,可靠的数据传输至关重要。RS - 485作为一种常用的通信标准,在长距离、多节点通信

2025-12-25 16:45:19 283

283 探索TJA1042高速CAN收发器:特性、应用与设计要点 在汽车电子领域,高速CAN(Controller Area Network)通信至关重要,它能确保各个电子控制单元(ECU)之间稳定、高效

2025-12-24 16:45:06 160

160 探索P3A1604UK 4位双电源转换收发器:特性、应用与设计要点 在电子设备设计中,电压转换是一个常见且关键的问题。不同的元件和电路可能需要不同的电压来工作,这就需要可靠的电压转换解决方案。NXP

2025-12-24 11:10:22 169

169 TUSB1106-Q1 USB收发器:特性、功能与应用详解 在当今的电子设备中,USB接口的应用无处不在,而USB收发器作为实现USB通信的关键组件,其性能和特性直接影响着设备的通信质量和稳定性

2025-12-24 10:10:02 145

145 SN888C RS-485收发器:特性、应用与设计要点 大家好,作为一名资深电子工程师,今天我要和大家详细介绍一款非常实用的RS - 485收发器——SN888C。它在电子计量表等应用中有着出色

2025-12-23 09:45:06 233

233 和TCAN337G。 文件下载: tcan332g.pdf 一、产品特性 电气特性 单电源3.3V供电 :这一特性使得该系列收发器能够直接与3.3V的CAN控制器或微控制器(MCU)接口,简化了系统设计。同时,它们还能与

2025-12-19 16:10:18 315

315 SN74AVCH8T245PWR低压双向电平转换的8位双电源总线收发器产品型号:SN74AVCH8T245PWR产品品牌:TI/德州仪器产品封装:TSSOP24产品功能:8位双电源总线收发器

2025-12-18 11:15:53 199

199

武汉芯源MCU的指令集架构是什么,有哪些特点?

2025-12-08 06:59:46

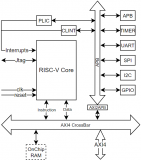

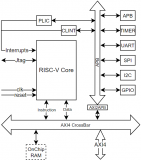

、WUP、IWDG、RTC、无线收发器等丰富的外设。内核采用RISC-V RV32IMAC(2.6 CoreMark/MHz)。

2025-12-01 17:43:10 473

473

的处理性能。

成本效益:Cortex-M处理器提供了高性价比的解决方案,适用于各种规模的嵌入式系统设计。

处理器核心:Cortex-M处理器核心采用深层流水线和精简指令集,旨在提供高性能

2025-11-26 07:22:38

RISC-V(Reduced Instruction Set Computing-V)是一个开源指令集架构(ISA),它的设计目标是提供一个简洁、可扩展且高效的指令集,适用于各种应用场景,从低

2025-11-24 11:36:12 4394

4394

想理解 RISC-V,得先从“指令集架构”说起,这是芯片的“语言”。

2025-11-14 09:44:52 1345

1345

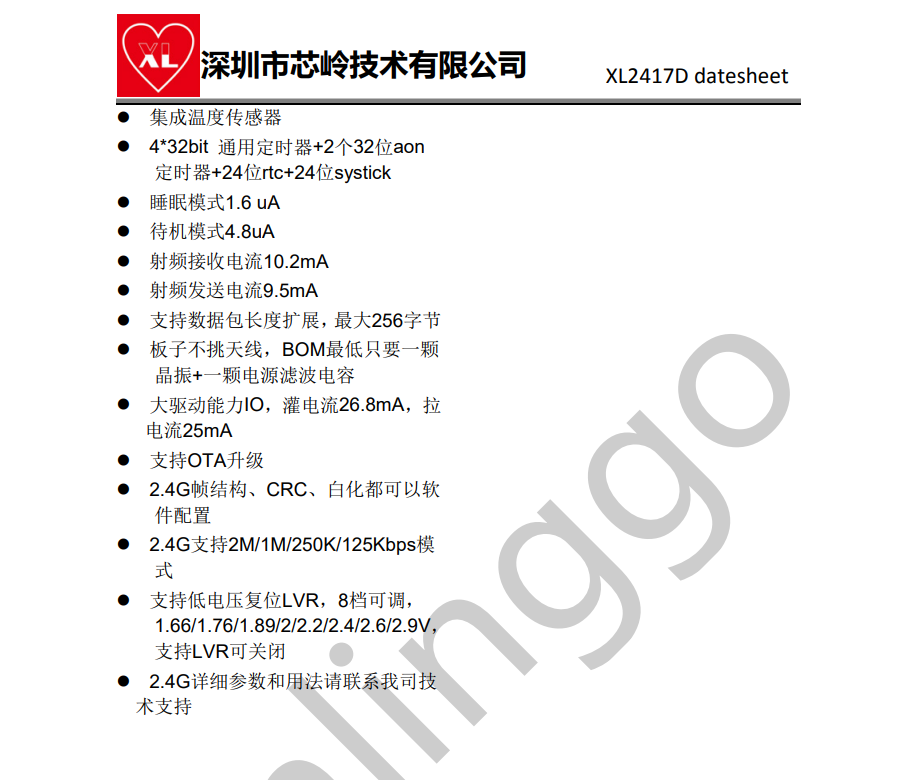

XL2417U 是一款在成本、集成度和性能方面都非常有竞争力的 2.4GHz RF SoC芯片,内置高性能2.4GHz射频收发器,灵敏度高达-96dBm,输出功率最大13dBm,通信稳定可靠。带

2025-11-12 16:57:29

、远程控制器 主要优势: Ci24R02提供配套的调试开发软件和丰富的函数库,能大大降低开发门槛和缩短开发周期。 主要特性 低功耗、Low Pin Count、宽电压工作范围,集成了13/14

2025-11-11 17:32:15 1169

1169

、WUP、IWDG、RTC、无线收发器等丰富的外设。内核采用RISC-V RV32IMAC(2.6 CoreMark/MHz)。 Ci24R02提供配套的调试开发软件和丰富的函数库,能大大降低开发

2025-11-11 14:47:17 172

172

利用定时器中断,率先判断该FIFO的值不为空,并且保证一次读取一个帧长(即10个周期)的数据,能够实现该FIFO内数据即写即读,数据写入不久便能取走的效果。

自定义指令集设计

E203

2025-10-28 08:03:26

了一个20除以6是否等于3的检验操作,以此完成指令集测试,其中gp寄存器寄存的是当前测试的代号,方便于定位当前处于哪个测试。了解完上述信息后,就可以进行通过仿真信号进行指令集测试纠错了。

2.通过仿真

2025-10-24 14:04:08

关于蜂鸟E203的浮点指令集拓展(F拓展)

Whetstone中有很多浮点数运算,而蜂鸟e203中没有硬件支持,是通过将浮点数转化成整型数来计算,效率大大降低。

为了提高Whetstone跑分

2025-10-24 11:51:39

本文为描述在没有开发板的前提下如何在Linux系统进行指令集测试。

在不同的开发板上移植蜂鸟E203软核的过程请参考前文

1.将文件传输进入Linux系统

首先,将解压好的蜂鸟E203文件夹通过

2025-10-24 11:43:16

实现功能

为了完成F拓展,我们计划在ALU内添加一个专用于计算单精度浮点数的FPU单元。

2.1 实现riscv的F指令集拓展

即需要实现26条F指令:

以下部分指令返回地址是给整数寄存器,红色

2025-10-24 07:43:20

3位标识数据位宽,高两位指示数据类型。

指令的类型由vetype的值进行标记,如果将vetype设为00000则会禁用向量寄存器。

对于vector指令集来说,有一些必须要明白的名词需要搞懂

2025-10-23 08:28:49

=17.3333px]二、指令集详细介绍

[size=17.3333px]P扩展包含指令数量较大,可以按照:SIMD数据处理指令、部分SIMD数据处理指令、64位数据计算指令及非SIMD指令进行分类。其中具体包括8位

2025-10-23 07:40:10

两个4位操作数相乘的结果。但是对于RISC-V架构的CPU来说,它所有的通用寄存器都是32位的,如果我们要进行两个32位操作数的乘法操作,那该如何保存这个操作的结果呢?RISC-V对于乘除法相关的指令

2025-10-23 06:52:35

RISC-V K扩展指的是RISC-V用于提升密码学算法的速度、减小应用程序大小的一个扩展指令集。主要包含了:AES加密算法的加速指令、SHA算法的加速指令,SM3、SM4算法的加速指令以及从B扩展

2025-10-23 06:12:39

本文主要讲解RISC-V指令集手册中F指令部分

RISC-V标准中采用了符合IEEE 754-2008算术标准的单精度浮点计算指令,对于浮点运算来说,RV32F指令扩展中增加了32个32位的浮点

2025-10-22 08:18:20

一、B扩展简介

B扩展,即bit-manipulation (bitmanip) extension,主打增强位操作的指令集。B扩展定义了RV32-64下的位操作指令。为了更精准地在领域

2025-10-22 08:11:43

RVF单精度浮点指令集扩展

RVF扩展了26条浮点指令。

浮点乘加指令

浮点比较、最大最小值、转移、符号注入、分类指令

浮点除、开方指令

浮点转换指令

2025-10-22 07:26:26

RVF单精度浮点指令集寄存器扩展

RVF扩展了32个独立的浮点通用寄存器,其中0号寄存器可变。

RVF扩展了1个fcsr寄存器,存放了异常标志和动态舍入模式。

RVF扩展必须对misa csr寄存器进行一定的修改。

2025-10-22 06:04:45

性能:内存的读写速度、延迟和带宽等都会影响到 Drystone 的性能。

指令集优化:对RISC-V指令集的优化也会影响性能。例如,对于特定的应用或计算任务,可以通过定制指令集来提高性能。

编译器优化

2025-10-21 13:58:40

B扩展简介

RISCV B扩展指的是RISCV用于位运算加速的一个扩展指令集,目的是使用一条指令实现原本需要2-3条指令才能实现的位操作指令。具体包含内容如下:

B扩展就是RISC-V一个可选

2025-10-21 13:01:45

;SIMD指令扩展,SIMD指令可以在单个指令中执行多个相同或类似的操作,可以提高处理器的运算速度,通过添加SIMD指令,可以提高处理器的计算能力。

2. 指令集P扩展的主要代码

//添加AES加密指令

2025-10-21 10:50:02

蜂鸟E203是一款基于RISC-V架构的微处理器,其指令集包含RV32I的基本指令集,RV32M的乘法扩展指令集,以及一些常用的定点指令和控制指令。如果需要扩展其指令集,可以考虑使用RISC-V的可

2025-10-21 09:38:47

1.队伍介绍

报名编号:CICC1137

团队名称:大衍

团队成员:王星距、郭柏炀、赵健棚

这是我们第一篇分享文章

2.E203的NICE接口

RISC-V ISA在32位指令中预定义了4组

2025-10-20 09:23:24

为推动RISC-V技术的创新和应用,中国电子学会联合国内优势单位,聚焦基于第五代精简指令集计算原理建立的开放指令集架构(RISC-V),在全国范围组织发起了以“启芯征程,创芯时代”为主题的CIE全国

2025-09-16 08:07:41 725

725

高精度 ADC、RTC、PWM 等功能,抗干扰能力强,适用于滑条遥控器、智能门锁、消费类电子产品等电子应用领域。2. 主要特性◼ CPU- CPU: 1T 8051 内核,指令兼容 MCS-51 指令集- 程序存储器 FLASH COD_ROM:16K*8bit,可

2025-09-15 16:42:30 0

0 CMT2392F512集成了32位ARM CortexTM-M4F内核和一颗超低功耗射频收发器,是一款高性能、超低功耗、适用于113至960 MHz无线应用的OOK,(G)FSK 和4(G)FSK

2025-09-11 15:22:19 0

0 的支持。 AT32UC3B0128是一款基于AVR32 UC精简指令集处理器的完整片上系统微控制器,其运行频率最高可达60MHz。AVR32 UC是一款高性能32位精简指令集处理器内核,专为对成本敏感的嵌入式应用而设计,尤其注重低功耗、高代码密度和高性能。该处理器配备了存储器保护单

2025-08-27 18:03:14 764

764

自8月12日成都华微公告发布全新32位RISC-V超低功耗MCU 后,现首次在elexcon深圳国际电子展上亮相该产品。 产品核心特点 超低功耗设计 -大幅延长电池续航时间 高性能32位

2025-08-26 09:28:02 1278

1278

在嵌入式控制领域,一款性能稳定、适配性强的单片机是设备高效运行的核心。FT60E11X 作为精简指令集的 I/O 型 8 位单片机,凭借丰富特性,成为照明控制、安防系统等多领域的理想选择,下面捷尚微

2025-08-25 14:32:19 532

532

2.4GHz射频收发器、丰富的基带功能、32位MCU和各种外围IO。它支持128KB的flash和8KB的RAM,以实现可编程协议和配置文件,支持定制应用程序。 XL2417D采用先进的55nm CMOS

2025-08-22 13:56:24 651

651

精简指令集(RISC)

与复杂指令集(CISC,如 x86 架构)相比,ARM 指令集更简洁,指令长度固定(多为 32 位),执行效率更高,适合低功耗场景。

低功耗与高性能平衡

设计注重能效比,在

2025-08-18 13:31:16

-V是一种开放(Open)指令集架构(ISA)标准。本报告探讨了RISC-V指令集架构标准区别于其它主流ISA的不同特点,以及这些特点对于国产微处理器芯片(CPU)的重

2025-07-29 17:02:45 1142

1142

以下是关于RISC-V的详细介绍,结合其核心技术特点与当前发展现状:核心概念RISC-V(第五代精简指令集)是一种基于精简指令集(RISC)的开源指令集架构(ISA),由加州大学伯克利分校于2010

2025-07-28 16:27:35 11

11 首先认识什么是ARM?

ARM公司简介

ARM是Advanced RISC Machines的缩写,它是一家微处理器行业的知名企业,该企业设计了大量高性能、廉价、耗能低的RISC (精简指令集

2025-07-23 10:21:48

2025年7月16日,在上海2025RISC-V中国峰会期间,由中移芯昇主办,隼瞻科技协办的峰会同期活动:RISC-DSP指令集研讨会暨VDSPIP发布会成功举办。此次会议得到了业界的广泛关注,也

2025-07-17 19:11:14 992

992

当前,按指令集架构(ISA)分类,主流架构包括 x86 架构、ARM 架构和 RISC-V 架构。作为开源精简指令集(RISC),RISC-V 的主要特点有模块化设计,开发者可自由扩展指令集;灵活性

2025-07-17 11:26:18 1423

1423 ARM 架构与 RISC-V 架构的 MCU 在同一性能水平下的运行速度对比,需从架构设计原点、指令集特性及实际测试数据展开剖析。以 ARM Cortex-M33 这类 ARMv8M 架构核心与采用

2025-07-02 10:29:33 1276

1276

在CAN总线通信中,CAN收发器(Transceiver)扮演着至关重要的角色——它就像一位“翻译官”,负责将微控制器(MCU)的数字信号转换为总线上的差分信号,同时把总线信号翻译回MCU能理解

2025-06-27 11:34:20 1905

1905

与RISC-VARM是一种精简指令集(RISC),以该指令集为基础的处理器通常被称为ARM芯片,它在全球范围内得到了极为广泛的应用。而RISC-V也是精简指令集,是美国加

2025-06-24 11:38:35 1824

1824

RV32IMBC指令集和自扩展指令 128KB SRAM,512KB Flash,支持ICP、ISP和IAP,支持OTA无线升级 内置2.4GHz RF收发器和基带及链路控制,支持BLE5.4 支持2Mb

2025-06-05 16:28:02 1683

1683

、WUP、IWDG、RTC、无线收发器等丰富的外设。内核采用RISC-V RV32IMAC(2.6 CoreMark/MHz)。

主要特性

主要特点

内置RISC-V RV32IMAC内核(2.6

2025-06-01 18:41:12

-V处理器,凭借其卓越的性能和创新的设计理念,为工业控制、物联网和消费电子等领域提供了全新的解决方案。HPM5E31IGN采用精简指令集(RISC)设计,指令集架构完全开源,避免了传统ARM架构的授权费用

2025-05-29 09:23:16

在CAN总线系统的设计中,物理层的延迟主要来源于收发器,它影响到系统的性能以及系统响应能力,过大的延迟会导致系统无法应用较高的波特率、总线位错误频发、通信时序异常等,通过在线测量和评估CAN收发器

2025-05-28 11:39:21 921

921

自由使用、修改底层指令集,降低芯片设计成本并加速定制化开发。 灵活扩展:支持基础指令集(如RV32I/RV64I)与可选扩展模块(如浮点运算、向量加速)的组合,开发者可根据低功耗需求裁剪冗余功能。 二、模块化与精简设计 核心指令精简:基于R

2025-04-23 10:01:05 1170

1170 RISC-V是基于精简指令集计算(RISC)原理建立的开源指令集架构,而RISC-VDSP则是在此基础上,专为数字信号处理设计的芯片。它具备开源、灵活可定制等特性,为众多领域的创新应用注入活力

2025-04-18 09:09:46 1803

1803

4 位微控制器,具备 4 信道语音 / Tone/Midi 合成功能,采用高音质 ADPCM 算法,最高采样率达 44.1kHz,有 16 阶音量控制,提供 PWM 和 DAC 两种输出方式,使用 RISC 精简指令集架构,多数指令 1 个时序完成,内置精准内阻震荡,也可外接震荡电阻,支持待

2025-04-03 11:18:26 1

1 AP8000所支持。 GD32F150C6T属于兆易创新GD32微控制器(MCU)家族的超值型产品线。它是一款基于高性能Arm® Cortex®-M3精简指令集计算机(RISC)内核的32位通用

2025-04-03 10:57:31 717

717

鹭岛论坛开源芯片系列讲座第27期「RISC-VAI指令集的标准化与开源实现」明晚(26日)21:00精彩开播期待与您云相聚,共襄学术盛宴!|直播信息报告题目RISC-VAI指令集的标准化与开源实现

2025-03-25 08:12:45 676

676

64位乱序4发射超标量微架构,支持RV64GCBHX指令集,其中X为自研高性能扩展指令集,同时支持虚拟化RVH 1.0指令扩展。 U

2025-03-21 00:04:00 2404

2404 ,具有高性能精简指令集、低工作电压、低功耗特性且完全集成触控按键功能。为各种触控按键的应用,提供了一种简单而又有效的实现方法。广泛应用于触摸台灯、小家电、消费类电子产品等电子应用领域。 基于 RISC 的架构绝大部分指令都只需一个指令执行周期,少部分需要两个

2025-03-17 17:53:16 0

0 1. 产品概述 PT8P2104 是一款 RISC 内核, 触摸 IO 型 8 位 MCU,其内置 1K*14bit OTP ROM、72*8bitSRAM、TOUCH、TIMER、PWM

2025-03-17 17:52:08 0

0 高性能精简指令集、低工作电压、低功耗特性且完全集成触控按键功能。为各种触控按键的应用,提供了一种简单而又有效的实现方法。广泛应用于触摸台灯、小家电、消费类电子产品等电子应用领域。 基于 RISC 的架构绝大部分指令都只需一个指令执行周期

2025-03-17 17:39:48 0

0 PT8P1101 是一款 RISC 内核, IO 型 8 位 MCU,其内置 1K*14bit OTP ROM、48*8bitSRAM、TIMER、PWM、LVD 等功能。主要应用于应用消费类

2025-03-17 17:23:28 0

0 鹭岛论坛开源芯片系列讲座第27期「RISC-VAI指令集的标准化与开源实现」3月26日(周三)21:00精彩开播期待与您云相聚,共襄学术盛宴!|直播信息报告题目RISC-VAI指令集的标准化与开源

2025-03-10 17:55:01 1207

1207

包含2.4G射频收发器、蓝牙接收发送器等,通过点对点的传输实现通讯,芯片包含PWM、ADC、UART、SPI、I2C等模块,广泛应用于灯控、智能家电等设备。

无线连接系列产品分类:> 蓝牙+

> 2.4G+

原厂代理 电话:19928739245(微同)欢迎咨询

2025-03-10 09:14:06

与安全性的MCU产品。然而,在汽车电子、工业控制等高可靠性场景中,国产芯片仍需突破功能安全认证、复杂环境适应性等技术壁垒。 AS32X601是国科安芯研制的一款32位RISC-V指令集MCU,采用双核锁步架构,主频高达180MHz,支持ASIL-B功能安全等级(符合ISO262

2025-03-08 18:40:13 1324

1324

一、RISC-V架构:实现芯片自主可控 国科安芯MCU芯片采用开放、灵活的RISC-V指令集架构,RISC-V的开源特性不仅大幅降低研发成本,更赋予芯片设计高度定制化能力。例如,国科安芯

2025-02-23 09:31:55 1331

1331 RISC-V 是一种基于精简指令集(RISC)原则的开源指令集架构(ISA),其开放性和灵活性使其在嵌入式系统和计算应用中得到了广泛应用。在 FPGA 上实现 RISC-V 处理器,可以充分利用 FPGA 的可编程性和高性能特点,构建定制化的微处理器设计。

2025-02-21 15:51:24 1490

1490

电子发烧友网站提供《74ALVCH16952 16位寄存器收发器规格书.pdf》资料免费下载

2025-02-19 16:39:24 0

0 电子发烧友网站提供《74ALVCH16600 18位通用总线收发器规格书.pdf》资料免费下载

2025-02-19 15:50:50 0

0 电子发烧友网站提供《74ALVCH16646 16位总线收发器/寄存器规格书.pdf》资料免费下载

2025-02-19 15:44:51 0

0 电子发烧友网站提供《74ALVCH16601 18位通用总线收发器规格书.pdf》资料免费下载

2025-02-19 15:39:24 0

0 电子发烧友网站提供《74AVC8T245-Q100具有可配置电压转换的8位双电源转换收发器规格书.pdf》资料免费下载

2025-02-18 17:53:55 0

0 电子发烧友网站提供《74AVC8T245具有可配置电压转换的8位双电源转换收发器规格书.pdf》资料免费下载

2025-02-18 17:52:17 0

0 电子发烧友网站提供《74AVCH8T245 8位双电源转换收发器规格书.pdf》资料免费下载

2025-02-18 16:52:24 0

0 高性能RISC-V内核32位MCU-AiP32RV15A8/AiP32RV1564

2025-02-12 11:48:23 1202

1202

处理器行业。RISC-V在半导体行业有何不同?RISC-V(精简指令集计算–V)在几个关键方面与其他指令集(如x86、ARM和MIPS)不同。以下是一些主要区别:开

2025-02-05 17:03:08 9

9

在工业自动化和通信领域,光纤收发器和IO-Link收发器都是关键的通信组件,它们在数据传输、网络扩展和设备连接方面发挥着重要作用。然而,两者在设计、功能、应用场景以及技术特性上存在显著差异。本文将

2025-02-02 15:44:00 995

995 本文将深入探讨无线收发器产生杂音的原因,并提供相应的解决方法。

2025-01-29 15:35:00 4005

4005 无线收发器作为现代通信技术的重要组成部分,广泛应用于各个领域,包括无线通信、物联网、远程控制和无线传感器网络等。本文将深入探讨无线收发器的工作原理,同时提供详细的使用方法。

2025-01-29 15:31:00 2746

2746 和模块化设计成为其显著优势。物联网设备通常需要长时间运行,且对体积和功耗有严格要求。RISC-V芯片通过精简指令集和优化设计,实现了低功耗的同时保持了高性能,非常适合用于传感器节点、智能家居控制器

2025-01-29 08:38:00

此前,2025年1月7日下午,一场聚焦RISC-V指令集架构未来发展的高端交流会议在雄安新区成功举办。本次交流由中国开放指令生态(RISC-V)联盟产业孵化组的多位核心成员与雄安新区的领导及代表共聚一堂,围绕RISC-V在雄安新区的发展蓝图与合作机遇展开了深入探讨。

2025-01-24 11:22:50 1507

1507 英集芯IP5911是一款集成锂电池充电管理、咪头检测唤醒、负载电阻插拔和阻值检测等功能的低功耗8位MCU芯片,以下是关于该芯片的详细介绍: 一、基本属性品牌:INJOINIC(英集芯

2025-01-20 15:14:37

嘿,咱来聊聊RISC-V MCU技术哈。

这RISC-V MCU技术呢,简单来说就是基于一个叫RISC-V的指令集架构做出的微控制器技术。RISC-V这个啊,2010年的时候,是加州大学伯克利分校

2025-01-19 11:50:11

需少量外围器件即可构建完整的充电与控制系统,简化了电路设计,缩小了方案尺寸,降低了生产成本。强大的MCU内核内置兼容8051指令集的8位MCU,主频最高可达16M

2025-01-18 12:05:42

、TIMER、WUP、IWDG、RTC、无线收发器、3D 低频唤醒接收器等丰富的外设。

内核采用 RISC-V RV32IMAC(2.6 CoreMark/MHz)。原厂提供了配套的调试开发软件和丰

2025-01-16 15:53:33

一、总体概述K1 系列是基于 RISC - V 开源指令集打造的 AI CPU,致力于构建更通用、高能效的 AI 处理器平台,推动全球开源、开放的 AI 算力生态建设。主要应用于单板计算机、网络存储

2025-01-06 17:37:36

电子发烧友App

电子发烧友App

评论