凯芯Cascade 64Mbit pSRAM CSL6408SB-A4为医疗手环提供高密度低功耗存储方案,支持200MHz高速数据缓存,待机电流低至1.8μA。其工业级温度范围与ECC纠错能力保障生命体征数据可靠存储,助力设备实现长效续航与临床级监测精度。

2025-12-09 09:21:00 357

357

工业数据中台完全支持接入MySQL数据库 ,且通过数据同步、集成与治理等技术手段,能够充分发挥MySQL在数据存储与事务处理方面的优势,同时弥补其在数据分析与共享能力上的不足,具体分析如下: 技术

2025-12-04 11:23:34 287

287

使用DMA将数据从FLASH传输到SRAM

下载示例

演示AT32F系列使用DMA将数据从FLASH传输到SRAM的使用方法。

注:本例程对应的代码是基于雅特力提供的V2.x.x 板级支持包

2025-12-03 16:26:37

严苛的场景。MD6639若需替代TI或ADI的同类电源管理芯片,需根据具体参数和应用场景筛选,ADI的LTM46xx系列(如LTM4661)在高频、高集成度场景中更具优势,而TI的TPS54xxx系列

2025-12-02 09:19:08

在各类电子设备与嵌入式系统中,存储器的性能与功耗表现直接影响着整体设计的稳定与效率。低功耗SRAM,特别是异步SRAM系列,凭借其出色的能效比与高可靠性,正成为越来越多工业控制、通信设备及便携终端中的关键部件。

2025-11-25 15:42:56 271

271

通过标准I/O操作磁盘文件时,为了减少系统调用的次数,标准I/O函数会将用户读取或写入文件的数据缓存在stdio缓冲区,然后再一次性将stdio缓冲区中缓存的数据通过调用系统调用系统I/O写入到系统I

2025-11-19 16:24:10

、英尚微电子代理的高性能PSRAM芯片——EMI164LA16LM-70I,是一款专为现代智能设备设计的高性能存储解决方案,在市场应用中得到了良好的反馈。

2025-11-18 17:24:35 255

255 DRAM利用电容存储数据,由于电容存在漏电现象,必须通过周期性刷新来维持数据。此外,DRAM采用行列地址复用设计,提高了存储密度,但增加了控制复杂性。它广泛用于大容量、低成本存储场景,如计算机内存。

2025-11-18 11:49:00 477

477 在现代高性能电子系统中,存储器的读写速度往往是影响整体性能的关键因素之一。同步SRAM(Synchronous Static Random Access Memory)正是在这一需求下发展起来的重要

2025-11-18 11:13:01 242

242 和size参数,可以分别指定两个参数为NULL和0。标准错误stderr默认属于这一种类型,从而保证错误信息能够立即输出。

⚫ _IOLBF:采用行缓冲I/O。当在输出或输入中遇到换行符\"

2025-11-14 09:02:30

在处理器性能持续攀升的今天,存储系统的速度已成为制约整体算力的关键瓶颈之一。作为最接近CPU核心的存储单元,SRAM(静态随机存取存储器)承担着高速缓存的重要角色,其性能直接影响数据处理效率。当前

2025-11-12 13:58:08 455

455 PSRAM(伪静态随机存储器)是一种兼具SRAM接口协议与DRAM内核架构的特殊存储器。它既保留了SRAM无需复杂刷新控制的易用特性,又继承了DRAM的高密度低成本优势。这种独特的设计使PSRAM在嵌入式系统和移动设备领域获得了广泛应用。

2025-11-11 11:39:04 497

497 型的调试工具来实时监控内存使用情况。

是否有其他方法(例如构建报告、SDK 功能或EZ-USB™ Suite 内的工具)可以让我检查固件使用了多少 SRAM?

2025-11-11 06:33:59

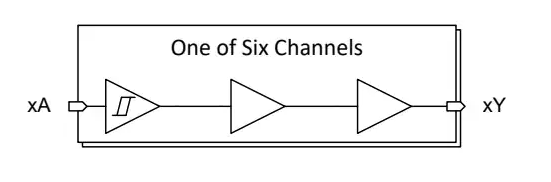

景中实现对德州仪器(TI)和安世半导体(Nexperia)等品牌的有效替代。长晶代理商南山电子将基于长晶科技目前量产的缓冲器产品,详细介绍其型号、性能参数、封装形

2025-11-07 17:18:33 728

728

电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4 在有些情况下,我们想要把代码放到SDRAM运行。下面介绍在APM32的MCU中,如何把代码重定位到SDRAM运行。对于不同APM32系列的MCU,方法都是一样的。

2025-11-04 09:14:18 4981

4981

时钟缓冲器广泛应用于各种电子系统中,以下是一些典型的应用场景:1.通信设备:在高速通信设备中,时钟信号的质量直接影响数据传输的准确性。时钟缓冲器通过优化信号完整性,确保通信系统的稳定性和可靠性。2.

2025-10-30 14:12:01 290

290

OV7725 输出时序中,只有当 HREF 为高电平时,PCLK 驱动下 D[0:7]线表示的才是有效像素数据,因此,利用 HREF 控制 FIFO 的 WE 可以确保只有有效数据才被写入到 FIFO

2025-10-29 23:11:06

凯芯CascadeTeq CSS6404SU-L是一款64Mb QSPI pSRAM,采用串行接口实现高带宽数据传输,工作电压2.7-3.6V,时钟频率达133MHz。适用于物联网、便携设备和工业控制等需要高速缓存的嵌入式场景。

2025-10-28 09:25:00 332

332

PSRAM全称为pseudo SRAM,一般叫伪静态SRAM,串行PSRAM具有类似SRAM的接口协议,给出地址,读、写命令,就可以实现存取,不同于DRAM需要用到memory controller来控制内存单元定期数据刷新

2025-10-27 16:04:47 450

450 非挥发性存储器,如NAND、NOR Flash,数据在掉电后不会丢失。这类存储器通常速度比较慢,可以做资料和大数据存储。

2025-10-27 15:14:39 310

310 在存储解决方案中,外置SRAM通常配备并行接口。尽管并口SRAM在数据传输率方面表现卓越,但其原有的局限性也日益凸显。最明显的挑战在于物理尺寸:不论是占用的电路板空间或是所需的引脚数量,并行接口都

2025-10-26 17:25:18 835

835 QSPI PSRAM是一种集成了QSPI接口与PSRAM存储功能的高效芯片。QSPI(四线串行外设接口)是一种高速串行通信接口,用于连接外部设备;而PSRAM(伪静态随机存储器)则结合了快速随机访问与动态存储的特性。

2025-10-23 15:40:17 379

379 PSRAM之所以被称为"伪静态"存储器,主要是因为其采用类SRAM的接口协议:只需要提供地址和读写命令就可以实现数据存取,无需像传统DRAM一样需要内存控制器定期刷新数据单元。

2025-10-23 14:29:00 296

296 、建立读写操作、配置地址计数器、模拟数据流、综合与仿真以及下载到FPGA进行硬件测试。通过实践,掌握SRAM在FPGA中的使用和基本读写方法,加深对FPGA工作原理的理解。

2025-10-22 17:21:38 4118

4118

爱普科技256Mb PSRAM(如APS256XXN-OBR-BG)为WiSUN无线模块提供高速数据缓存与临时存储解决方案,其166MHz速率、1.8V低功耗及小尺寸封装显著提升模块在智能电网、工业自动化中的多任务处理能力和稳定性。

2025-10-14 09:25:00 265

265

keil+Env怎么把很大的数组定义到SDRAM中?

RTT自带的SDRAM程序运行正常,能够申请里面的空间。

但是没有办法把很大的数组——ltdc_lcd_framebuf[1280][800]

定义到SDRAM中,一运行就出错,请问各位大佬怎么解决啊?

2025-10-11 16:10:01

。CDCDB400是一款DB800ZL衍生缓冲器,符合或超过DB800ZL中的系统参数规格。该器件还符合或超过了DB2000Q规格中的参数。Texas Instruments CDCDB400采用5mm × 5mm 32引脚VQFN封装。

2025-10-06 15:28:00 1218

1218

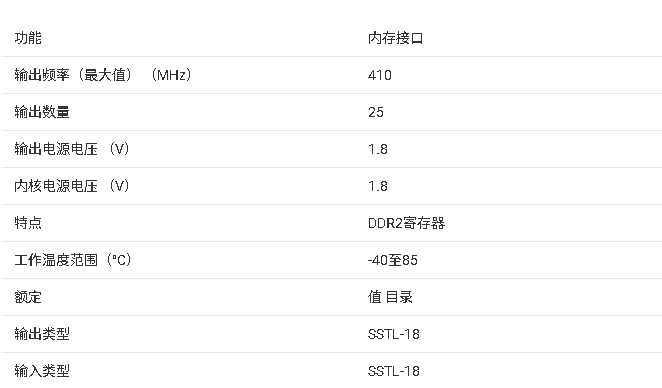

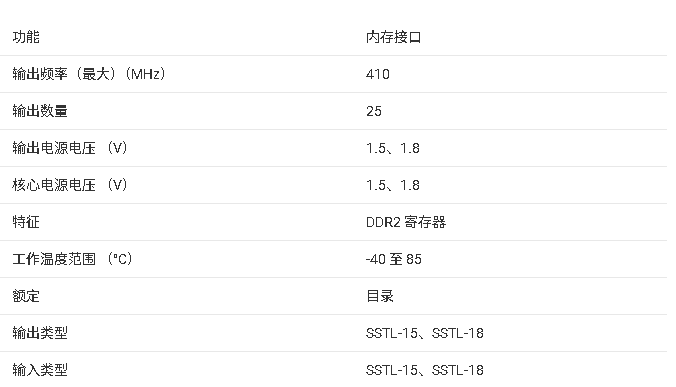

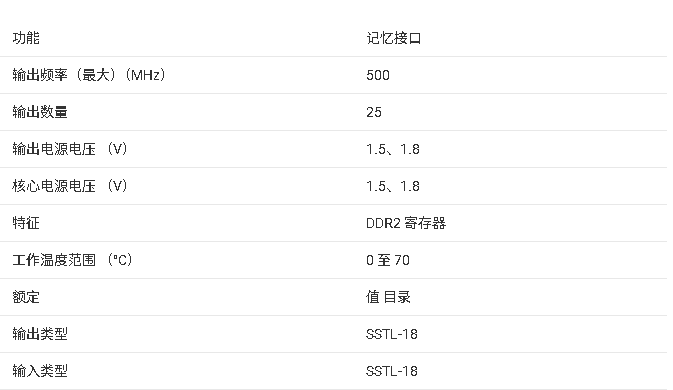

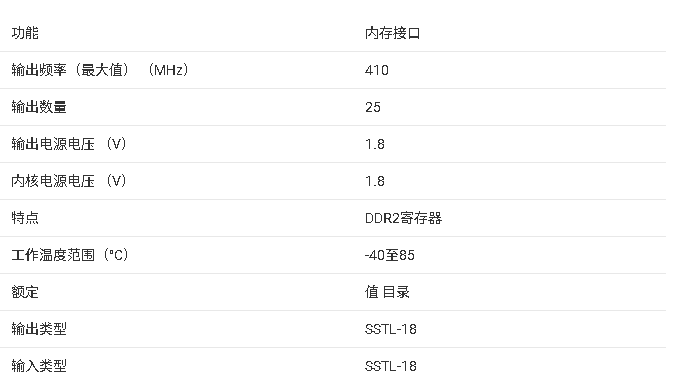

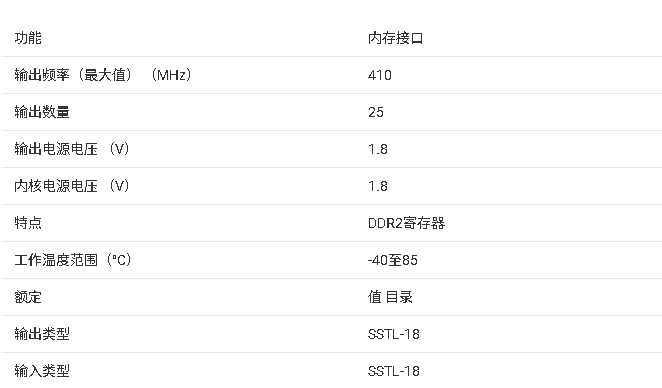

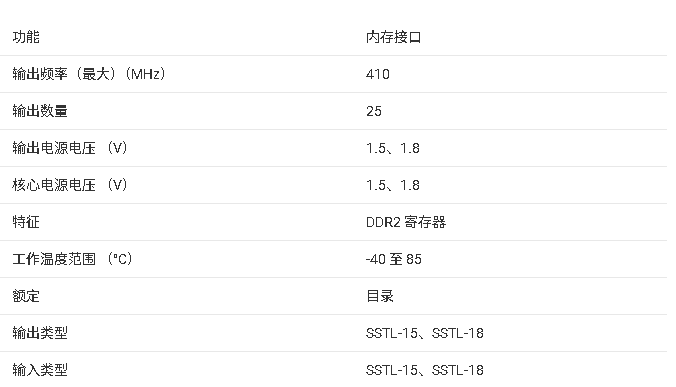

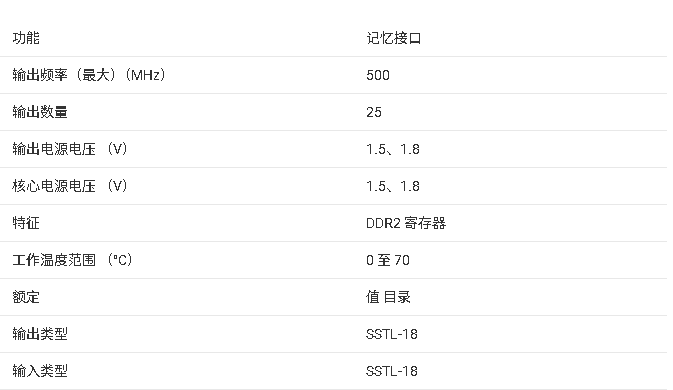

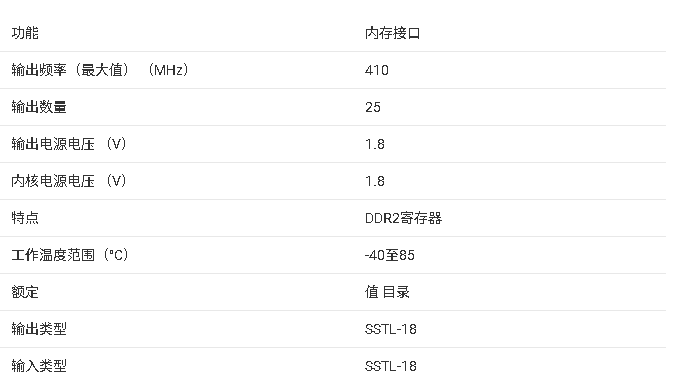

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V VCC 工作。在 1:1引脚配置,每个DIMM只需要一个器件即可驱动9个SDRAM负载。在 1:2 引脚排列中 配置中,每个 DIMM 需要两个设备来驱动 18 个 SDRAM 负载。

2025-09-18 16:52:01 801

801

裸机以及RTT初始化是可以正常读写的,但在线程中,用了rt_thread_mdelay,SDRAM内的数据会被清理,数据丢失,也无法读写了,调试发现是rt_schedule导致的,请问这个该问题如何解决?

2025-09-18 07:53:44

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.425V 至 1.9V VCC 工作。在 1:1 引脚配置中,每个 DIMM 只需要一个器件即可驱动 9 个 SDRAM 负载。在 1:2 引脚配置中,每个 DIMM 需要两个器件来驱动 18 个 SDRAM 负载。

2025-09-17 14:19:28 577

577

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V V~CC~操作。在 1:1 引脚配置中,每个 DIMM 只需要一个器件即可驱动 9 个 SDRAM

2025-09-12 09:35:37 570

570

这款 25 位 1:1 或 14 位 1:2 可配置寄存器缓冲器设计用于 1.7V 至 1.9V VCC 工作。在 1:1 引脚配置中,每个 DIMM 只需要一个器件即可驱动 9 个 SDRAM

2025-09-12 09:31:36 711

711

在此前的文章《SRAM PUF:为每颗芯片注入“不可复制的物理指纹”,守护芯片安全》中,我们探讨了基于SRAM的物理不可克隆功能(PUF)的基本原理,并介绍了SRAM PUF作为一种安全可靠、经济

2025-09-05 10:46:16 1152

1152 在电子系统设计中,时钟信号的稳定与可靠性对于整个系统的正常运行至关重要。为了确保时钟信号在传输过程中不会受到干扰或延迟,工程师们通常会使用一种名为“时钟缓冲器”的装置。本文将探讨时钟缓冲器的应用条件

2025-09-04 15:01:45 673

673

是否可以对 EBI 进行 DMA?我有从 USB 到 SDRAM 的 DMA 工作,但是当我将 DMA 目标地址更改为 EBI(60000000 美元)时,我没有收到任何外部总线活动。如果我将 DMA 到 SDRAM 中的临时缓冲区,然后将 CPU 复制到 EBI,它会按预期工作。

2025-08-29 07:05:06

CBB81电容属于高压谐振薄膜电容器,主要用于高压、高频、大电流电路中,事实上,有很多电容器的作用和CBB81电容是一样的,可以互相替代,cbb81电容用什么可以代替?

2025-08-26 14:23:46 1031

1031 PY32F003 是普冉半导体推出的一款高性价比国产32位微控制器,PY32F003是一款高性价比的国产替代方案,可以用来替换一些进口MCU。芯片采用32 位 ARM® Cortex®-M0+内核

2025-08-21 11:50:09

两个总线能不能同时使用,用了华邦的SDRAM发现SDRAM数据高概率读写错误,但是用ISSI的没问题。如果不对外部SRAM读写就正常。

2025-08-12 06:56:57

凯芯CSS12804SU-O 128Mbit pSRAM以2.1Gbps带宽、1.8μA待机、3×3mm封装重塑穿戴存储:实时缓存健康数据,支撑AR与边缘AI,工业级耐宽温,国产化30%成本优势,续航延长30%,零重构兼容主流平台。

2025-08-04 10:00:00 551

551

与软件问题

链路层错误检测与修复

场景:PCIe链路因信号完整性问题(如插损、串扰)导致误码率(BER)升高,引发链路训练失败或数据重传。

作用:

捕获DLLP包中的ACK/NAK字段,统计重传率

2025-07-29 15:02:27

打算先判断 USB IN 是否存在数据,再执行后续获取数据的步骤,但一旦调用 USBDevice->BulkInEndPt->XferData,就无法再次获取数据。是否有其他 USB API 可以实现我的这一功能?#CYUSB3KIT-003

2025-07-28 06:52:41

:

1.哪个函数可以读取USB端口缓冲区数据的实际字节数?

2. 哪个函数可以读取 GPIF II 上 DMA 缓冲区数据的实际字节数?

3、GPIF II 接口的标志信号会受 USB 端口状态的影响吗?会怎样,然后又会产生怎样的影响?

2025-07-21 07:27:08

RISC-V 作为一种开源指令集架构,凭借其灵活性、可扩展性和开源特性,在数据中心领域的应用正从探索阶段逐步向实际落地推进。目前,RISC-V 在数据中心的应用处于 “能跑通但需优化” 的阶段。从

2025-07-18 13:38:15 5192

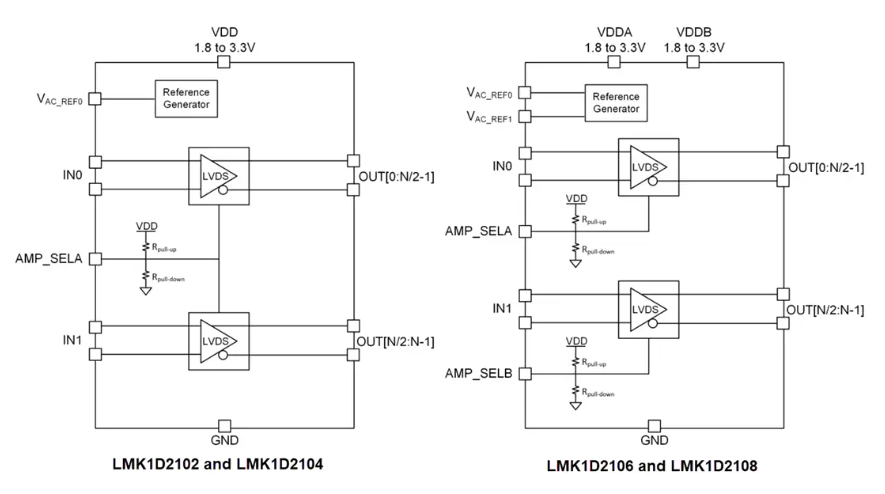

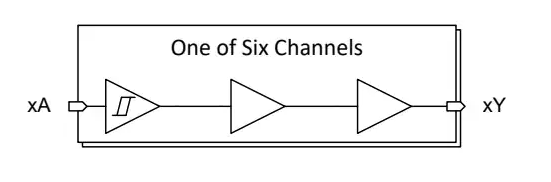

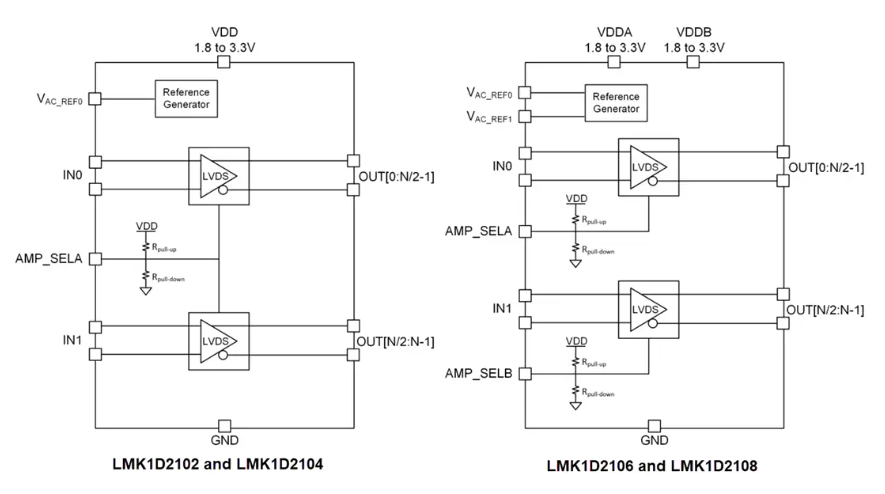

5192 (LMK1D2106L) 或八个 (LMK1D2108L) LVDS输出。输入可以是LVDS、LVPECL、HCSL、CML或LVCMOS。LMK1D210xL专门设计用于驱动50Ω 传输线。在单端模式下驱动输入时,向未使用的负输入引脚施加适当的偏置电压。

2025-07-17 11:17:27 586

586

在使用USB软件获取数据是,下位机给我发送了13个32位数据到USB IN缓冲区,为什么我调用API函数想要第一次取1个32位数据,取完之后再取12位数据,程序会卡死。

2025-07-16 08:12:04

AEC-Q100认证。这些缓冲器用于开关去抖、启用或禁用数字信号、消除缓慢或嘈杂的输入信号以及在复位期间保持控制器。

2025-07-15 10:00:42 635

635

一般我们开发MCU自带的SRAM,对一般应用来说,已经够用了,但是对于内存需求较高的场合,比如跑GUI或者算法等,自带的内存会就不够用,这个时候就要外扩SRAM或SDRAM。

2025-07-15 09:33:09 1781

1781

客户要求Flash driver不能存储在Flash中,需要在升级的时候,由CAN FBL发送到SRAM中,再运行SRAM中的Flash driver

我应该如何实现这个要求?如何能把Flash driver分离成一个单独的部分,再由CAN FBL加载到SRAM中?你们有相关的文档和示例程序吗?

2025-07-15 07:22:16

近日,紫光国芯自主研发的PSRAM(低功耗伪静态随机存储器)芯片系列产品正式发布,并同步上线天猫官方旗舰店。此次上新的PSRAM产品兼容业界主流接口协议Xccela,容量覆盖32Mb,64Mb

2025-07-01 16:42:50 1443

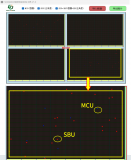

1443 近期受晶圆厂委托, 季丰在执行完SRAM芯片在中子辐射下SER测试后, 通过对SRAM芯片的深入研究,对测试失效数据的分析,将逻辑失效地址成功转换为物理坐标地址,最终在图像上显示失效位置,帮助客户直观地看到失效点分布位置。 通过多个失效芯片图像的叠加,客户可以看到多个芯片失效积累效果。

2025-06-03 10:08:45 861

861

速率)接口,旨在为主机控制 器和外设(如闪存、SRAM 等)之间提供高效的数据传输。该接口采用 12 个信号引脚,包括一 个差分时钟对(或单端)、一个读写数据选通(RWDS)信号、一个片选(CS#)信号

2025-05-29 15:44:59

时钟缓冲器作为现代电子技术中的一项关键元件,其在信息化建设和智能化发展中所扮演的角色日益凸显。随着社会的不断发展,人们对信息传输的速度和准确性要求越来越高,时钟缓冲器以其独有的功能,确保了数据

2025-05-27 14:08:45 564

564

最近有客户反映国产FPGA京微齐力P2器件内部合封的pSRAM控制器读写效率很高,能达80%以上,而且合封了4片8bit位宽pSRAM芯片,按250MHz主频DDR双沿读写算下来80%效率能跑

2025-05-16 14:19:39 1517

1517

中说“套接字在填充或清空 DMA 缓冲区后,需要一段有限的时间(最多几微秒)才能从一个 DMA 描述符切换到另一个 DMA 描述符”(第 14 页)并且“如果外部外围设备在套接字从内存中检索下一个

2025-05-16 07:51:28

2 次传输,再次卡住的时间更短,然后顺利传输数据。

Buffers working until they get stuck缓冲器在卡住之前一直在工作

前两个缓冲区的标志 A(上)和 B(下),然后

2025-05-16 07:18:39

我想知道我是否可以在数据和电源中使用 Cypd2122 作为 DRP?

如果是,有任何参考设计或应用说明吗?

数据表说不推荐用于新设计,为什么?

2025-05-07 07:28:43

迁移。 在荷兰,我们说苹果和梨不能相提并论,但这并不完全正确。两者都是所谓的手工水果,一个硬一点,另一个软一点。 但拿开源技术与大型技术相比,就好比拿烤箱与餐厅相比。大型科技公司提供完善的服务支持,如今他们在自己的数据中

2025-04-30 16:49:28 557

557 滚珠螺杆在数控机床中如何降低摩擦系数?

2025-04-24 17:49:18 594

594

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

如何使用 S32 Design Studio for ARM 将自定义数据放入 SRAM 中以进行S32K146?

2025-04-01 08:27:32

mcxn947自带的ram太小了,无法满足需求,想外扩一块psram,比如乐鑫的esp-psram64芯片,这个需求有哪个案例可以参考吗?

2025-03-31 06:54:14

ASL6328替代AG7220|替代AG7120|HDMI延长线缆方案|HDMI信号放大方案ASL6328芯片设计原理图:

ASL6328特性

概述

符合 HDMI 2.0 规范,数据速率高达

2025-03-28 16:19:50

(主)

int_sram_no_cacheable

int_sram_shareable

由于我超出了 RAM 使用量 (int_sram),我能够将一些数据

2025-03-27 07:16:12

RFID洗涤标签在数字化工厂中的应用,以其耐用性、高效性和智能化管理能力,为纺织、洗涤和制造行业提供了全面的解决方案。以下是RFID洗涤标签在数字化工厂中的主要应用场景及其优势:1.生产流程优化

2025-03-26 16:54:52 564

564

RFID标签在数字化工厂中的应用,以其高效、精准和自动化的特性,正在成为推动制造业数字化转型的重要工具。以下是RFID标签在数字化工厂中的主要应用场景及其优势:1.生产流程优化与追踪实时追踪

2025-03-25 14:13:13 735

735

在嵌入式开发中,流缓冲区(Stream Buffer)是FreeRTOS中用于高效处理字节流数据传输的核心机制,尤其适合任务间或中断与任务间的连续数据传输场景(如串口通信、网络数据流等)。本文将深入

2025-03-24 11:37:29

数据中台是一种集成和管理企业内部及外部数据的技术架构,旨在实现数据的采集、存储、处理、分析和应用。它能够解决多个方面的问题,具体如下: 一、数据孤岛问题 数据孤岛是指不同部门或系统之间的数据

2025-03-18 15:24:43 562

562 直线导轨在数控机床中起着关键作用,通常用于支撑和导向机床上移动的部件,以确保其运动精度和稳定性。

2025-03-13 17:43:48 912

912

采用STM32F427+FPGA+Flash。

STM32通过FMC总线访问FPGA内部SRAM,起始地址为0x60000000;

Flash中存储FPGA的配置数据,STM32和FPGA均可

2025-03-12 07:59:54

SDRAM和NAND都使能了,都能正常工作,但是读取Nand数据然后存放到SDRAM中,发现SDRAM中的数据是错误的。但是将数据存到内部的IRAM中数据是正确的。请问NAND跟SDRAM不能同时访问么?该问题同时存在于STM32F767跟STM32H743中。请帮忙解答,谢谢!

2025-03-11 08:13:19

两块SRAM分别位于不同的基地址,有什么方法可以使这两块区域SRAM当成一块使用

2025-03-07 08:59:10

想用来做一个手表,怕内存不够用想外扩,不知道2mb flash和768kb的sram够不够,打算外扩esp-psram,8M。希望能够有大佬能够给出建议,感谢回答!!

2025-03-07 07:23:53

HAC925QN是一款2.1GHz,2路输出差分高性能时钟扇出缓冲器,且高度通用、低附加抖动的产品,可以生成两路LVPECL时钟副本的缓冲区输出,可以支持LVPECL、LVDS或LVCMOS输入。最大时钟频率高达2.1GHz。该器件专为高频、低相位噪声时钟和数据信号的信号扇出而设计。

2025-03-06 15:11:55 0

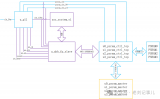

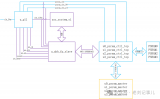

0 前言 SDRAM控制器里面包含5个主要的模块,分别是PLL模块,异步FIFO 写模块,异步FIFO读模块,SDRAM接口控制模块,SDRAM指令执行模块。 其中异步FIFO模块解读

2025-03-04 10:49:01 2301

2301

一、前言 在全球半导体供应链波动的背景下,"国产替代"已成为中国硬科技领域的关键词。而在时钟信号领域这一核心赛道,华奥创芯推出的HAC946QN时钟缓冲器,凭借其突破性性能表现,正成为硬件工程师替代

2025-02-27 11:59:18 1464

1464 为了加深读者对 FPGA 端控制架构的印象,在数据读取的控制部分,首先我们可以将SDRAM 想作是一个自来水厂,清水得先送至用户楼上的水塔中存放,在家里转开水龙头要用水时,才能及时供应,相同

2025-02-26 15:27:09 1813

1813

Ti是否有一款停产的DLP产品,型号为1191-403BC.官网已经查不到此型号。是否有替代型号可以推荐?以及替代型号与原型号有哪些差别,谢谢!

2025-02-26 08:26:57

command.v文件对应图中SDRAM指令执行模块,它会从SDRAM接口控制模块接收指令,然后产生控制信号直接输出到SDRAM器件来完成所接收指令的动作。

2025-02-25 10:32:12 1034

1034

物联网数据中台可以接入的设备种类非常广泛,涵盖了从简单的传感器到复杂的智能设备。以下是物联网数据中台常见的接入设备类型: 1. 传感器 : - 环境监测传感器 :温度、湿度、气压、空气质量等传感器

2025-02-24 11:07:29 733

733 手中的一支智能笔。在数字前端开发中,工程师要编写RTL(寄存器传输级)代码,这就好比是在创作一篇特殊的文章。Gvim提供了一个书写的平台,让工程师能够输入、修改和组织代码内容。 它类似于传统的纸质笔记本,但功能强大得多。在这个“笔记本”里,工程师可以精

2025-02-20 10:21:08 840

840 时钟缓冲器是一种用于生成、处理和分配时钟信号的电子电路,主要用于确保数字系统中各模块的同步操作。其核心功能是对输入时钟信号进行调理和分配,以提供高质量、低抖动的时钟信号。

2025-02-17 14:34:51 2136

2136 SAFERTOS中的流缓冲区(Stream buffer)机制,可以实现任务到任务或中断到任务之间的通信。字节流是由发送方写入缓冲区,接收方读取缓冲区数据。流缓冲区作为队列的轻量级级替代方案,适合单读单写场景,写者在流缓冲区中放置任意数量的字节,读者读取任意数量的字节。

2025-02-14 11:33:16 1074

1074

1、TLV5616存在数据间隔转换 2、 数据转换过程中当数字量为奇数值时写不进去或着转换不出模拟量的问题! 芯片工作外围:5v (VCC)、Uref 2.56v(基准电压)

2025-02-14 08:12:26

HAC946QN是一款2.1GHz,6路输出差分高性能时钟扇出缓冲器,且高度通用、低附加抖动的产品,可以生成六路LVPECL时钟副本的缓冲区输出。可以支持LVPECL、LVDS、HCSL或

2025-02-13 16:56:46 1

1 、HCSL 或 LVCMOS(单端)输入。该产品具有配备中 心抽头的差分输入,100Ω片上终端电阻器。最大时钟频率高达 2.1GHz。该器件 专为高频、低相位噪声时钟和数据信号的信号扇出而设计。

a) 1:8 差分时钟缓冲器;

b) 通用输入接受 LVPECL、LVDS 和 HCSL

2025-02-13 16:54:49 0

0 HAC925QN 是一款 2.1GHz,2 路输出差分高性能时钟扇出缓冲器,且高度 通用、低附加抖动的产品,可以生成两路 LVPECL 时钟副本的缓冲区输出,可 以支持 LVPECL、LVDS 或

2025-02-13 16:53:50 0

0 、HCSL 或 LVCMOS(单端)输入。该产品具有配备中 心抽头的差分输入,100Ω片上终端电阻器。最大时钟频率高达 2.1GHz。该器件 专为高频、低相位噪声时钟和数据信号的信号扇出而设计。

a) 1:4 差分时钟缓冲器;

b) 通用输入接受 LVPECL、LVDS 和 HCSL

2025-02-13 16:53:42 0

0 HAC946QN时钟缓冲器的技术优势与应用场景,完全替代ADCLK946BCPZ

2025-02-13 14:09:13 897

897 按键KEY1触发写,将计数器产生的0到255的数据写到FIFO写模块里面,继而写到SDRAM 器件里面。

2025-02-07 09:33:41 1192

1192

高速缓冲存储器(Cache)是内存的一种特殊形式,但它与通常所说的主存储器(RAM)有所不同。在计算机存储体系中,Cache位于CPU和主存储器之间,用于存储CPU近期访问过的数据或指令,以加快数据的访问速度。

2025-01-29 11:48:00 3395

3395 量子芯片在未来某些领域的应用可能会展现出更大的优势,但它目前并不能完全替代半导体芯片。以下是对这一观点的详细解释:

2025-01-27 13:51:00 2593

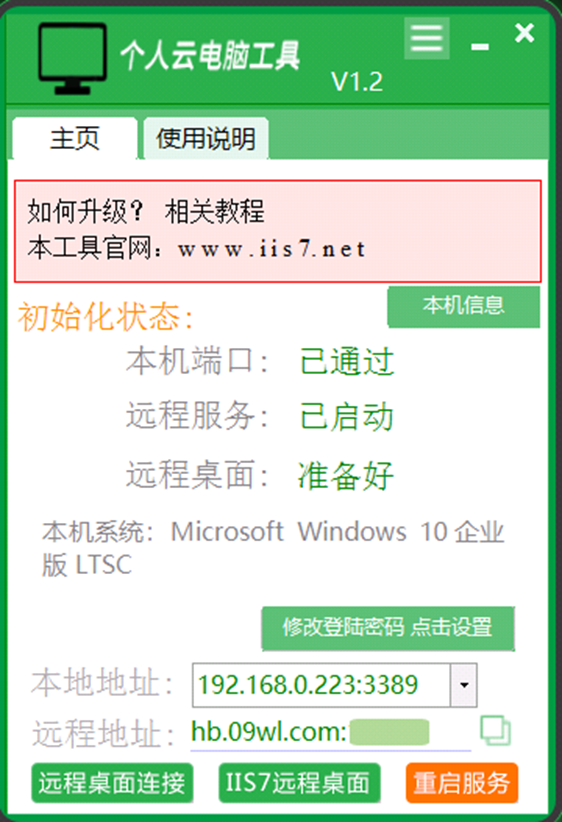

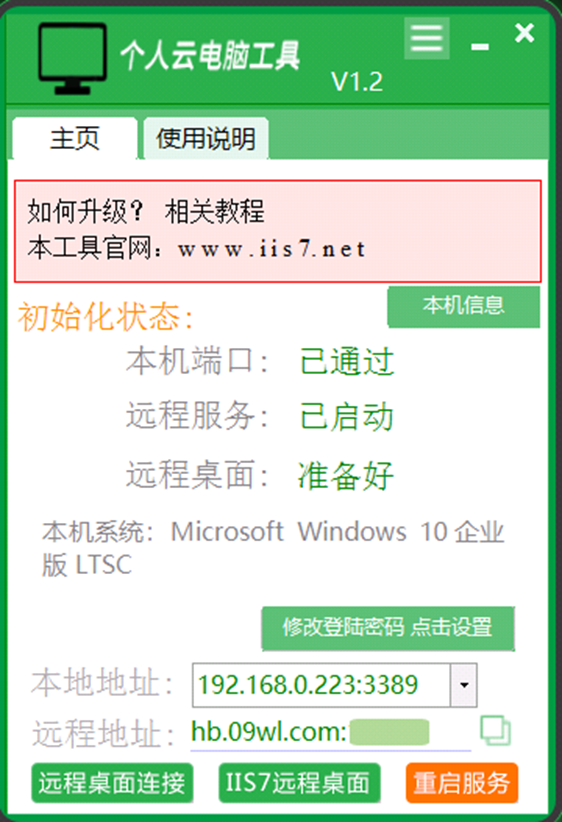

2593 放在云端,让用户可以通过任何设备访问强大的计算能力。今天就为大家介绍怎么操作电脑替代云存储。 在数字化时代,将闲置的旧电脑改造成私有云存储服务器,不仅可以充分利用闲置的硬件资源,还能为家庭或个人提供一个安全、

2025-01-16 09:10:21 742

742

卡诺图(Karnaugh map,简称K-map)在数字电路中具有广泛的应用,它主要用于布尔代数表达式的简化和最小化,从而优化数字电路的设计。以下是卡诺图在数字电路中的具体应用: 一、布尔代数

2025-01-14 17:08:29 2549

2549 物联网数据中台是一个集成和管理大量设备产生的数据的平台,主要功能包括数据采集、数据管理、数据可视化和数据分析等。它为企业提供了一个全面的数据管理和分析解决方案,有助于企业在数字化转型中实现更高的效率

2025-01-10 11:24:20 833

833 工控主板作为数控机床的核心组件之一,发挥着至关重要的作用。以下是工控主板在数控机床设备中应用的详细介绍:

2025-01-09 15:33:57 877

877 数据库是现代信息技术中存储和管理数据的核心组件。字符串作为最常见的数据类型之一,在数据库中的存储方式对其性能和可扩展性有着重要影响。 数据类型 固定长度字符串 :如CHAR类型,它为每个字符串分配

2025-01-07 15:41:59 1338

1338

电子发烧友App

电子发烧友App

评论