一、读写均衡失效引发的核心问题 读写均衡(磨损均衡,Wear Leveling)是SD卡固件通过算法将数据均匀分配到闪存芯片各单元,避免局部单元过度擦写的关键机制。瀚海微SD卡出现读写均衡失效后,会

2025-12-29 15:08:07 98

98

的 bootloader 源码

但 CMake 缓存中记录的却是 D:/esp-idf-v5.4.3 路径的源码

路径不匹配导致配置阶段失败,进而中断整个编译流程

解决方案

下面是一步步的修复操作,你可以按顺序执行

2025-12-23 07:07:26

本次测评基于瑞萨RA6E2地奇星开发板,验证其内部CodeFlash与DataFlash的读写功能稳定性与可靠性,测试Flash擦除、写入、读取及数据验证的全流程可行性,为后续嵌入式项目存储方案提供参考依据。

2025-12-16 08:08:45 651

651

视频推荐随着储能控制系统智能化发展,对实时处理和高速缓存需求提升。本测试对EM-1000与EM-1000G的Redis性能进行对比,评估其在吞吐、响应与稳定性上的差异,为客户提供精准硬件选型依据

2025-12-02 11:39:20 207

207

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

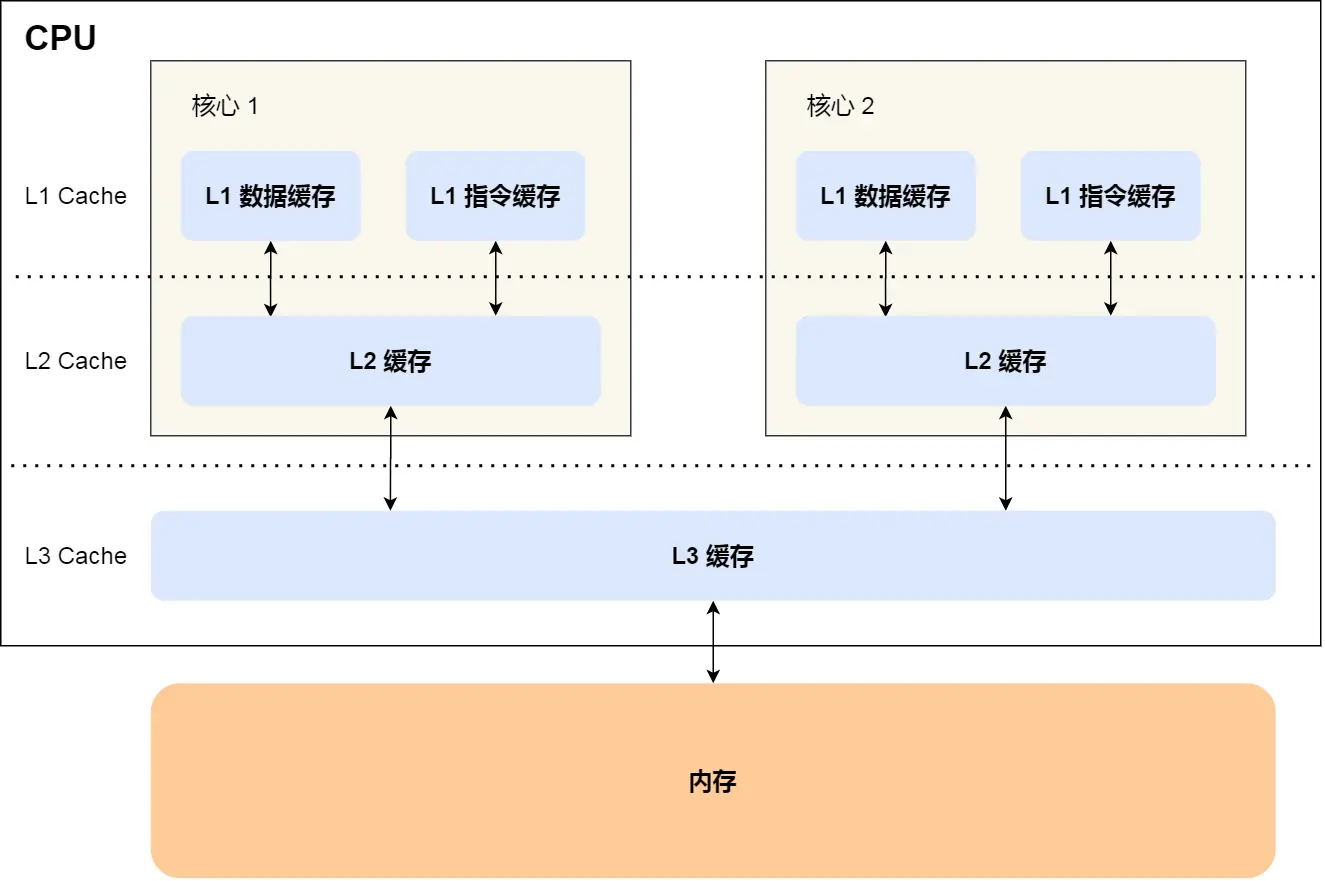

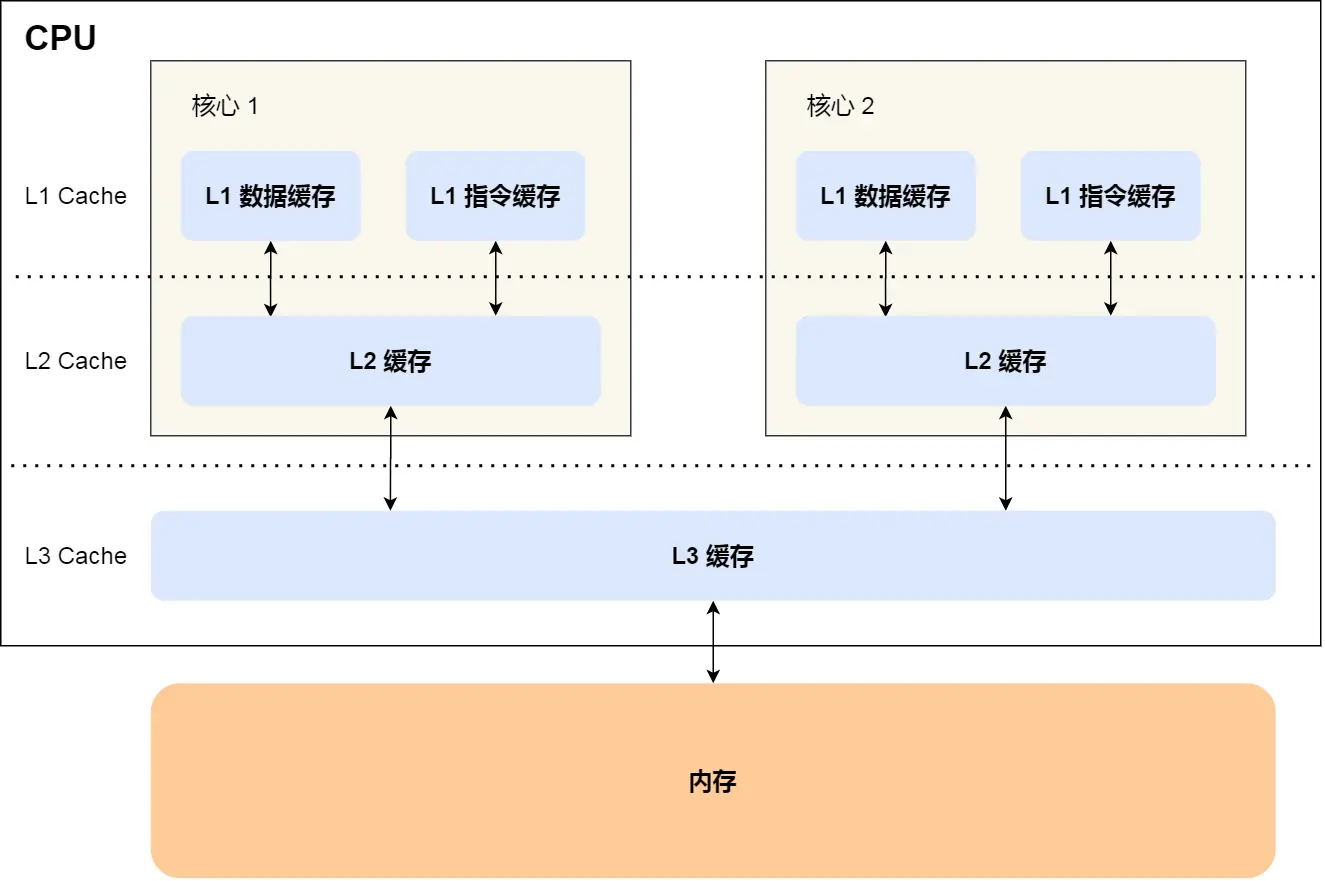

的运算速度远高于内存的读写速度,为了避免被拖慢,CPU 都自带一级缓存和二级缓存。基本上,CPU 缓存可以看作是读写速度较快的内存。

但是,CPU 缓存还是不够快,另外数据在缓存里面的地址是不固定

2025-11-20 06:45:06

的flash均无法进行读写。

麻烦给解释一下为什么会出现这种问题以及解决方案,是否一定需要外部加上SDRAM或者DDR?

2025-11-19 19:53:00

RA6809MQ4N是台湾瑞佑科技股份有限公司(RAiO)研发推出的一款低功耗及显示功能强大的彩色液晶图文显示控制器,芯片内建了128Mb SDRAM显存,可作为多区块显示的缓存,可以快速更新屏幕

2025-11-18 10:32:24

全面解析,覆盖全场景需求。 一、数据读写超时涉及的核心方面 (一)接口与硬件适配层面 接口速率瓶颈:使用USB2.0、SDHC等低速接口或老旧读卡器,限制高速存储卡(如支持UHS-II协议的瀚海微卡)性能发挥,大数据传输时速率不匹配引发超时。 硬

2025-11-17 10:04:44 461

461 在处理器性能持续攀升的今天,存储系统的速度已成为制约整体算力的关键瓶颈之一。作为最接近CPU核心的存储单元,SRAM(静态随机存取存储器)承担着高速缓存的重要角色,其性能直接影响数据处理效率。当前

2025-11-12 13:58:08 455

455 在物联网技术飞速发展的当下,RFID读写器作为数据采集的核心设备,已广泛渗透到生产生活的多个领域。其中,超高频rfid读写器凭借独特的性能优势,成为物流、零售、制造等行业的“得力助手”。很多人会好

2025-11-06 15:08:46 340

340

电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4 蜂鸟E203怎样外部的摄像头进行数据传输

2025-11-05 06:58:39

在有些情况下,我们想要把代码放到SDRAM运行。下面介绍在APM32的MCU中,如何把代码重定位到SDRAM运行。对于不同APM32系列的MCU,方法都是一样的。

2025-11-04 09:14:18 4981

4981

OPPO Pad 5 搭载 3nm 先进制程的天玑 9400+ 旗舰芯,全大核架构设计,内建大容量高速缓存,以更高的单线程和多线程任务处理性能,带来令人惊叹的日常应用、游戏等全场景应用体验,内置

2025-10-30 15:44:42 622

622 SD卡读步骤:

SD卡初始化完成后,SD 卡初始化过程中的 SPI 时钟需要使用低速时钟(最好小于 400Khz)。所以要对系统时钟进行分频。

SD 卡读取模块: SD 卡读取的过程和初始化流程

2025-10-29 07:04:53

凯芯CascadeTeq CSS6404SU-L是一款64Mb QSPI pSRAM,采用串行接口实现高带宽数据传输,工作电压2.7-3.6V,时钟频率达133MHz。适用于物联网、便携设备和工业控制等需要高速缓存的嵌入式场景。

2025-10-28 09:25:00 332

332

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

2025-10-22 17:21:38 4118

4118

DDR控制协议

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源

2025-10-21 14:30:16

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源难以实现大量图像数据

2025-10-21 10:40:28

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源难以实现大量图像数据

2025-10-21 08:43:39

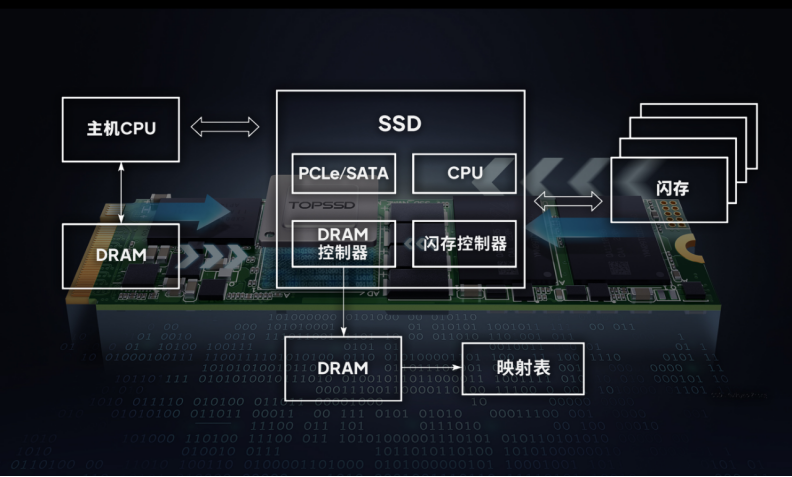

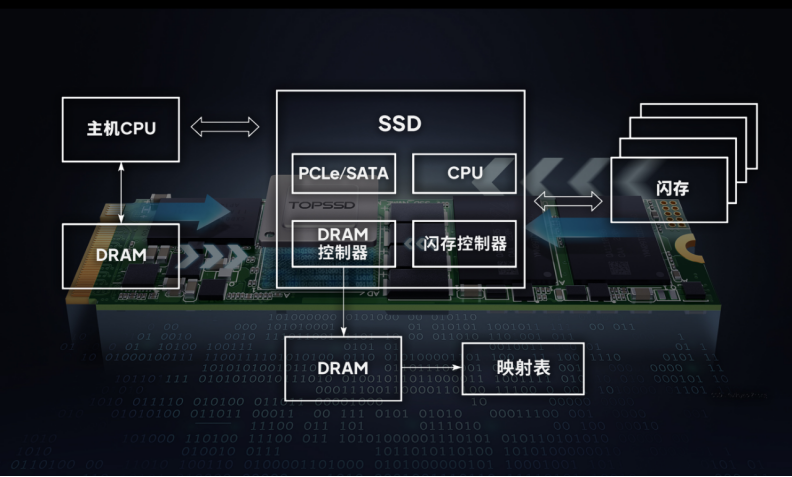

键技术的特点与价值。 Q1:什么是DRAM缓存,它在SSD中起什么作用? DRAM(动态随机存取存储器)在固态硬盘中扮演着"高速缓冲区"的角色。具体到天硕G55 Pro M.2 NVMe工业级SSD,其DRAM缓存主要承担两项关键任务:存储FTL映射表和管理数据传输的临

2025-10-20 17:59:28 655

655

keil+Env怎么把很大的数组定义到SDRAM中?

RTT自带的SDRAM程序运行正常,能够申请里面的空间。

但是没有办法把很大的数组——ltdc_lcd_framebuf[1280][800]

定义到SDRAM中,一运行就出错,请问各位大佬怎么解决啊?

2025-10-11 16:10:01

串口DMA发送有缓存吗, 我是从ringbuffer取出来,放到申请的缓存里,启动串口DMA发送,然后就释放了。暂时没发现什么问题。

用的drv_usart.c是这个版本

2025-10-10 06:14:05

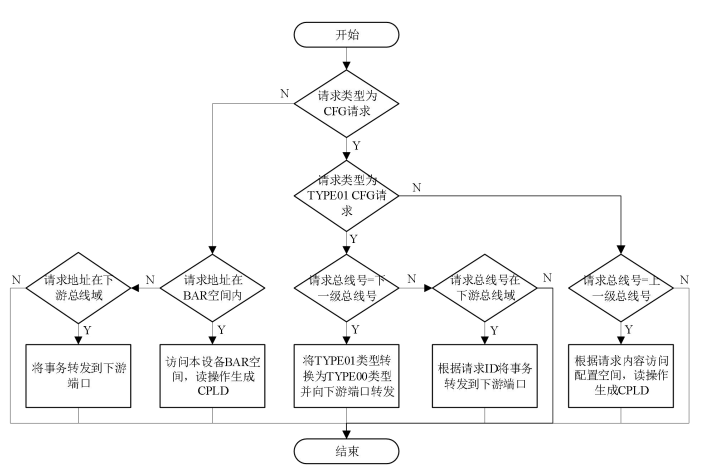

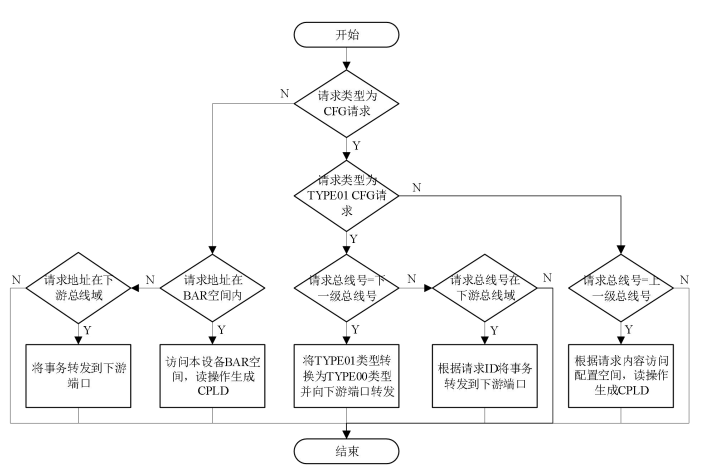

包、 指令响应包、 PRP 响应包并将其放入对应的缓存队列中。 如果类型为 TLP 请求, 根据请求类型对配置空间或 BAR 空间进行读写操作, 读操作生成 CplD 发送到模型输出缓存。

Admin

2025-09-29 09:31:50

当请求类型为 MEM 读写请求时使用地址路由的方式。 如果请求地址在此设备 BAR 空间内, 则对 BAR 空间进行读写操作,读操作将生成 CplD, 从对应请求端口的输出端口发出; 如果请求地址在下游总线域,根据请求 ID 的设备号将事务转发到对应的下游输出端口。

2025-09-23 09:05:25 443

443

程序的执行流程图当对应任务接口的事务缓存中存在未处理事务时, 处理程序从缓存中获取事务。首先检查事务类型, 当事务类型为 Cpl 响应类型事务时, 如果当前程序对应接收端口号为 0, 即接收端口为唯一

2025-09-21 08:51:04

裸机以及RTT初始化是可以正常读写的,但在线程中,用了rt_thread_mdelay,SDRAM内的数据会被清理,数据丢失,也无法读写了,调试发现是rt_schedule导致的,请问这个该问题如何解决?

2025-09-18 07:53:44

:

扩展 MCU 外部数据 RAM

超低功耗

简单的接口设计,可高效利用 PCB 空间

SDRAM 扩展解决方案的经济高效的替代方案

Hyper Bus 接口由 13 条数据和控制线组成,确保紧凑的设计并

2025-09-05 06:06:33

蓝牙耳机作为现代科技的热门产品,其生产流程的高效与精准至关重要。本文将深入剖析蓝牙耳机的生产流程,并重点介绍一套兼顾稳定、快速与性价比的系统搭建方案,带您领略科技生产背后的精细工艺与智慧选择。蓝牙

2025-09-04 11:39:06 489

489

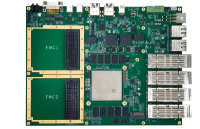

作为主处理器,FPGA 外挂两组 72 位 DDR4 SDRAM,用来实现超大容量数据缓存,DDR4 的最高数据缓存带宽可以达到2400MHz,DDR4 的缓存

2025-08-29 15:57:37 398

398

:XCKU115-2FLVF1924I 作为主处理器,FPGA 外挂两组 72 位 DDR4 SDRAM,用来实现超大容量数据缓存,DDR4 的最高数据缓存带宽可以达到 2400M

2025-08-29 15:49:41

DDR4SDRAM,用来实现超大容量数据缓存,FPGA的PS端外挂1组72位的DDR4SDRAM的高速数据缓存,用来支持操作系统的运行。该平台支持2个FMC+接口,每个F

2025-08-29 15:29:49 1292

1292

DDR4 SDRAM,用来实现超大容量数据缓存,FPGA的PS端外挂1组72位的DDR4 SDRAM的高速数据缓存,用来支持操作系统的运行。该平台支持2个FMC+接口,

2025-08-29 15:28:59

浏览 M453 的各种示例代码,我没有看到显式启用 4kb 缓存,那么缓存是否默认启用?

2025-08-28 08:27:31

用户疯狂查询数据库中不存在的数据,每次查询都绕过缓存直接打到数据库,导致数据库压力骤增。

2025-08-20 16:24:14 627

627 硬盘的物理结构可以分为外部结构和内部结构。外部结构主要包括硬盘的外壳和电路板,硬盘的外部物理故障通常是电路板故障。

硬盘的电路板上分布着主控芯片、缓存、电机驱动芯片、BIOS及其他电子元器件。在电路板前端还有硬盘的电源接口和数据线接口。这些电路板上的元器件都有出现故障的可能。

2025-08-20 14:34:20 662

662 两个总线能不能同时使用,用了华邦的SDRAM发现SDRAM数据高概率读写错误,但是用ISSI的没问题。如果不对外部SRAM读写就正常。

2025-08-12 06:56:57

最新版K230IDE怎么打开帧缓存区

2025-08-08 06:01:51

二、测试原理

核心三步骤

清除缓存 :确保数据从物理介质读取echo 3 > /proc/sys/vm/drop_caches

执行读取 :使用dd命令直读设备dd if=/U盘路径

2025-08-07 19:48:25

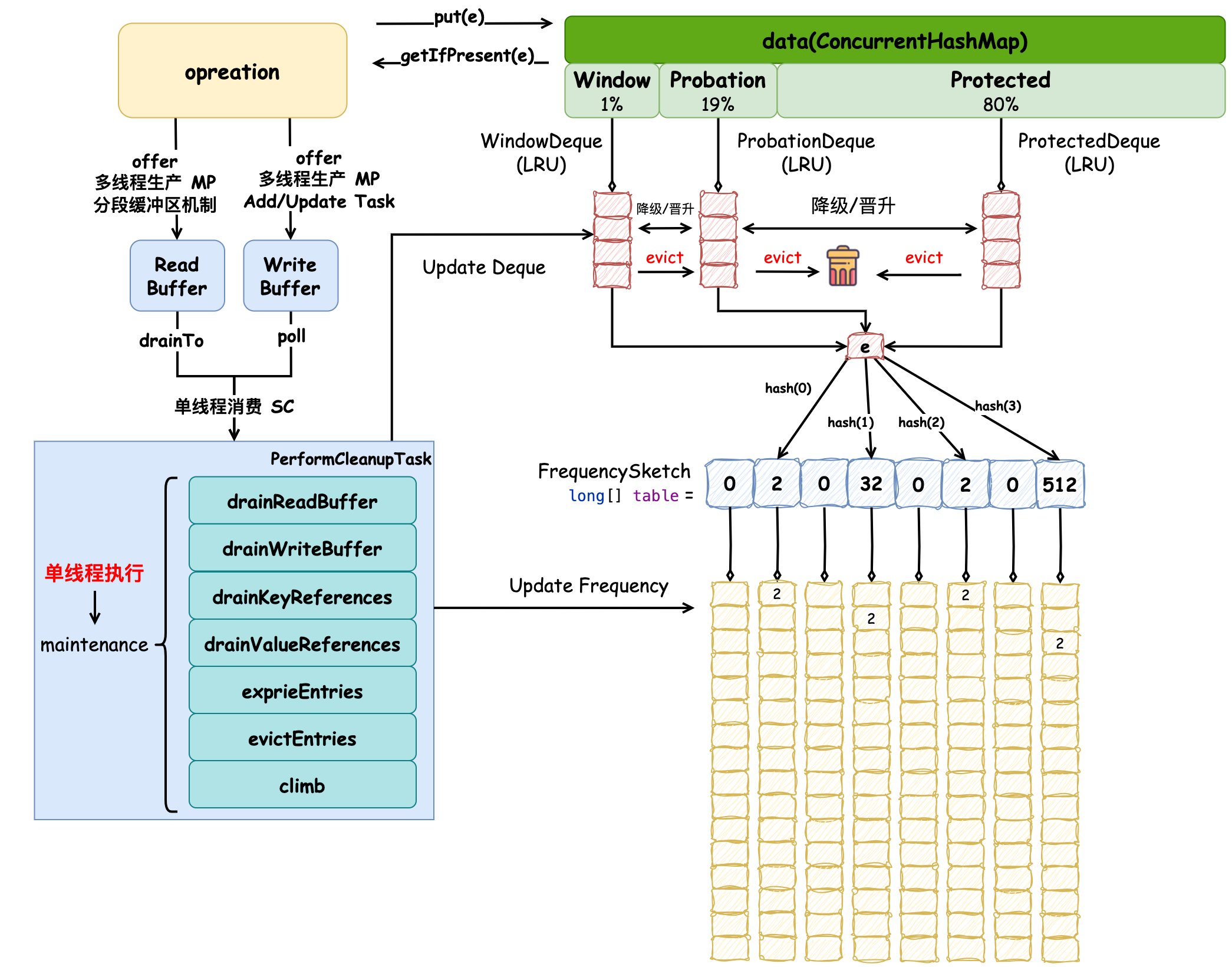

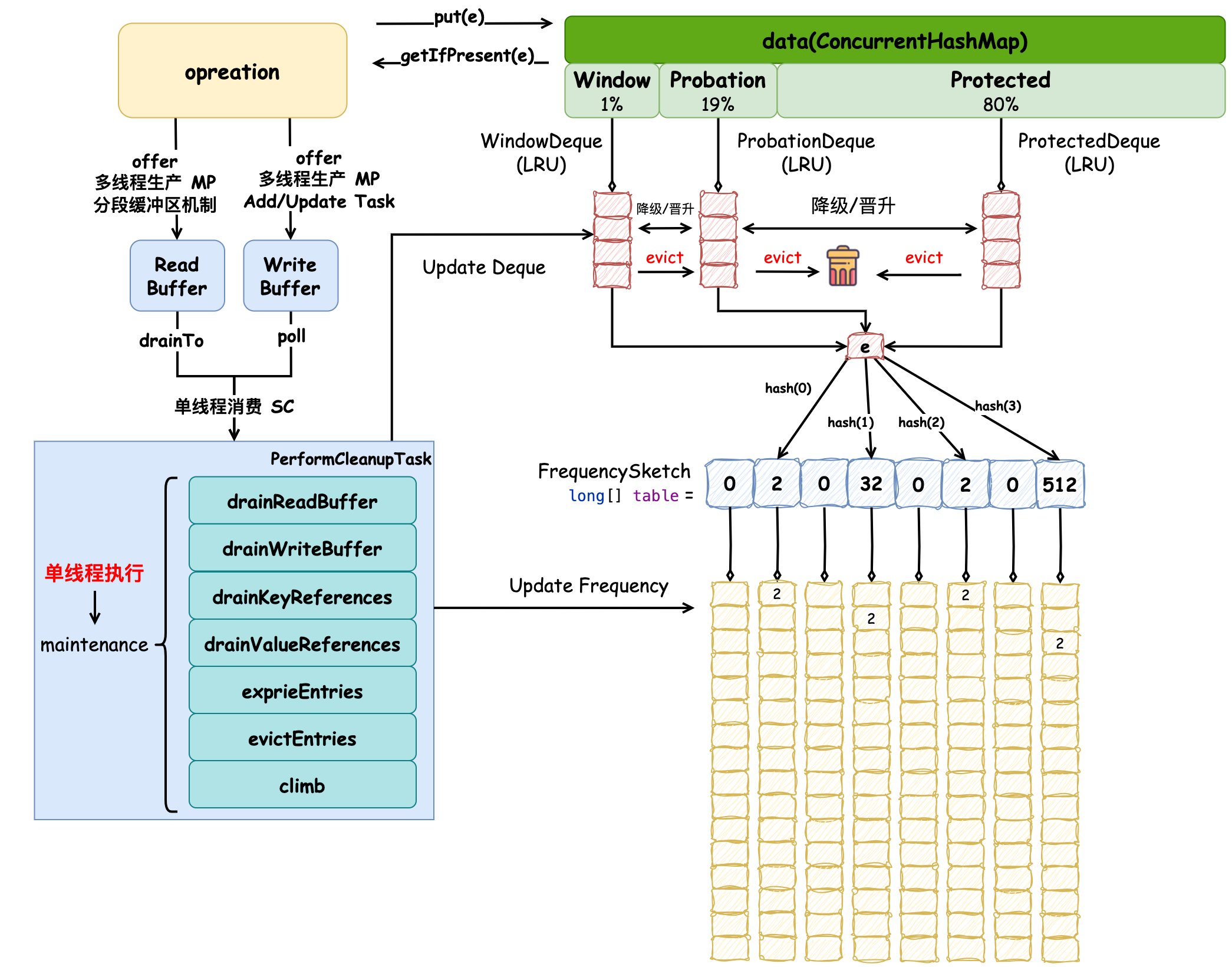

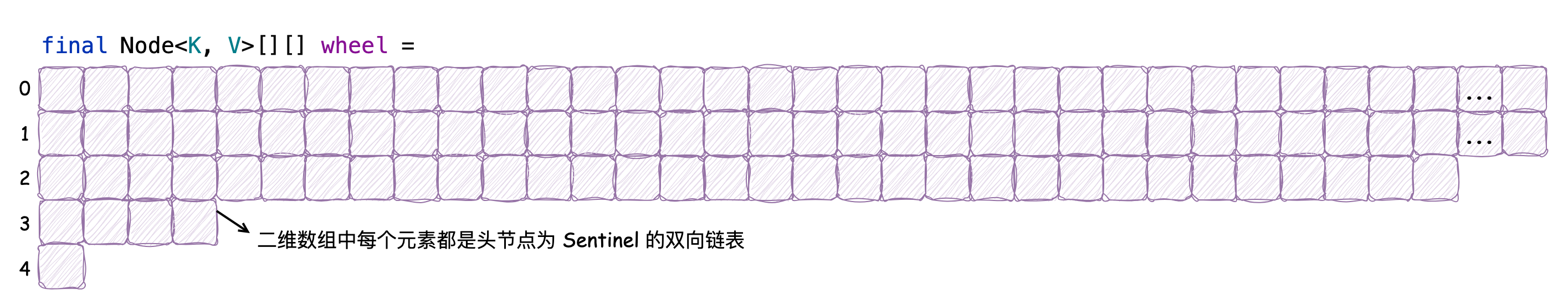

文章将采用“总-分-总”的结构对配置固定大小元素驱逐策略的 Caffeine 缓存进行介绍,首先会讲解它的实现原理,在大家对它有一个概念之后再深入具体源码的细节之中,理解它的设计理念,从中能学习到

2025-08-05 14:49:12 586

586

我们详细介绍了 Caffeine 缓存添加元素和读取元素的流程,并详细解析了配置固定元素数量驱逐策略的实现原理。在本文中我们将主要介绍 配置元素过期时间策略的实现原理 ,补全 Caffeine

2025-08-05 14:48:13 525

525

问了技术支持说可以进行读写操作,但是我看着手册修改指令和流程,连第一步打开RF会话的反馈都不对,有没有好心人指导指导,可有偿

2025-07-28 14:34:23

我用读卡器能够读写M1的卡,但是现在要用ST25TA64K这个卡,我在原读写M1的程序上改,因问过技术支持,说能够进行读写操作这个卡。但我修改后,连第一步打开RF会话都不行。

原M1卡流程:寻卡唤醒

2025-07-28 14:16:30

harmony-utils之CacheUtil,缓存工具类

2025-07-04 16:36:34 374

374 在多核高并发场景下, 缓存伪共享(False Sharing) 是导致性能骤降的“隐形杀手”。当不同线程频繁修改同一缓存行(Cache Line)中的独立变量时,CPU缓存一致性协议会强制同步整个

2025-07-01 15:01:35 578

578

,MT/s)、时序(CL值)。

3.2 SRAM - CPU的高速缓存

原理:利用4-6个晶体管组成双稳态触发器来存储一位数据。只要通电,状态就能保持,无需刷新。

特点:

优点:速度最快(皮秒到纳秒级

2025-06-24 09:09:39

无法确定如何在 C++ 中的 NPU 上使用模型缓存

2025-06-24 07:25:43

cy7c68013a 异步slave fifo 模式,外部mcu无法读写fifo

上位机发送bulk数据,flag标志是对的,SLCS也拉低了,是设置的低有效, 检测到了flag不为空的标志后

2025-06-03 10:49:04

怎样使用Jlink (SEGGER) 通过SWD读写呢?Jlink没有找到CYPD6125的信号,官方也没有找到CYPD6125对应的FLM和xml 文件

2025-05-27 06:45:43

维烦恼,非常适合高并发场景下的数据快速读写需求

下面我将从信息获取到代码实战,手把手带大家实现云缓存接入。

一、云缓存信息获取全攻略

1.1 基础信息获取

登录控制台

打开AppGallery

2025-05-22 18:37:01

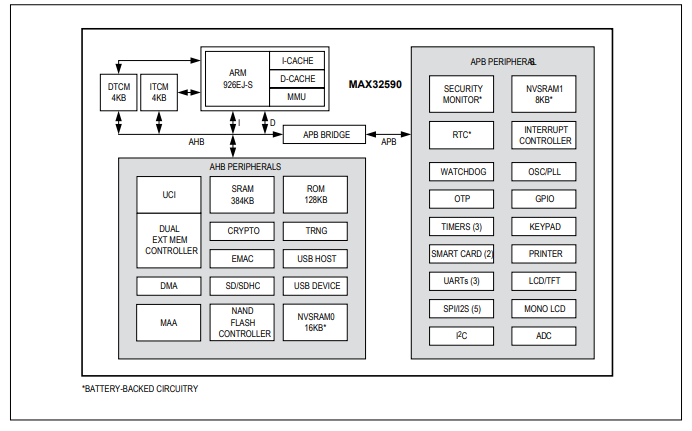

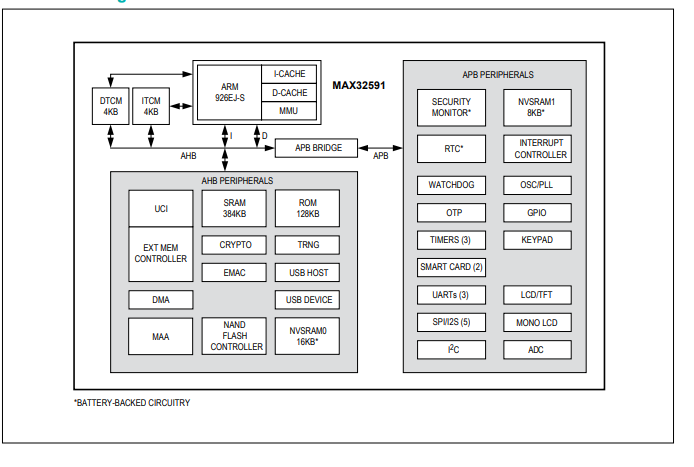

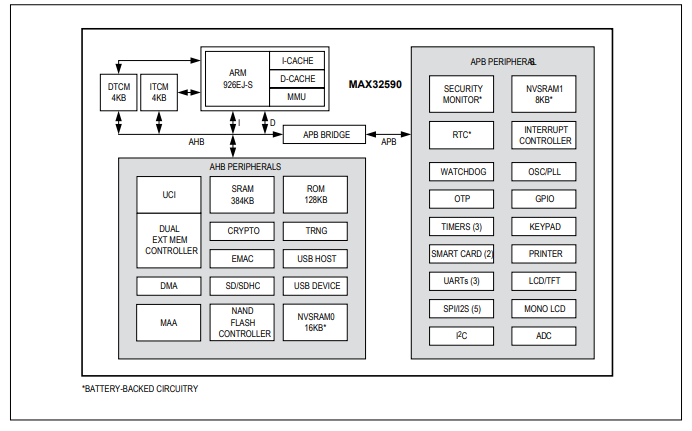

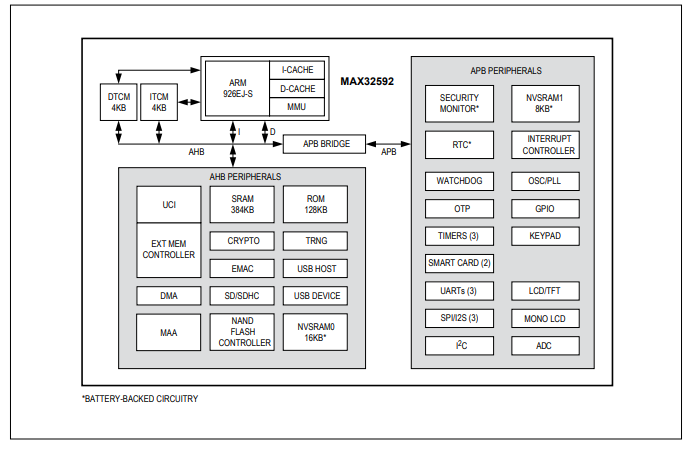

的解决方案,用于构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32590集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令TCM、4KB数据TCM

2025-05-15 09:38:55 660

660

分应用场景来看;铜互联应用场景主要有:芯片直出跳线overpass:高速跳线overpass可解决数据量激增及带宽更高时面临的传输问题,可实现AISC与背板、ASIC与IO接口及芯片之间的互连,芯片

2025-05-09 07:34:36 2023

2023

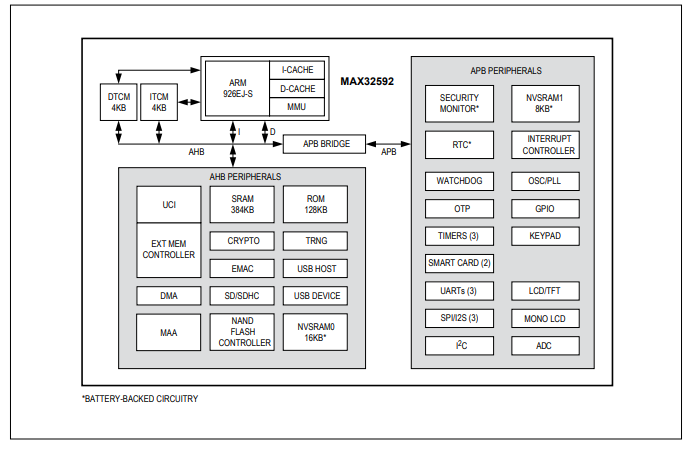

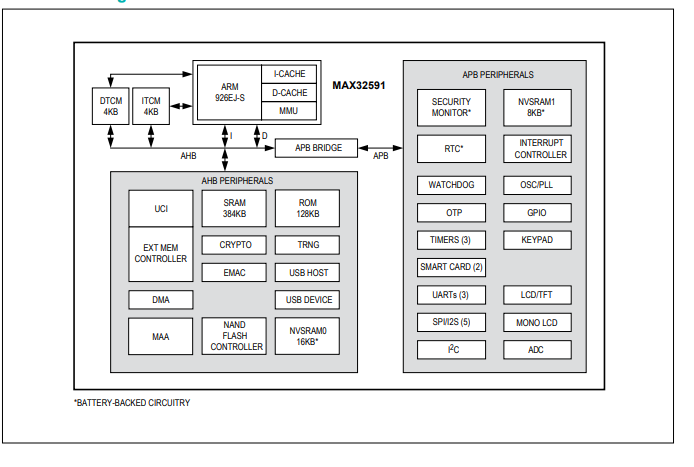

的解决方案,用于构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32591集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令TCM、4KB数据TCM

2025-05-08 14:34:17 636

636

的解决方案,用于构建新一代信任设备,例如:便携式多媒体EFT-POS终端。MAX32592集成了存储器管理单元(MMU)、32KB指令高速缓存器、16KB数据高速缓存、4KB指令TCM、4KB数据

2025-05-08 14:15:46 679

679

从Flash或外部存储器读取的指令,减少CPU因等待指令加载而停滞,适用于实时性要求高的场景(如中断服务程序)。 D-Cache:缓存从Flash、SRAM或外部存储器读取的数据,加速变量与堆栈的读写操作。 TCM(紧耦合内存):部分MCU(如STM32H743)设置独立TCM区域,存放需极低延

2025-05-07 15:29:47 937

937 Nginx 是一个功能强大的 Web 服务器和反向代理服务器,它可以用于实现静态内容的缓存,缓存可以分为客户端缓存和服务端缓存。

2025-05-07 14:03:02 1105

1105

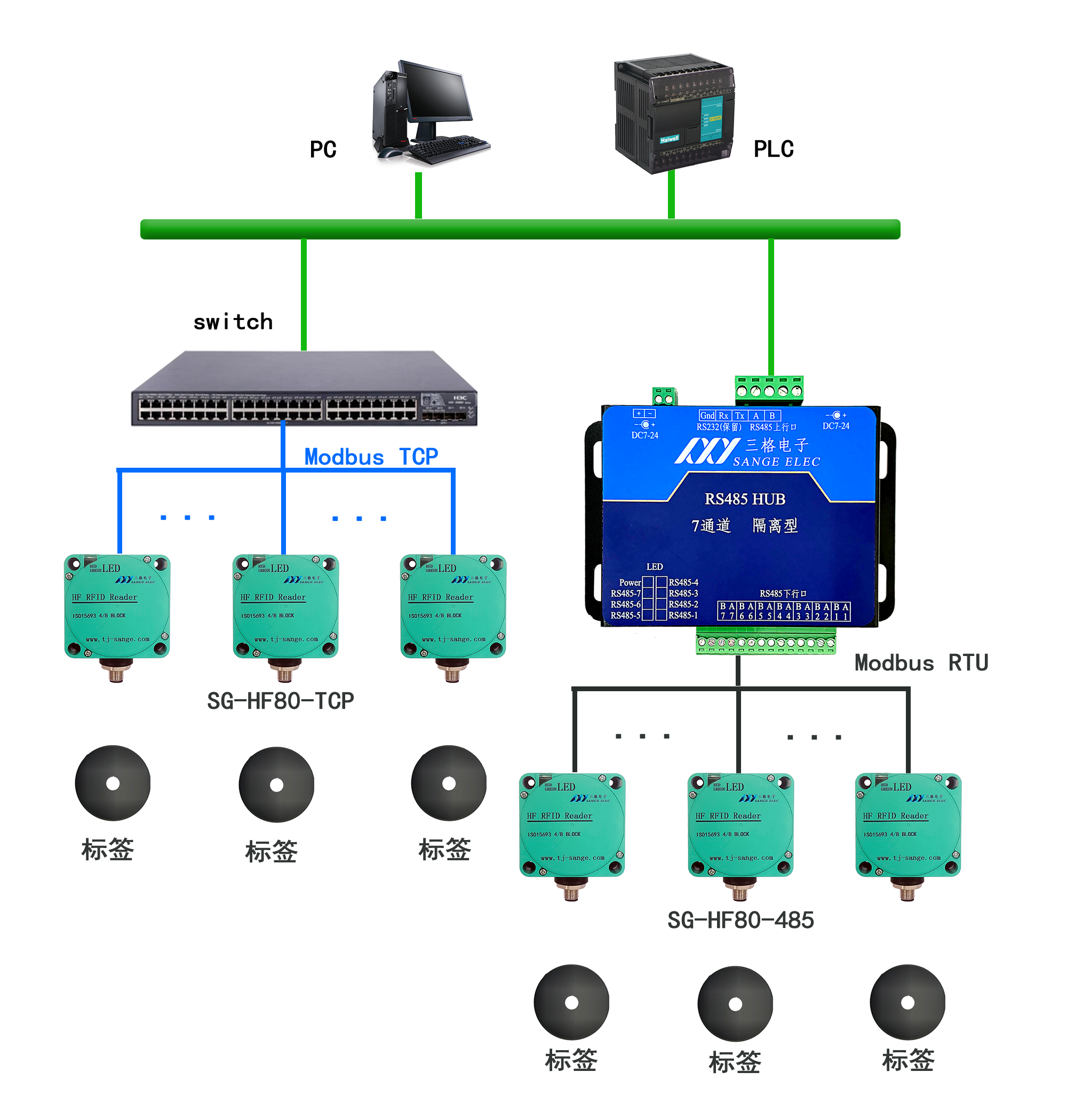

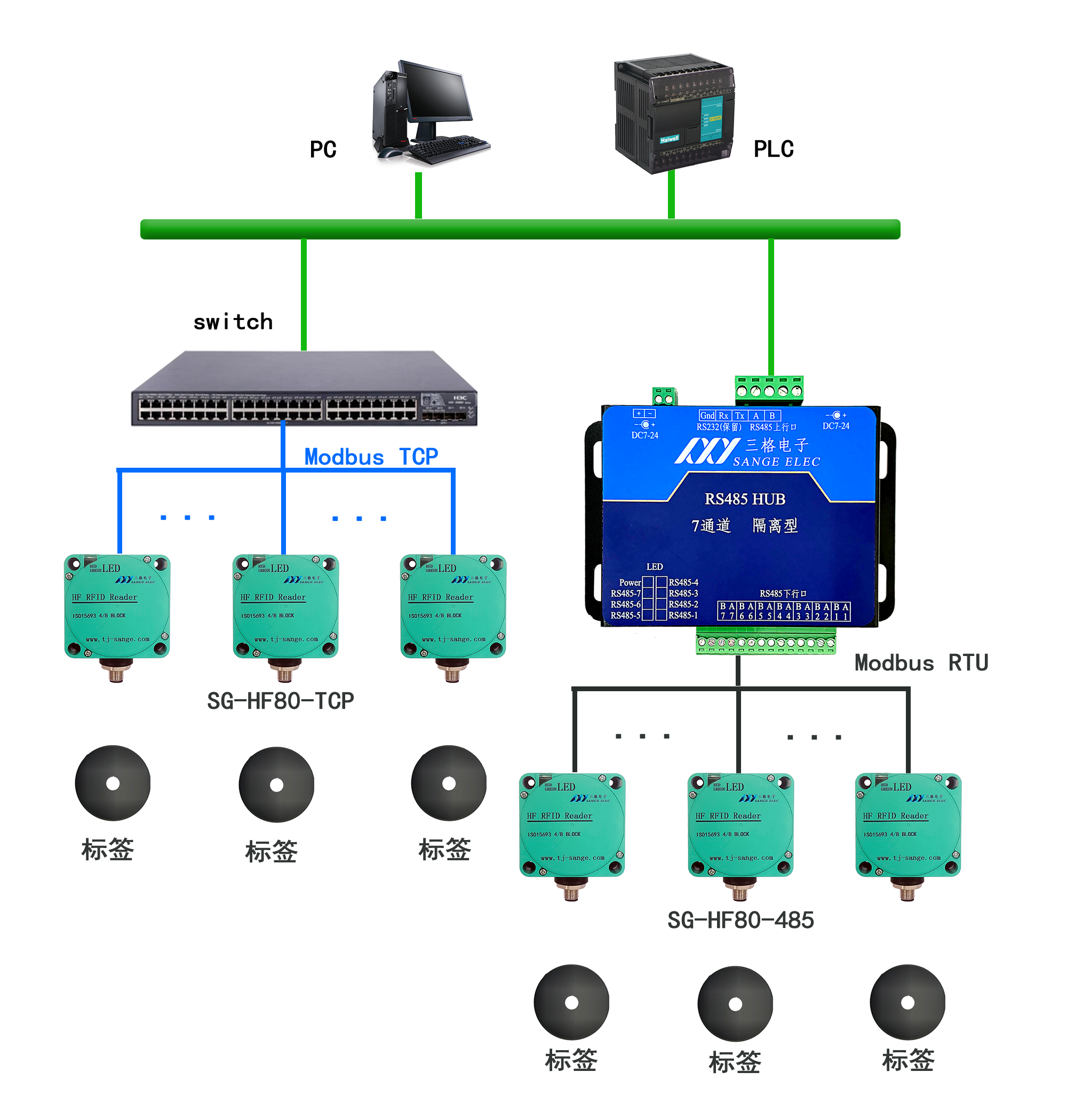

高频工业RFID读写器 型号:SG-HF40-485、SG-HF40-TCP 产品功能 高频工业读写器(RFID)产品用在自动化生产线,自动化分拣系统,零部件组装产线等情境下,在自动化节点的工位上部

2025-05-06 15:33:17 810

810

了新的活力。而规范、科学的安装流程,则是确保叁仟智慧路灯能够稳定运行、充分发挥其功能的基础。深入了解叁仟智慧路灯的安装流程,不仅有助于施工团队高效开展工作,更能为智慧城市建设的稳步推进提供有力保障。接下来,将从前期规划

2025-04-27 17:22:57 780

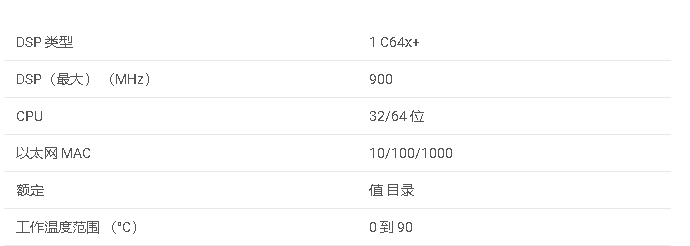

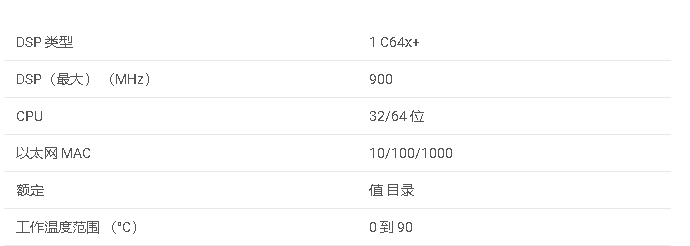

780 TMS320C6452是一款高性能的数字信号处理器,集成丰富的外设接口和高速缓存,适用于需要高速数字信号处理的多种应用领域。其强大的处理能力和灵活的配置选项,使得它成为通信、音频/视频处理、图像处理等领域的理想选择。

2025-04-15 10:38:43 942

942

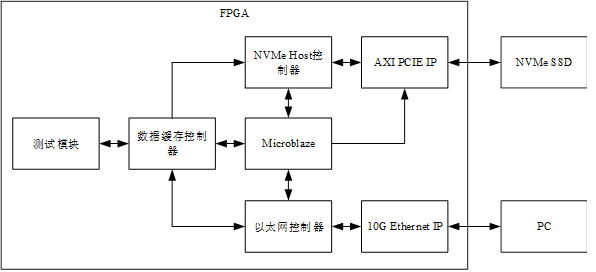

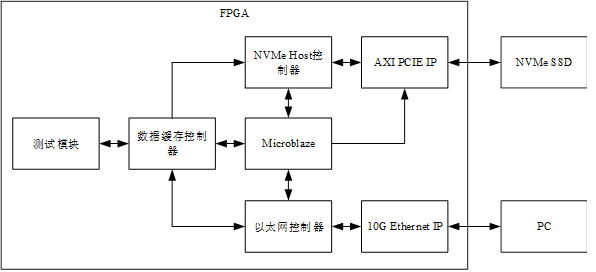

Ethernet IP)、AXI PCIe IP等模块。该系统能够持续接收高速数据流数据,并经缓存模块处理后,存储至NVMe SSD,同时可以将存储数据通过万兆光纤以UDP协议上传至上位机以供后续处理。

2025-04-14 13:38:13 659

659

The issue was i need to run data from external SDRAM memory instead of using internal RAM(DTCM). I

2025-04-14 12:21:59

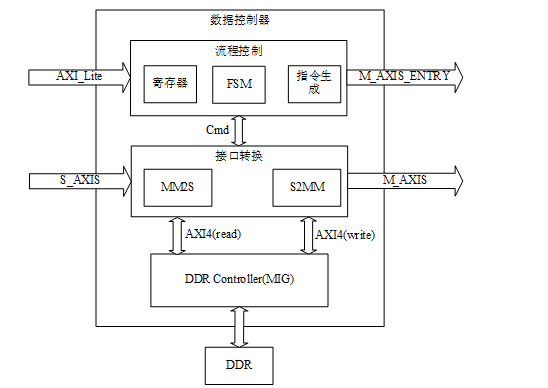

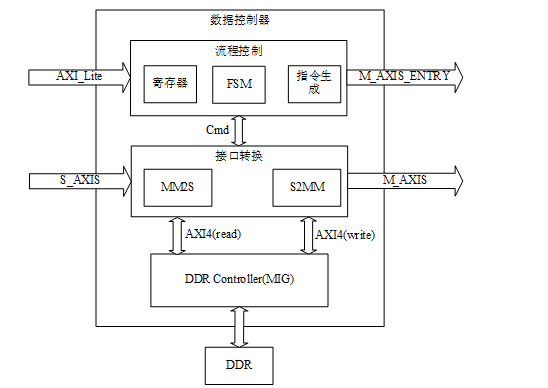

数据缓存控制器主要实现了对大量突发数据的缓存、AXI4接口与AXI4-Stream接口之间的转换和NVMe命令的生成等功能。这里主要介绍相关开发流程。

2025-04-14 10:46:12 678

678

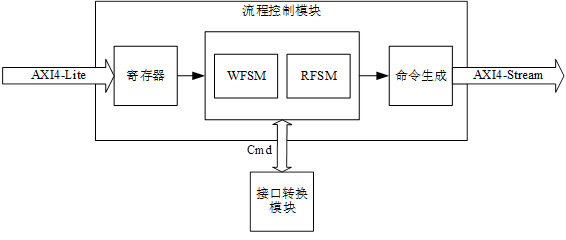

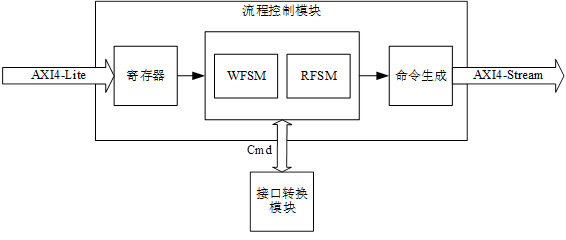

高速SSD系统中流程控制模块设计。该模块主要由寄存器、读状态机、写状态机和命令生成模块组成,系统介绍各模块功能。

2025-04-14 10:43:28 694

694

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

使用的sdram型号是IS42S16160 32mb的是正常的但是更改到IS4216400 8mb的sdram后不能使用,请问1052支持吗?需要修改哪些配置,请大神讲解一下

2025-04-08 19:40:06

RT1176 与 DDR SDRAM 兼容吗?

2025-04-04 06:09:26

强缓存直接告诉浏览器:在缓存过期前,无需与服务器通信,直接使用本地缓存。

2025-04-01 16:01:51 798

798 我按照 AN5191指南启动MPC5777C自定义板,它的一些内置测试要求我禁用缓存以执行某些作,然后重新启用它们以进行正常作。考虑到我把一半的数据缓存作为我的堆栈(使用基于 dcbz 和 dcbtls 指令的 AN5191代码),我应该如何在禁用其余数据缓存的同时继续保持堆栈工作?

2025-03-27 06:01:37

μXI-X1073是中科采象公司自主研发的一款1GSPS、16-bit、8通道高速数字化仪,结合高速大容量数据缓存和高速数据交换技术,适合于高速、瞬态信号的精确捕获,可用于构建多通道、高精度、同步

2025-03-26 09:59:39

耦合的大容量内存 (576KB),可以降低使用高速缓存存储器时出现的执行时间波动,并提供确定性与高速响应处理。RZ/T2L在CPU 内核、外设功能和 LLPP(低延时外设端口)总线等方面具备与 RZ

2025-03-14 15:07:56 907

907

各位大神,我在给G030配置外部高速无源晶振之后,发现无法起振。电路图就跟其他的项目一样,很常规的一个配置。G030的datasheet里面也没说不能使用外部高速无源晶振啊,但是在使用Cube进行

2025-03-14 06:16:14

SDRAM和NAND都使能了,都能正常工作,但是读取Nand数据然后存放到SDRAM中,发现SDRAM中的数据是错误的。但是将数据存到内部的IRAM中数据是正确的。请问NAND跟SDRAM不能同时访问么?该问题同时存在于STM32F767跟STM32H743中。请帮忙解答,谢谢!

2025-03-11 08:13:19

前言 SDRAM控制器里面包含5个主要的模块,分别是PLL模块,异步FIFO 写模块,异步FIFO读模块,SDRAM接口控制模块,SDRAM指令执行模块。 其中异步FIFO模块解读

2025-03-04 10:49:01 2301

2301

CameraLink、CoaXPress)转换为计算机可处理的数字数据。数据缓冲:通过高速缓存(如DDR、SDRAM)缓解数据传输速率与计算机处理速度的不匹配。协议解

2025-03-03 14:36:08 787

787

怎样修改固件会将开机时显示的为无启动画面且为外部输入模式呢?或者说有什么工具可以修改呢?

2025-02-27 06:08:21

为了加深读者对 FPGA 端控制架构的印象,在数据读取的控制部分,首先我们可以将SDRAM 想作是一个自来水厂,清水得先送至用户楼上的水塔中存放,在家里转开水龙头要用水时,才能及时供应,相同

2025-02-26 15:27:09 1813

1813

command.v文件对应图中SDRAM指令执行模块,它会从SDRAM接口控制模块接收指令,然后产生控制信号直接输出到SDRAM器件来完成所接收指令的动作。

2025-02-25 10:32:12 1034

1034

VMware vsan架构采用2+1模式。每台设备只有一个磁盘组(7+1),缓存盘的大小为240GB,容量盘的大小为1.2TB。

由于其中一台主机(0号组设备)的缓存盘出现故障,导致VMware虚拟化环境中搭建的2台虚拟机的磁盘文件(vmdk)丢失。

2025-02-23 17:05:54 701

701

您好,最近购买了贵司的DLP4710LC开发模块,我了解到其有32位输入数据总线,我想知道数据的加载方式是怎样的,就是这32位数据总线是如何控制1920×1080个像素的,他的工作流程是怎样的,相关资料有吗,谢谢。

2025-02-20 06:51:46

在用高速AD采样时当采样开始后发现输入信号质量恶化,感觉应该是采样时钟的影响,请问怎样隔离

2025-02-14 08:09:27

按键KEY1触发写,将计数器产生的0到255的数据写到FIFO写模块里面,继而写到SDRAM 器件里面。

2025-02-07 09:33:41 1192

1192

使用25M的采样频率对1M的信号进行采样,ADS4129以12位cmos电平输出,出来后的数据接缓存器SN74AVC16244,缓存器工作电压是3.3V,在工作过程中缓存器很烫,芯片管脚没有短路

2025-02-07 08:42:27

请问,ADS1210的校准功能怎么使用?具体的流程怎样? 如果在开始就设置好校准模式为 Self-Calibration 模式,那么在读 DOR 的过程中,需要对 OCR 或 FCR操作吗?

2025-02-07 07:22:33

随着信息技术的不断进步,存储设备作为计算机系统的核心组成部分,其性能与稳定性直接影响到整个系统的运行效率。固态硬盘(Solid State Disk,简称SSD)作为新一代存储设备,以其高速读写、低

2025-02-06 16:35:36 4682

4682 在程序运行结束后不会自动释放。这可能会导致程序频繁读写文件后可用物理内存变得很少,必要时(比如内存确实不够用),需要主动释放缓存内存。 注意:一般情况下,是不推荐主动释放缓存内存的,除非你有非常明确的需求,比如测试程序缓存内存的使用情况,

2025-01-16 10:04:02 2241

2241 数据库中的热数据缓存在redis/本地缓存中,代码如下: @Cacheable(value = { "per" }, key="#person.getId

2025-01-14 15:18:04 1250

1250

电子发烧友网站提供《EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器.pdf》资料免费下载

2025-01-14 15:00:14 0

0 电子发烧友网站提供《EE-326: Blackfin处理器与SDRAM技术.pdf》资料免费下载

2025-01-07 14:38:14 0

0 电子发烧友网站提供《EE-162:通过外部存储器总线将ADSP-BF535 Blackfin处理器与高速转换器连接.pdf》资料免费下载

2025-01-07 14:24:49 0

0 电子发烧友网站提供《EE-286:SDRAM存储器与SHARC处理器的接口.pdf》资料免费下载

2025-01-06 15:47:01 0

0 电子发烧友网站提供《EE-127:ADSP-21065L片内SDRAM控制器.pdf》资料免费下载

2025-01-06 15:45:00 0

0

电子发烧友App

电子发烧友App

评论