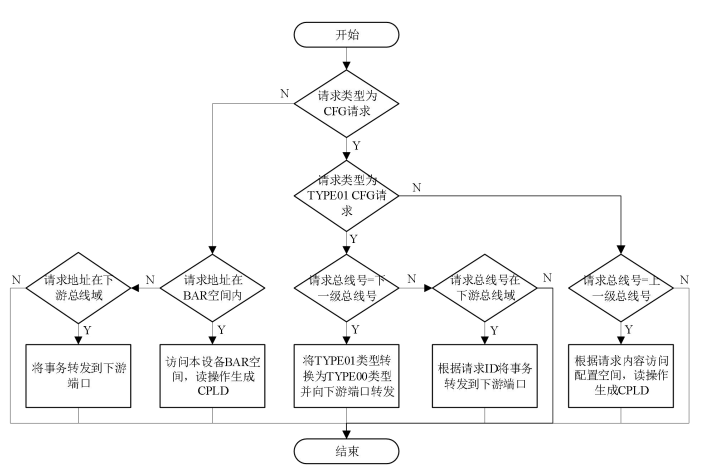

TLP 请求处理子程序流程如图 1 所示。 当请求类型为 MEM 读写请求时使用地址路由的方式。 如果请求地址在此设备 BAR 空间内, 则对 BAR 空间进行读写操作,读操作将生成 CplD, 从对应请求端口的输出端口发出; 如果请求地址在下游总线域,根据请求 ID 的设备号将事务转发到对应的下游输出端口。 当请求类型为 CFG 配置请求时采用 ID 路由的方式。 如果请求类型为 TYPE1 配置请求, 当请求 ID 中的总线号等于配置空间中的下一级总线号时, 表示请求发往连接到该桥设备的下一级设备, 将TYPE1 类型请求转换为 TYPE0 请求转发到下游端口; 当请求 ID 总线号位于下游总线域时, 直接根据请求 ID 将事务转发到下游端口。 如果请求类型为 TYPE0 配置请求,当请求 ID 总线号等于上一级总线号时, 表示请求发送到本设备, 根据请求内容访问本设备配置空间, 读操作将生成 CplD, 从对应请求端口的输出端口发出。

图1 TLP 请求处理子程序流程图

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

审核编辑 黄宇

-

TLP

+关注

关注

0文章

37浏览量

16587 -

高速传输

+关注

关注

0文章

46浏览量

9321

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计30: NVMe 设备模型设计

NVMe高速传输之摆脱XDMA设计28: TLP 事务处 理程序的执行流程

NVMe高速传输之摆脱XDMA设计21:PCIe的TLP读处理

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

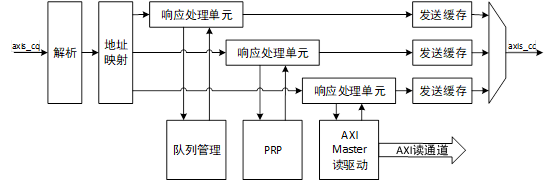

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

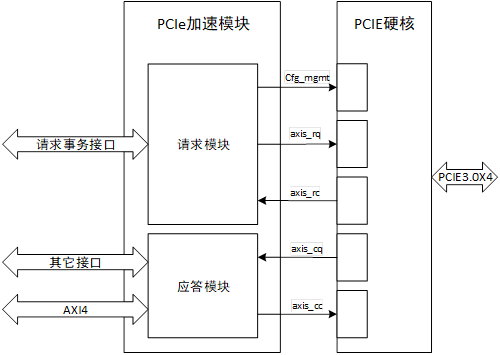

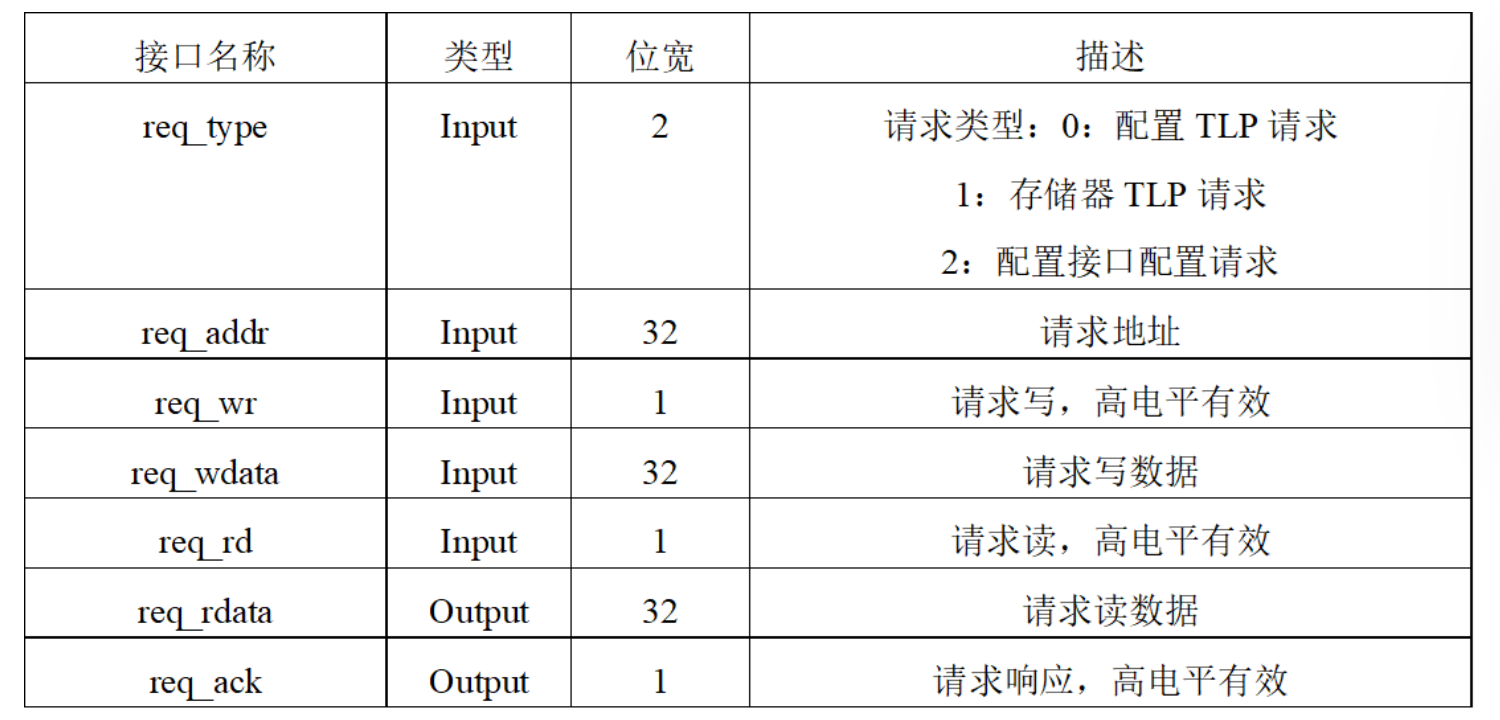

NVMe高速传输之摆脱XDMA设计17:PCIe加速模块设计

NVMe高速传输之摆脱XDMA设计16:TLP优化

NVMe高速传输之摆脱XDMA设计15:PCIe的TLP读处理

NVMe高速传输之摆脱XDMA设计15:PCIe的TLP读处理

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计29: TLP 请求处理流程

NVMe高速传输之摆脱XDMA设计29: TLP 请求处理流程

评论