深入解析TPS51116EVM评估模块:DDR内存供电的理想之选

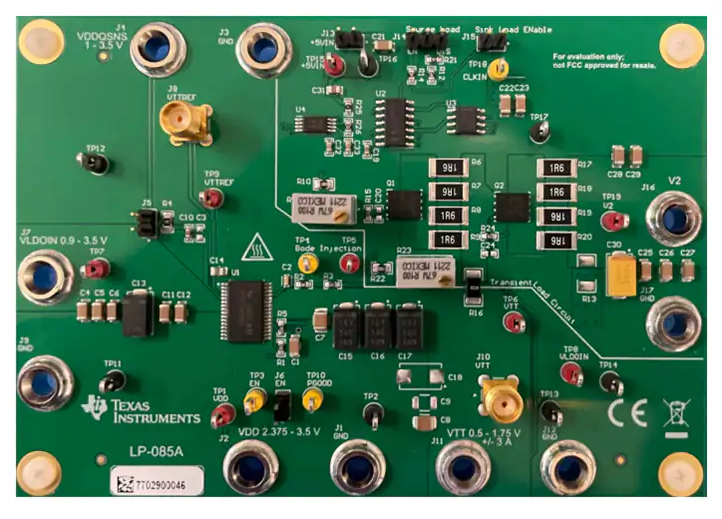

在电子工程师的日常工作中,为DDR内存模块设计高效、稳定的电源解决方案是一项常见且关键的任务。德州仪器(TI)的TPS51116EVM评估模块,为DDR、DDR2和DDR3内存模块提供了一个完整的电源解决方案。接下来,我们将详细探讨这个评估模块的特点、配置和性能。

文件下载:TPS51116EVM-001.pdf

一、TPS51116EVM概述

TPS51116EVM是一款双输出转换器,专为DDR、DDR2和DDR3内存模块设计。它采用10 - A同步降压转换器为DDR内存模块提供核心电压(VDDQ)。该评估模块的供电电压范围为4.5 - 28 V,控制器偏置电源为4.75 - 5.25 V,这使得它既可以从单一的5 V电源启动,也能在较宽的电源电压范围内配合低功耗5 V偏置电源工作。

1.1 应用领域

1.2 功能特性

- VDDO开关稳压器输出效率高达85%

- 双开关稳压器/LDO输出,为DDR核心和端接电压供电

- 3 - A灌/拉端接电压LDO稳压器

- 10 - mA端接参考电压,用于DDR输入参考

- 用户可选择DDR、DDR2、DDR3或外部参考电源电压

- 用户可选择开关稳压器或外部电源作为LDO端接稳压器的电源

- 提供用于测试S3和S5睡眠状态的开关

二、电气性能规格

| 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| VVIN(电源电压) | - | 4.5 | - | 28 | V |

| VV5IN(逻辑电源电压) | - | 4.75 | - | 5.25 | V |

| VVDDQ(开关输出电压) - DDR模式 | - | 2.45 | 2.50 | 2.55 | V |

| VVDDQ(开关输出电压) - DDR2模式 | - | 1.75 | 1.80 | 1.85 | V |

| VVDDQ(开关输出电压) - DDR3模式 | - | 1.45 | 1.50 | 1.55 | V |

| VVDDQ(RIPp - p)(开关输出电压纹波) - DDR2模式,IDDQ = 10 A | - | 10 | - | 40 | mV |

| IVDDQ(开关输出电流) - IVTT = 0 A | - | 0 | - | 10 | A |

| VVTT(端接电压输出) - VVDDQSNS = VVDDQ | - | - | VVDDQ/2 | - | V |

| Vtt(tol)(VTT输出电压相对于VTTREF的公差) | - | -40 | - | 40 | mV |

| Vttripple(p - p)(端接电压纹波) | - | 0 | - | 20 | - |

| Vtt_Ref(参考电压) - VVDDQSNS = VVDDQ | - | - | VVDDQ/2 | - | V |

| Vtt_Ref(tol)(参考电压公差) - IVTTREF < 10 mA | - | -10 | - | 10 | mV |

| η(开关输出效率) - IVTTREF = 0 mA,DDR2模式,IVDDQ = 10 mA,VIN = 12 V | - | 78% | - | - | - |

| η(开关输出效率) - IVTTREF = 0 mA,DDR2模式,IVDDQ = 1 A | - | - | 88% | - | - |

| η(开关输出效率) - IVTTREF = 0 mA,DDR2模式,IVDDQ = 7 A | - | - | 90% | - | - |

| η(开关输出效率) - IVTTREF = 0 mA,DDR2模式,IVDDQ = 10 A | - | - | 88% | - | - |

三、原理图与配置

3.1 跳线功能

| 标准的100 - mil间距的跳线JP1 - JP4为用户提供了TPS51116EVM的配置选项。每个由三个或六个引脚组成的跳线组都配有一个100 - mil的分流器,用户可以通过它选择所需的操作模式。 | 跳线 | 选择 | 默认值 |

|---|---|---|---|

| JP1 | TPS51116 VDDQ放电方案,跟踪、非跟踪或无放电 | 跟踪 | |

| JP2 | TPS51116使用的电流传感模式 | RDS(on) | |

| JP3 | TPS51116使用的控制方案 | D - CAP模式 | |

| JP4 | 输出电平 - DDR、DDR2、DDR3或外部可调 | DDR2 |

3.2 睡眠状态开关

开关SW1和SW2分别用于选择S5和S3睡眠状态,用户可以通过它们观察TPS51116控制器对这些内存睡眠状态的反应。

3.3 电阻和短路

电阻R8和短路R9允许用户在无损RDS(on)和传统电阻电流传感之间进行选择。如果通过JP2选择电阻传感,则必须安装R8并移除R9;如果通过JP2选择RDS(on)传感,则必须安装R9,由于R9和R8并联,R8可以留在PCB上。

3.4 MOSFET选择

TPS51116EVM上使用的MOSFET Q1和Q2的值是为了在3 - 28 V的笔记本电源系统工作范围内优化开关稳压器的运行而选择的。在有稳压电源电压的应用中,可以优化MOSFET以减少损耗并提高效率。

- 对于固定12 V电源的系统,高端MOSFET的低占空比有利于选择具有较高RDS(on)的MOSFET,以降低栅极电荷和加快开关时间。TI推荐使用Vishay SI4390作为Q1,SI4378作为Q2或等效的MOSFET。

- 对于开关稳压器和TPS51116的VDD电压都使用单一5 V电源轨的应用,高端MOSFET的占空比较高,因此适合选择具有较低RDS(on)和稍高栅极电荷的MOSFET。TI推荐将Vishay SI4378用于Q1和Q2。

四、配置模式

4.1 用户可选择的配置模式

TPS51116EVM通过四个跳线块、两个开关和三个电阻来调整配置。需要注意的是,不要将跳线安装在非指定位置。

4.2 JP1跟踪放电模式

TPS51116EVM预配置为跟踪放电模式。在该模式下,当TPS51116通过打开S3和S5开关设置为放电时,它会关闭两个MOSFET,并通过内部MOSFET从VDDQ输出缓慢吸收电流。要将评估模块编程为跟踪放电模式,需将JP1跳线设置到较低的垂直位置。

4.3 JP1非跟踪放电模式

要使TPS51116EVM在非跟踪放电模式下运行,TPS51116必须设置为自驱动LDO电源电压模式,因为它会从VDDQ输出吸收高达3 A的电流,直到VVDDQ放电至300 mV。如果使用外部LDO电源,选择非跟踪放电模式可能会损坏TPS51116EVM。要将评估模块编程为非跟踪放电模式,需将JP1跳线设置到较高的垂直位置。

4.4 JP1无放电模式

在无放电模式下,TPS51116只需关闭电源MOSFET,让输出由负载或输出电容的自放电来放电。要将评估模块编程为无放电模式,需将JP1跳线设置到中心水平位置。

4.5 JP2 RDS(on)电流传感

TPS51116EVM预配置为无损RDS(on)电流传感模式。在该模式下,它使用低端MOSFET(Q2)的正向电压降来监测电感电流。如果检测到故障,输出电压会随着输出电流的增加而下降;如果检测到严重的过流故障,会触发欠压比较器。要进行RDS(on)过流传感,需在R9处放置一个0 - Ω电阻或短路,并将JP2跳线设置到较低位置。

4.6 JP2电阻电流传感

TPS51116EVM也可以配置为电阻电流传感模式。在该模式下,它通过R8上的电压降来传感电感电流。与RDS(on)电流传感模式一样,TPS51116会限制输出电流,使VVDDQ下降并触发欠压比较器输出。要将评估模块编程为电阻电流传感模式,需确保在R8位置安装2 - W、6 mΩ的电阻,移除R9位置的任何电阻,并将JP2设置到较高位置。

4.7 JP3 D - CAP控制模式

TPS51116EVM预配置为TI的D - CAP模式。这种自适应恒定导通时间半滞回控制方案结合了固定频率稳态操作和滞回控制的快速瞬态响应的优点,并具有最小关断时间,以防止电感饱和或100%占空比操作。要将评估模块编程为D - CAP控制模式,需将JP3设置到较高位置。

4.8 JP3电流模式控制

TPS51116EVM也可以配置为更传统的电流模式控制。在该模式下,跨导放大器的输出连接到补偿网络。要将评估模块编程为电流模式控制,需将JP3设置到较低位置。

4.9 JP4 DDR模式

要使TPS51116EVM在DDR模式下运行,需将开关稳压器输出电压(VVDDQ)设置为2.5 V,LDO端接电压(VVTT)设置为1.25 V。要将评估模块编程为DDR模式,需将JP4跳线放置在中心垂直位置。

4.10 JP4 DDR2模式

TPS51116EVM预配置为DDR2模式,将开关稳压器输出电压(VVDDQ)设置为1.8 V,LDO端接电压(VVTT)设置为0.9 V。要将评估模块编程为DDR2模式,需将JP4跳线放置在右侧水平位置。

4.11 JP4 DDR3或可调输出电压

TPS51116EVM可以配置为DDR3或可调输出模式,用户可以通过选择R10和R11分压器并使用内部750 - mV参考来将VVDDQ设置在1.5 - 3.0 V之间。VTT输出电压会跟踪该可调电压。默认的R10和R11值提供DDR3电压电平,将开关稳压器电压(VVDDQ)设置为1.5 V,LDO端接电压(VVTT)设置为0.75 V。要将评估模块编程为可调输出电压模式,需将JP4跳线放置在左侧水平位置。

4.12 自驱动LDO电源电压

TPS51116EVM预配置为自驱动LDO电源电压模式。在该模式下,LDO直接由VVDDO开关稳压器的输出供电,无需外部电源电压。要将评估模块编程为自驱动LDO电源电压,需在R1位置放置一个短路。

4.13 外部LDO电源电压

TPS51116EVM也可以配置为外部LDO电源电压模式。在该模式下,LDO由TPS51116以外的外部电压源供电,用户可以通过移除R1位置的0 - Ω电阻并将外部电源应用到评估模块板上的LDOIN_EX引脚(J1)来选择另一个电源轨为VLDOIN供电。

五、测试设置

5.1 DC电源(VIN)

VIN应是一个能够提供0 - 30 VDC和0 - 10 A电流、功率处理能力至少为35 W的DC电压源。VIN应连接在引脚VIN和VIN_GND之间,为开关稳压器供电。

5.2 5 - V DC电源(VDD)

VDD应是一个能够提供5 V、500 mA电流、功率处理能力至少为2.5 W的DC电压源。VDD应连接在引脚V5IN和V5IN_GND之间,为TPS51116提供工作电流,为S3和S5睡眠状态开关以及JP1 - JP4配置跳线供电。

5.3 端接电压源(VTT)

VTT源用于测试VTT LDO的灌电流能力。VTT必须能够在5 V下提供3 A的电流。应在VTT上串联一个二极管,以防止电流流入VTT。VTT应连接在引脚Vtt和Vtt_GND之间。VTT和LOAD3绝不能同时通电。

5.4 核心电压负载(LOAD1)

LOAD1应是一个设置为恒流模式的电子负载,能够在2.5 V(DDR模式)或1.8 V(DDR2模式)下吸收0 - 10 A的电流。LOAD1应连接在引脚VDDQ和VDDQ_GND之间。

5.5 端接电压负载(LOAD2)

LOAD2应是一个设置为恒流模式的电子负载,能够在1.25 V(DDR模式)或0.9 V(DDR2模式)下吸收0 - 3 A的电流。LOAD2应连接在引脚Vtt和Vtt_GND之间。LOAD2和VTT绝不能同时通电。

5.6 存储单元参考电压负载(LOAD3)

LOAD3应是一个电子或电阻负载,从1.25 V(DDR模式)或0.9 V(DDR2模式)的VTTREF吸收小于10 mA的电流。LOAD3应连接在引脚Vtt_Ref和V5IN_GND之间。

5.7 风扇

由于该转换器的一些组件在运行时会发热,且评估模块未封闭以便探测电路节点,因此建议使用一个能够提供200 - 400 LFM风量的小风扇来降低组件温度。

六、上电/下电测试程序

6.1 准备工作

在ESD工作站工作,确保在给评估模块通电之前,将任何腕带、靴带或垫子连接到接地参考点。同时,应佩戴静电服和安全眼镜。

6.2 连接设备

按照原理图连接电源、负载、电压表和电流表。

6.3 设置跳线

根据所需的操作配置设置100 - mil分流跳线。注意,在操作过程中不要尝试更改跳线设置。

6.4 初始状态设置

确保S3和S5设置为S4/S5状态,以确保在施加输入电压之前输出初始处于禁用状态。

6.5 上电过程

- 将VDD从0 VDC增加到5 VDC,使用V3验证VDD电压在4.75 - 5.25 V之间。

- 将VIN从0 VDC增加到12 VDC,使用V1验证VIN电压在11 - 13 V之间。

- 将S3和S5切换到S0状态以启用输出。

6.6 负载测试

- 将LOAD1从0 ADC变化到10 ADC。

- 在启动LOAD2之前,确保VTT关闭。

- 将LOAD2从0 A变化到3 A(在仪表A5上为0 A到 - 3 A),以测试LDO的源电流能力。

- 在打开VTT之前,将LOAD2设置为0 A。

- 改变VTT,使A5在0 A到 + 3 A之间变化,以测试LDO的灌电流能力。

- 将LOAD3从0 mA变化到10 mA,但不要超过10 mA。

- 将VIN从4.5 V变化到28 V。

- 将VDD从4.75 V变化到5.25 V。

- 使用S3和S5状态开关测试睡眠状态。

6.7 下电过程

- 将VIN增加到12 VDC。

- 将LOAD3减小到0 mA。

- 将LOAD2减小到0 A。

- 将LOAD3减小到0 A。

- 将VIN减小到0 V。

- 将VDD减小到0 V。

七、性能数据和特性曲线

7.1 效率

TPS51116EVM设计用于在从最大负载10 A到小于100 mA的非常轻负载的很宽负载电流范围内提供高效率。在非常轻负载下实现高效率非常重要,因为内存模块在空闲状态等待指令时消耗的电流非常少。

7.2 瞬态响应

TPS51116EVM使用TI的D - CAP控制模式,能够立即响应负载瞬态。在D - CAP模式下,它可以在单个开关周期内从标称占空比切换到最大占空比,并在输出电压恢复到调节值后立即返回标称占空

-

评估模块

+关注

关注

0文章

1753浏览量

8386

发布评论请先 登录

深入解析TPS51116EVM评估模块:DDR内存供电的理想之选

深入解析TPS51116EVM评估模块:DDR内存供电的理想之选

评论