ADS117L14(四通道)和ADS117L18(八进制)是 16 位、三角形 Σ (ΔΣ)、模数转换器 (ADC)。这些器件提供4个或8个通道的同步采样,数据速率高达512kSPS(宽带滤波器模式)和1365kSPS(低延迟滤波器模式)。24位ADS127L14(四通道)和ADS127L18(八进制)ADC是引脚兼容器件,可提高分辨率。

*附件:ads117l14.pdf

特性

- 同时测量四个或八个通道

- 宽带滤波器模式:高达 512kSPS

- 线性相位响应

- ±0.0004dB通带纹波

- 106dB阻带衰减

- 低延迟滤波模式:高达 1365kSPS

- 3.9μs 转换延迟

- 功率可扩展速度模式:

- 最大转速:21mW/ch (512kSPS/1365kSPS)

- 高速:16mW/ch (400kSPS/1067kSPS)

- 中速:9mW/ch (200kSPS/533kSPS)

- 低速:3mW/ch (50kSPS/133kSPS)

- 高精度:

- 200kSPS时的SNR:97.7dB(典型值)

- 总谐波差:–115dB(典型值)

- INL:0.5LSB(典型值)

- 失调漂移:60nV/°C(典型值)

- 增益漂移:1ppm/°C FSR(典型值)

- 预充电缓冲信号输入

- 双极或单极电源作

- ±VREF 或 ±2VREF 输入范围

- 可通过引脚设置或 SPI 进行编程

- 用于输出数据的帧同步端口

- 内部或外部时钟作

- 模拟电源电压:2.85V 至 5.5V

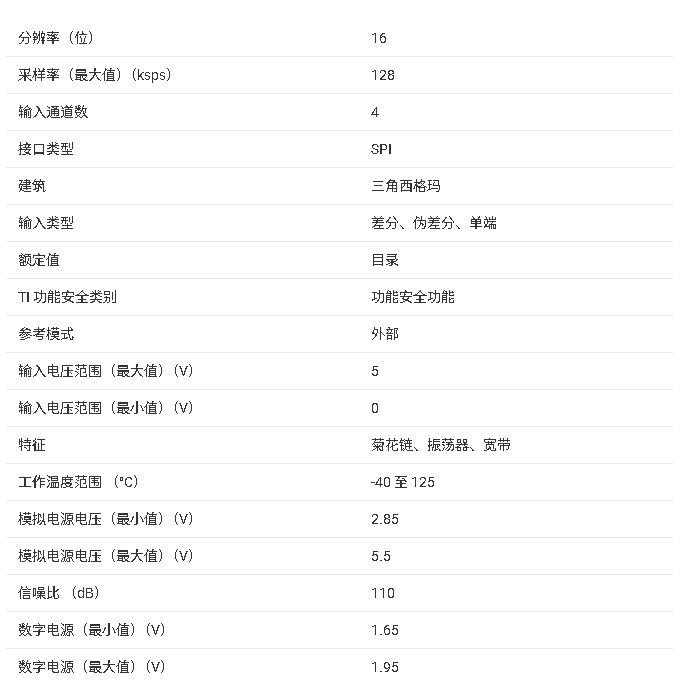

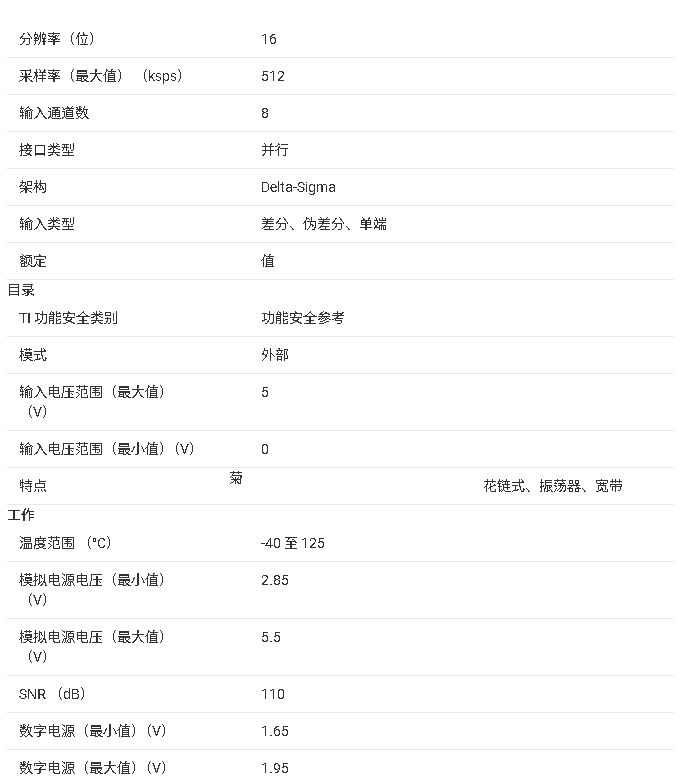

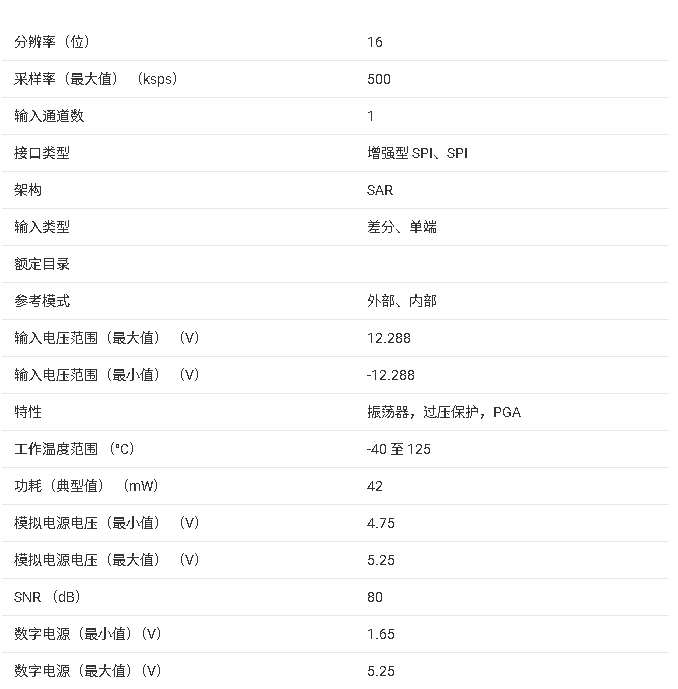

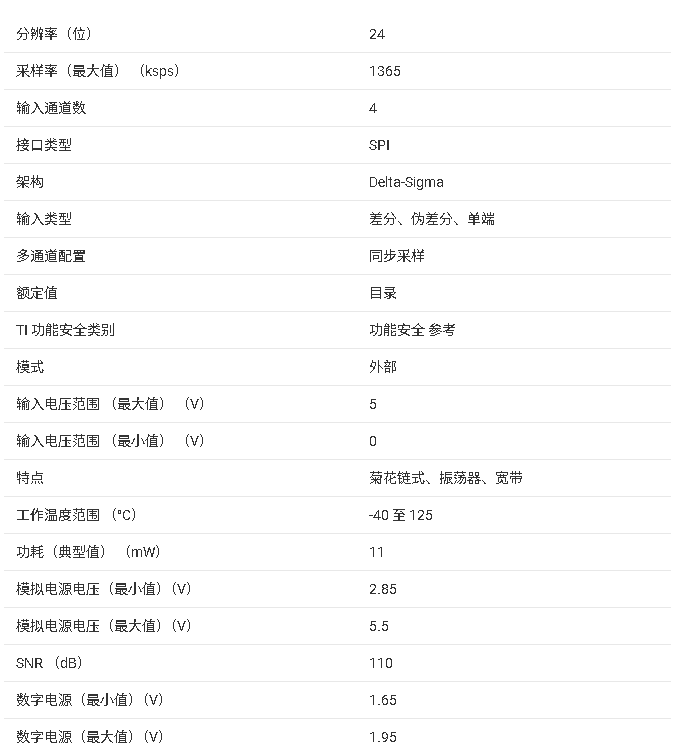

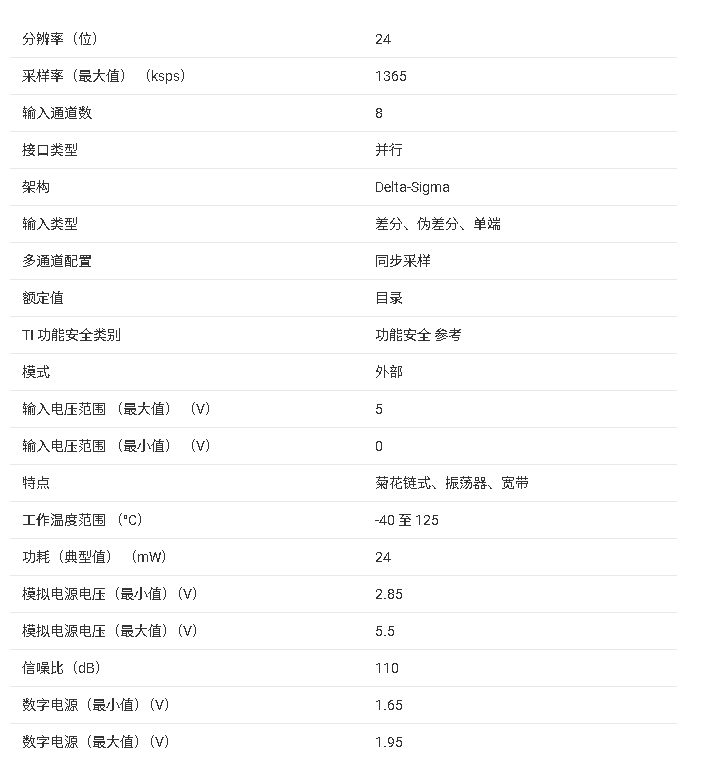

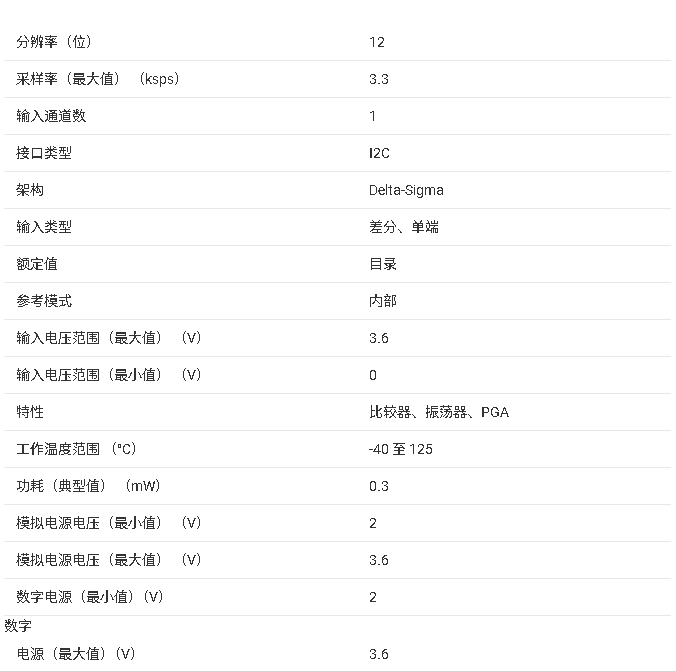

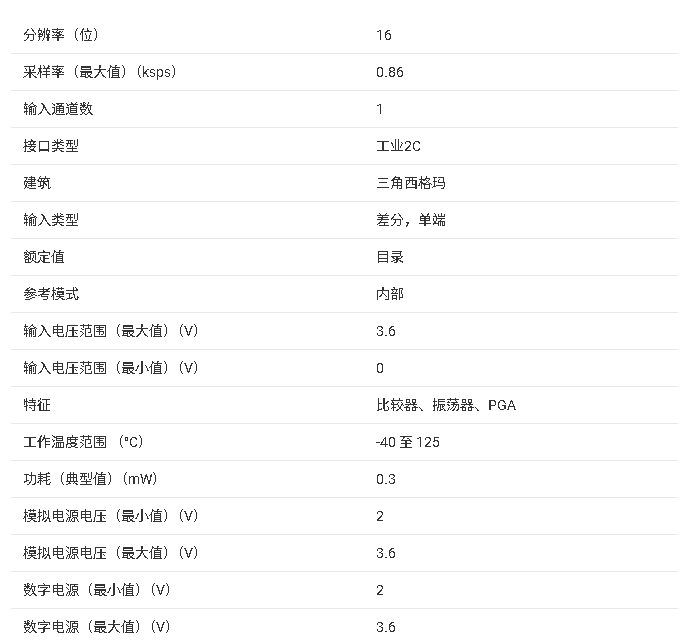

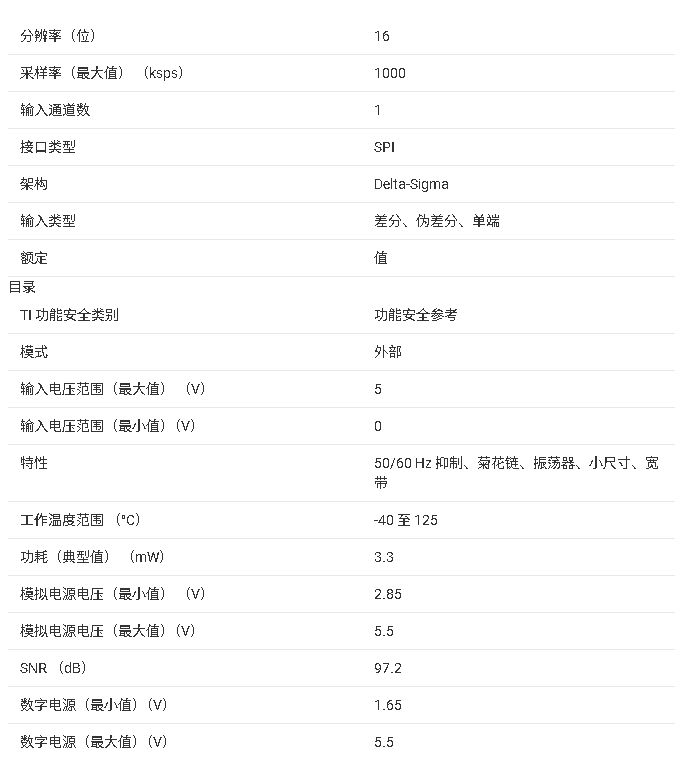

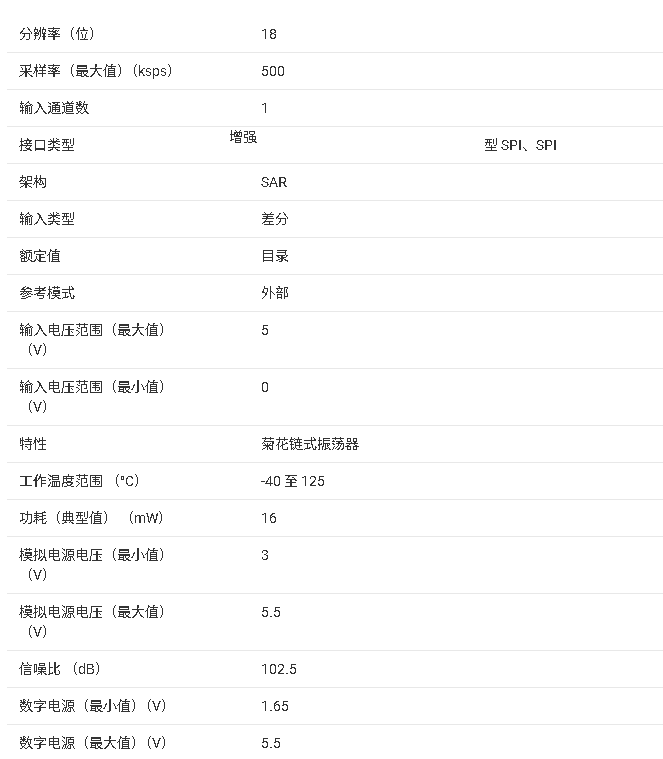

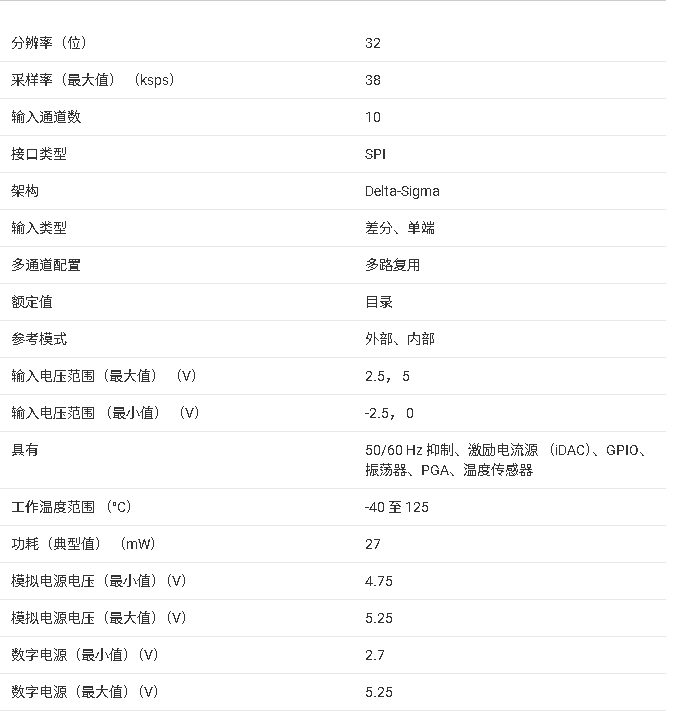

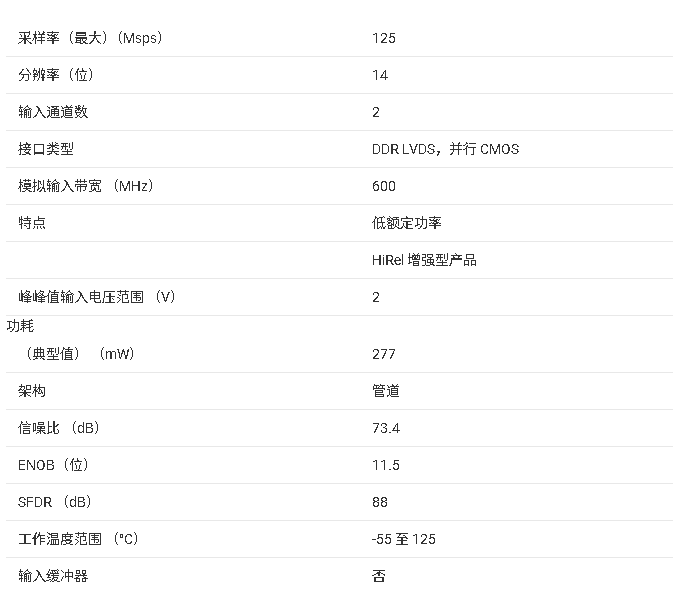

参数

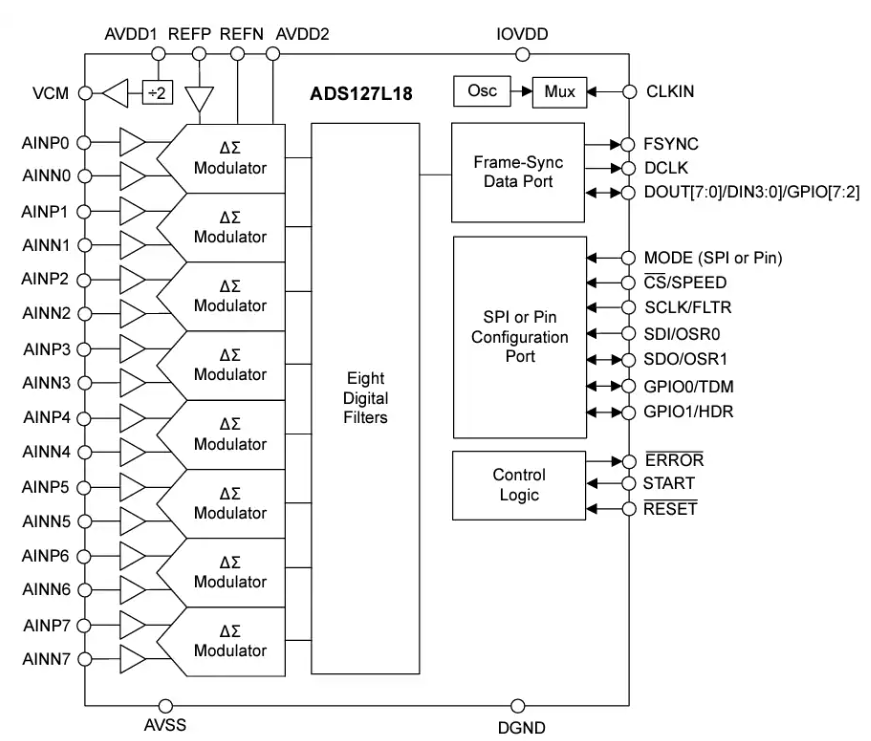

方框图

ADS117L14(4 通道)与 ADS117L18(8 通道)是 16 位 ΔΣ 架构同步采样模数转换器(ADC),支持最高 1365.3kSPS 数据率与宽频带信号处理,集成可编程滤波器、输入缓冲及多模式数据接口,适用于测试测量、工业自动化、航空航天等高精度多通道数据采集场景。

一、核心特性

1. 采样与信号性能

- 数据率与滤波器模式 :提供两种核心滤波模式,宽带滤波器(最高 512kSPS,线性相位、106dB 阻带衰减)适合交流信号,低延迟滤波器(最高 1365.3kSPS,3.9μs 转换延迟)适合直流信号;支持 4 档功率可缩放速度模式,功耗随数据率降低而减少(如低速模式单通道功耗低至 3mW)。

- 精度指标 :200kSPS 时信噪比(SNR)典型值 97.7dB,总谐波失真(THD)低至 - 115dBc,积分非线性(INL)±1LSB,失调漂移 60nV/℃,增益漂移 1ppm/℃,确保宽温范围(-40℃至 125℃)内的高精度测量。

- 输入范围与缓冲 :支持 ±VREF 或 ±2VREF 差分输入范围,集成输入预充电缓冲器,可降低输入电流(缓冲开启时典型 ±0.4μA)与采样噪声,适配低带宽信号驱动场景。

2. 集成功能模块

- 可编程数字滤波器 :宽带滤波器提供 1x-256x 过采样比(OSR),阻带衰减 106dB;低延迟滤波器含 sinc4、sinc4+sinc1 等 4 种拓扑,支持 50/60Hz 工频噪声抑制(NMRR 达 100dB)。

- 校准与诊断 :每通道配备 24 位偏移与增益校准寄存器,支持硬件 / 软件复位;集成 CRC 校验(SPI 接口与寄存器映射)、调制器饱和检测(MOD_FLAG)及电源电压监控(ALV_FLAG),提升系统可靠性。

- 参考电压管理 :支持 0.5-2.75V(低范围)或 1V-AVDD1(高范围)差分参考输入,可选 REFP 缓冲器降低参考端负载,VCM 引脚提供(AVDD1+AVSS)/2 的共模电压输出,用于外部放大器电平匹配。

3. 接口与同步能力

- 数据输出接口 :帧同步(Frame-Sync)接口支持 1/2/4/8 通道时分复用(TDM),可级联多器件( Daisy-Chain)减少数据 lanes;提供 FSYNC(帧时钟)与 DCLK(位时钟),数据格式支持二进制补码(双极性)或无符号二进制(单极性)。

- 配置与控制 :支持硬件引脚配置( MODE 引脚选择,无需 SPI)或 SPI 编程(16 位命令帧,可选 CRC 校验);START 引脚实现多通道同步采样,RESET 引脚支持手动复位,GPIO 引脚可复用为数据接口或控制信号。

二、适用场景

凭借多通道同步采样、高信噪比及宽温特性,两款芯片主要应用于以下领域:

- 测试测量 :数据采集(DAQ)、振动分析仪、声学检测设备,利用同步采样与高 SNR 实现多通道信号精准捕获。

- 工业自动化 :设备状态监控、电机控制,通过低延迟滤波与抗干扰能力,实时反馈设备运行参数。

- 航空航天与医疗 :声呐系统、脑电图(EEG),依托宽温工作范围(-40℃至 125℃)与低失真特性,适配恶劣环境与高精度生物信号采集。

- 电网基础设施 :电能质量分析仪,支持 50/60Hz 工频噪声抑制,准确测量电压、电流谐波与功率参数。

三、硬件设计要点

1. 电源与时钟设计

- 电源需求 :需多组独立电源,模拟电源 AVDD1(2.85-5.5V)、AVDD2(1.74-5.5V),数字电源 IOVDD(1.65-1.95V),负电源 AVSS(可接地或负压,如 - 2.5V 实现双极性输入);每个电源引脚需并联 2.2μF+0.1μF 低 ESR 电容,CAPA/CAPD 引脚(内部稳压器输出)需 10μF/2.2μF 旁路电容。

- 时钟配置 :支持内部振荡器(25.6MHz,仅推荐直流测量)或外部时钟(0.5-33.66MHz),时钟分频器(1/2/3/4/8 倍)可调整 ADC 核心时钟;外部时钟需低抖动(如 100kHz 信号允许≤50ps RMS 抖动),避免 SNR 性能退化。

2. 布局与布线准则

- 信号隔离 :模拟输入(AINP/AINN)、参考电压(REFP/REFN)需差分走线(阻抗 100Ω,长度匹配误差≤5mil),与数字信号(SPI、Frame-Sync)间距≥2mm,避免串扰。

- 地平面处理 :模拟地(AGND)、数字地(DGND)单点连接,时钟地(VSSCLK)独立布局;散热焊盘需通过至少 4 个过孔连接至接地平面,PCB 铜皮面积不小于封装(7mm×7mm VQFN)2 倍,控制结温(Tj)≤150℃。

- 抗混叠滤波 :输入需外接低通滤波器(如 4 阶 RC),抑制调制器采样频率(fMOD)附近的带外信号,避免混叠(如 fMOD=12.8MHz 时,需 90dB 衰减以确保信号纯净)。

3. 初始化与配置

- 模式选择 :MODE 引脚接 IOVDD 进入 SPI 模式(灵活配置所有参数),接地 / 悬空进入硬件模式(通过引脚 strap 配置速度、滤波器类型);硬件模式下默认外部时钟、高参考范围、VCM 输出使能。

- 同步与校准 :START 引脚提供多通道同步触发,需确保触发信号周期为 DACLK 周期整数倍;校准流程为:短接输入测偏移→施加已知信号测增益→写入 24 位校准寄存器,校准后误差可降至 ±0.1% FSR 以内。

四、工作模式与性能优化

1. 核心工作模式

- 同步控制模式 :START 引脚上升沿触发同步采样,后续采样持续进行,支持连续时钟触发以维持多通道时序对齐。

- 启停控制模式 :START 引脚高电平启动采样,低电平停止(当前转换完成后终止),适合单次 / 间歇采样场景,需注意停止前需提前 24 个 DACLK 周期置位 STOP 信号。

- 掉电与待机 :支持单通道掉电(CHn_PWDN)或全局待机模式,掉电通道输出最后一次采样值,待机模式下模拟部分断电以降低功耗(待机电流典型 60μA)。

2. 性能优化手段

- 噪声抑制 :开启输入缓冲器(CHn_BUFP/CHn_BUFN)降低输入噪声,选择合适 OSR(如 OSR=64 时噪声典型 7.2μV RMS);模拟电源端并联 10nF 高频电容,抑制开关噪声。

- 失真控制 :输入信号幅度控制在 FSR 的 90% 以内,避免调制器饱和(MOD_FLAG 置位);参考电压端使用低噪声基准(如 REF6041),并靠近 ADC 布局以减少布线损耗。

- 接口优化 :Frame-Sync 接口采用 TDM 模式减少数据 lanes(如 8 通道可压缩至 1 lane),级联时需确保所有器件时钟分频比为 1,且同步触发信号延迟一致。

五、可靠性与封装

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

滤波器

+关注

关注

162文章

8481浏览量

186388 -

adc

+关注

关注

100文章

7951浏览量

557052 -

模数转换器

+关注

关注

26文章

4105浏览量

130283 -

数据速率

+关注

关注

0文章

60浏览量

12318

发布评论请先 登录

相关推荐

热点推荐

ADS117L11 400 kSPS、宽带宽、16位、Δ-ΣADC数据表

电子发烧友网站提供《ADS117L11 400 kSPS、宽带宽、16位、Δ-ΣADC数据表.pdf》资料免费下载

发表于 07-16 09:50

•0次下载

Texas Instruments ADS127L18 24 位模数转换器数据手册

Texas Instruments ADS127L18 24位模数转换器(ADC)是基于单通道 ADS127L11的Δ-Σ 器件。这些器件可对八个通道进行采样,数据速率高达512kSPS(宽带滤波器

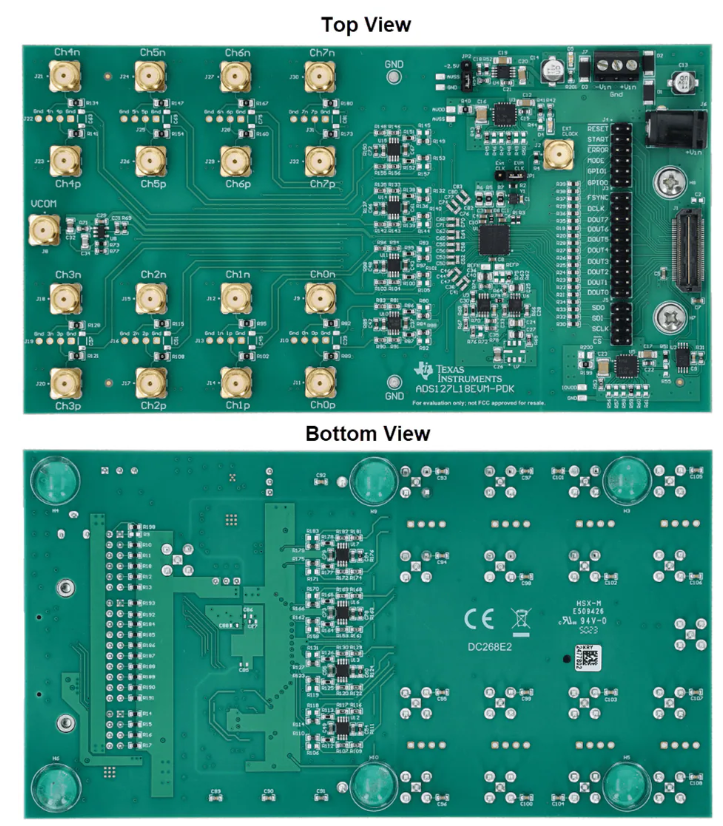

Texas Instruments ADS127L18EVM-PDK 评估模块(EVM)数据手册

Texas Instruments ADS127L18EVM-PDK 评估模块 (EVM) 是一个评估 ADS127L18 性能的平台。ADS127L18是一款八通道、24位、同步采样ΔΣ模数转换器

ADS117L18 512kSPS、16位、8通道、同步采样、宽带宽、Δ-Σ ADC技术手册

ADS117L14(四通道)和ADS117L18(八进制)是 16 位、三角形 Σ (ΔΣ)、模数转换器 (ADC)。这些器件提供4个或8个通道的同步采样,数据速率高达512kSPS(宽带滤波器模式)和1365kSPS(低延迟滤波器模式)。

ADS8681W/ADS8685W/ADS8689W 核心信息总结

ADS8681W、ADS8685W和ADS8689W是基于逐次逼近(SAR)模数转换器(ADC)拓扑的集成数据采集系统系列。这些器件具有高速、高精度 SAR ADC、集成差分模拟前端 (AFE

ADS127L14/ADS127L18 ADC 产品文档总结

ADS127L14(四通道)和ADS127L18(八进制)是基于单通道[ADS127L11](https://www.ti.com/lit/pdf/SBAS946)的24位、增量Σ(ΔΣ)模数转换器

ADS127L18四通道 / 八通道同步采样 24 位 ADC 产品文档总结

ADS127L14(四通道)和ADS127L18(八进制)是基于单通道[ADS127L11](https://www.ti.com/lit/pdf/SBAS946)的24位、增量Σ(ΔΣ)模数转换器

ADS1014L/ADS1015L 系列模数转换器技术文档总结

ADS1014L和ADS1015L (ADS101xL) 是精密、低功耗、12 位、I2C 兼容的模数转换器 (ADC),采用超小型 12 引脚 DSBGA 和 10 引脚 VSSOP 封装

ADS1114L/ADS1115L 系列模数转换器技术文档总结

ADS1114L和ADS1115L (ADS111xL) 是精密、低功耗、16 位、I2C 兼容的模数转换器 (ADC),采用超小型 12 引脚 DSBGA 和 10 引脚 VSSOP 封装

ADS117L11 技术文档总结

该ADS117L11是一款 16 位 Δσ 模数转换器 (ADC),使用宽带滤波器的数据速率高达 400 kSPS,使用低延迟滤波器的数据速率高达 1067 kSPS。该器件将交流性能和直流精度完美

ADS891xB 系列 18 位高精度 SAR ADC 核心信息总结

ADS8910B、ADS8912B和ADS8914B (ADS891xB)属于引脚到引脚兼容、高速、单通道、高精度、18位逐次逼近寄存器(S

ADS127L01 24 位高速宽带 ADC 核心信息总结

该ADS127L01是一款 24 位、三角积分 (ΔΣ)、带数据的模数转换器 (ADC) 速率高达 512 kSPS。该器件提供了出色的直流精度和 出色的交流性能。高阶斩波稳定调制器实现了极低的漂移

ADS1262/ADS1263 产品核心信息总结

ADS1262和ADS1263 (ADS126x)是低噪声、低漂移、38.4kSPS、三角积分 (ΔΣ) ADC,集成了PGA、基准电压源和内部故障监控器。该ADS1263集成了一个用

ADS4245-EP 核心产品信息总结

该ADS4245是ADS42xx超低功耗系列双通道14位模数转换器(ADC)的低速变体。采用创新的设计技术实现高动态性能,同时在 1.8V 电源下消耗极低的功耗。这种拓扑结构使ADS4

ADS117L14/ADS117L18 核心信息总结

ADS117L14/ADS117L18 核心信息总结

评论