1AMD EV系列器件介绍

近年来,随着音视频应用场景和内容越来越丰富,对网络传输和存储都带来了巨大的挑战。为了应对这一挑战,各种视频编解码技术就被提了出来,其中H.264/H.265视频编解码协议是当前的主流视频编解码标准。AMD的ZYNQ MPSOC EV系列器件,是ZYNQ MPSOC集成了H.264/H.265 Video Codec Unit (VCU)硬核的一个系列器件。

▎该系列器件支持多标准编码/解码支持,包括:

• ISO MPEG-4第10部分:高级视频编码(AVC)/ITU H.264

• ISO MPEG-H第2部分:高效视频编码(HEVC)/ITU H.265

• HEVC:Main、Main Intra、Main10、Main10 Intra、Main 42 10、Main 42 10 Intra〔直到Level 5.1 (High Tier)〕

• AVC:Baseline、Main、High、High10、High 42、High10 Intra、High 42 Intra(直到Level 5.2)

▎支持多达32个流的同步编码和解码(最大聚合带宽为3840×2160 @ 60fps)

▎低时延速率控制

▎灵活的速率控制:CBR、VBR和常量QP

▎支持分辨率高达4K UHD @ 60 Hz的同步编码和解码

▎支持8 K UHD(~15 Hz)的降低帧速率

2VCU IP简介

LogiCORE IP H.264/H.265 Video Codec Unit (VCU)核支持多标准视频编码和解码,包括支持符合H.264标准的高效视频编码(HEVC)和高级视频编码(AVC)。这个单元可提供编码(压缩)和解码(解压缩)功能,并且能够同时编码和解码。

编码器块简介

编码器引擎被设计来用HEVC和AVC标准对视频流进行处理。它全面支持这些标准,包括支持8位和10位颜色、Y-only(单色)、40和42色度格式以及高达4K UHD @ 60 Hz的性能表现。下图显示的是编码器块的顶层接口和详细架构。编码器还包含多个全局寄存器、一个中断控制器和一个定时器。编码器由微控制器(MCU)子系统控制。

在PS上运行的VCU应用通过VCU control software API与编码器微控制器进行交互。微控制器固件(MCU Firmware)不是用户可修改的。APU通过32位的AXI4-Lite接口来控制MCU(以配置编码参数)。两个128位的AXI4主接口用于将视频数据和元数据移入、移出系统存储器。32位的AXI4主接口用于获取MCU软件(指令高速缓存接口)并加载或存储附加的MCU数据(数据高速缓存接口)。

APU通过32位AXI4-Lite接口控制MCU,完成编码参数配置。

两个128位AXI4主接口负责视频数据和元数据的系统存储器移入与移出。

32位AXI4主接口用于获取MCU软件(指令高速缓存接口),并加载或存储附加MCU数据(数据高速缓存接口)。

编码器块包含压缩引擎、控制寄存器、中断控制器,以及带存储器控制器的可选编码器缓存(缓存连接可编程逻辑中的UltraRAM或BlockRAM,通过寄存器启用)。

MCU的AXI-4主接口与解码器的相应AXI-4主接口多路复用,复用器输出可用于嵌入式VCU。

解码器块简介

解码器块可处理HEVC和AVC标准视频流,全面兼容两项标准,支持8位和10位颜色深度、Y-only(单色)、40及42色度格式,性能最高可达4K UHD @ 60 Hz,内部包含多个全局寄存器、中断控制器和定时器。

解码器由MCU子系统控制,APU通过32位AXI4-Lite从接口实现控制MCU,相关交互逻辑与编码器一致(APU上的VCU应用通过赛灵思VCU Control Software API与解码器微控制器交互,MCU不可由用户修改)。具体接口与结构特性如下:

两个128位AXI4主接口负责视频数据和元数据的系统存储器移入与移出。32位AXI4主接口用于获取MCU软件(指令高速缓存接口),并加载或存储附加MCU数据(数据高速缓存接口)。

解码器块包含H.265/H.264解压缩引擎、控制寄存器、中断控制器块,以及桥接单元和一组内部存储器(桥接单元用于管理解码器所需外部存储器访问的仲裁请求、突发地址和突发长度)。

系统CPU通过32位AXI-Lite从接口控制MCU,完成解码器参数配置、视频帧处理启动及状态与结果获取。

两个128位AXI-4主接口负责视频输入数据的获取和视频输出数据的存储(均与系统存储器交互)。

AXI-4主接口同时用于获取MCU软件,并对其他MCU数据执行加载或存储操作。

3VCU软件架构

视频编解码器单元(VCU)软件堆栈具有软件开发者可在多个抽象层级进行编程的分层架构,如下图所示。从高层到低层的应用接口如下所列:

GStreamer

OpenMAX Integration Layer

VCU Control Software

各层级核心说明如下:

GStreamer是跨平台开源多媒体框架,提供集成多个多媒体组件、创建流水线的基础架构,其支持OpenMAX Integration Layer API。

OpenMAX Integration Layer API定义了标准化媒体组件接口,助力开发者与平台提供商实现与硬件或软件多媒体编解码器的集成与通信。

VCU Control Software是VCU应用开发者可接触的最低级软件,所有VCU应用均需直接或间接使用AMD提供的该软件,其包含定制内核模块、定制用户空间库及AL_Encode和AL_Decode应用。

4VCU Control Software介绍

VCU Control Software是VCU应用开发人员可接触到的最低层级软件。它包含定制化内核模块、定制化用户空间库,以及ctrlsw_encoder和contrlsw_decoder应用程序。

下面的流程图详细定义了VCU Control Software中编码任务的执行链路,明确了缓冲区管理、编码流程控制、回调处理的协同逻辑,是开发者理解AL_Encoder API调用时序、资源管理机制的核心参考。

左侧主流程(main):涵盖编码器初始化(Initialize Encoder Settings)、实例创建(AL_Encoder_Create)、缓冲区分配(流缓冲区与源缓冲区的创建/入池)、数据填充、编码处理(AL_Encoder_Process)、任务销毁及资源释放等关键步骤,是编码任务从启动到结束的主线逻辑。

右侧回调流程:包含Unref Source callback(源缓冲区回池)、Unref Stream callback(流缓冲区回送编码器)、EndEncoding callback(编码结束后的资源释放与状态通知),用于处理编码过程中的异步回调与资源回收逻辑。

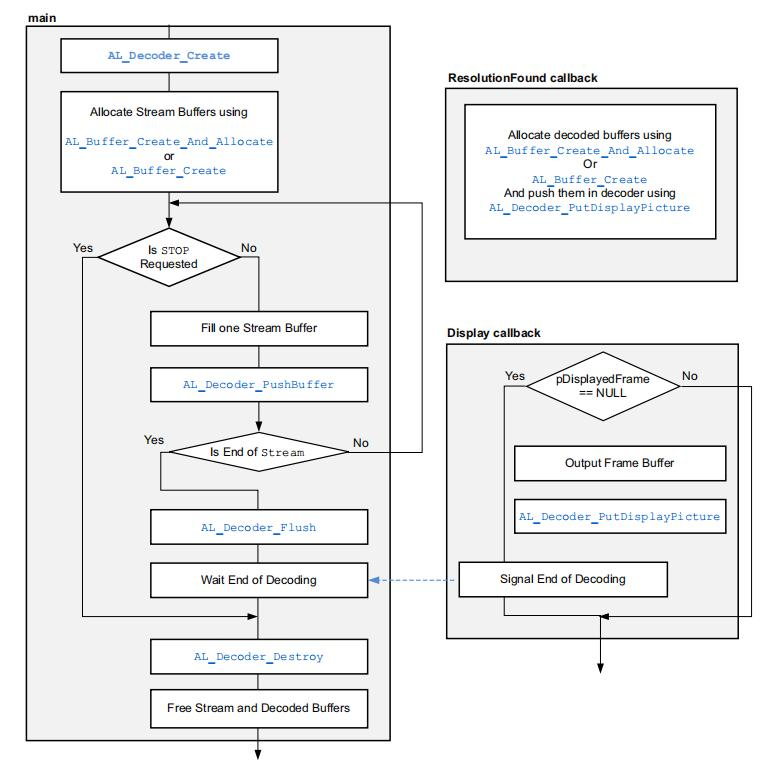

下面的流程图详细定义了VCU Control Software中解码任务的执行链路,明确了缓冲区管理、编码流程控制、回调处理的协同逻辑,是开发者理解AL_Decode API调用时序、资源管理机制的核心参考。

左侧主流程(main):包含解码器实例创建(AL_Decoder_Create)、流缓冲区分配(AL_Buffer_Create_And_Allocate或AL_Buffer_Create)、数据填充与推送(Fill one Stream Buffer、AL_Decoder_PushBuffer)、解码结束处理(AL_Decoder_Flush、Wait End of Decoding)、实例销毁及资源释放等关键步骤,是解码任务从启动到结束的主线逻辑。 右侧回调流程:ResolutionFound callback:用于在识别到视频分辨率后分配解码缓冲区(AL_Buffer_Create_And_Allocate或AL_Buffer_Create),并将其推入解码器(AL_Process_DisplayPicture)。 Display callback:处理解码后帧的输出逻辑,包含帧缓冲区判空、输出(Output Frame Buffer)、显示帧推送(AL_Decoder_PutDisplayPicture)及解码结束信号通知。

5VCU Control Software开发流程

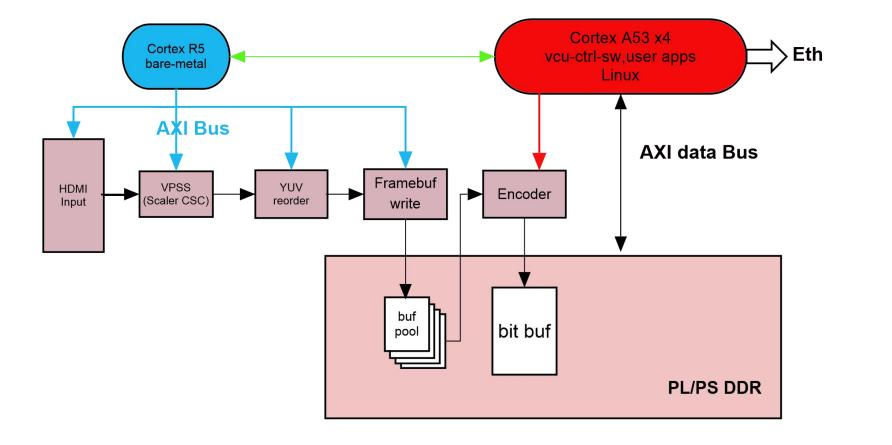

下面以AMD VCU Control Software参考设计为例,简要介绍control software的开发流程。该参考设计分为编码部分和解码部分。其中编码部分框图如下:

APU(四核Cortex A53)运行Linux系统,并搭载ctrlsw_encoder组件,负责帧缓冲区(framebuf)的写入缓冲控制、编码器控制,以及比特流文件写入和UDP流传输。

RPU(实时处理单元)/Microblaze运行裸机应用,负责采集流水线的初始化,具体包括:HDMI输入、VPSS(视频处理子系统)、YUV重排及帧缓冲区写入。解码部分框图如下:

APU(四核Cortex A53)运行Linux系统,并搭载ctrlsw_decoder组件,负责文件输入、解码器控制,以及混合器(Mixer)显示缓冲区地址指针配置。

RPU(Cortex R5)运行裸机应用,负责显示流水线的初始化,具体包括:帧缓冲区读取(Framebuf read)、YUV重排、混合器(Mixer)处理及HDMI输出。

Block Design设计

VCU配置

主要配置参数介绍

Coding Standard:选择AVC或HEVC,AVC:H264 HEVC:H265

Coding Type:选择要用于编码的GOP结构

- Intra Frame Only-仅限I帧

- Intra & Inter Frame-I帧、B帧和P帧

只有在选择Intra和Inter Frame时才能启用编码器的缓存。

Resolution:选择以下分辨率之一

- 1280×720

- 1920×1080

- 3840×2160

- 4096×2160

- 7680×4320

Frames Per Second:帧率选择,选择15、30、45或60 fps。在7680×4320分辨率下,只有15fps可用。

Color Format:选择以下颜色格式之一

- 40-单色

- 40

- 42

Color Depth:选择每通道8位或10位。

Use Encoder Buffer:选择是否要使用编码器缓存。只有在选择了Intra和Inter Frame之后才能启用编码器的缓存。编码器缓存通过缓存可编程逻辑中的数据来减少外部存储器的带宽,但它可能会略微降低视频的质量。

Memory Resource Type:选择下列存储器类型选项:

- URAM ONLY

- BRAM ONLY

- COMBINATION-URAM&BRAM

Max Number of Encoder Streams:选择1到8个流。

仅当“Basic Configuration”标签设置如下时,系统才会启用编码器缓存的高级配置选项:

▎“Coding Type”是“Intra & Inter Frame”

▎“Use Encoder Buffer”被选中

“Advanced Configuration”标签上的参数设置如下:

▎Manual Override:选择此选项可覆盖由IP集成器计算的编码器缓存存储器的大小。

▎Memory Depth (Kbytes):如果选中“Manual Override”复选框,则可以输入0到7,000Kbyte的存储器大小。

▎B Frame:选择以下选项之一:

NONE-最低时延

STANDARD-GOP配置IPPP(内部周期为30 ms)

▎Motion Vector Range:决定编码器缓存的大小:

LOW

MEDIUM

HIGH

▎CORE Clk (MHz):选择1-667 MHz的时钟频率

其余部分Block Design连接按照参考设计图所示添加并连接。

手动添加顶层封装文件zcu106_hdmirx_wrapper.v和约束文件vcu_hdmirx.xdc。只需点击“Generate Bitstream”按钮生成比特流。比特流生成完成后,选择“File->Export->Export Hardware”,导出供Vitis和Petalinux使用的XSA文件,注意需勾选“include bitstream”(包含比特流)选项。

Vitis流程

1、先使用之前从Vivado生成的XSA文件创建一个新平台。并添加新的应用项目名称(例如r5_hdmirx_yuv444),然后选择psu_cortexr5_0作为该应用项目的目标处理器。

2、修改R5的BSP设置,将uart1配置为标准打印输出。

3、将R5的源代码复制到src文件夹中。

4、右键点击r5_hdmirx_yuv444_system,选择“Build Project”,此步骤会生成 r5_hdmirx_yuv444.elf文件,该文件将用于Petalinux打包。

Petalinux流程

1、使用xilinx-vcu-zcu106-v2020.2-final.bsp创建Petalinux项目,具体可参考链接:

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/176914576/Zynq+UltraScale+MPSoC+VCU+TRD+2020.2+-+Run+and+Build+Flow

$ petalinux-create -t project -s xilinx-vcu-zcu106-v2020.2-final.bsp

2、在新建的Petalinux项目目录下,创建一个名为XSA的文件夹(示例),将之前从Vivado生成的.xsa文件复制到该文件夹中,然后通过该xsa文件配置Petalinux项目。

$ petalinux-config --get-hw-description=./XSA

3、进入配置界面后,在“Subsystem AUTO Hardware Settings”(子系统自动硬件设置)中,选择“Memory Settings”(内存设置),将系统内存大小(System Memory Size)设置为0x6FFFFFFF。

4、由于hdmirx、vphy、frmbuf_wr和vproc_ss等组件是在r5驱动,所以需要在petalinux设备数中将这些节点删除。

5、编译petalinux工程

$ petalinux-build

6、打包生成BOOT.bin文件,执行命令:

$ petalinux-package --boot --fsbl zynqmp_fsbl.elf --u-boot u-boot.elf --pmufw pmufw.elf --fpga system.bit --add r5_hdmirx_yuv444.elf --cpu=r5-0

至此,我们即完成了编码端的开发流程,解码端开发流程也和编码端类似。

关于安富利

安富利是全球领先的技术分销商和解决方案提供商,在过去一个多世纪里一直秉持初心,致力于满足客户不断变化的需求。通过遍布全球的专业化和区域化业务覆盖,安富利可在产品生命周期的每个阶段为客户和供应商提供支持。安富利能够帮助各种类型的公司适应不断变化的市场环境,在产品开发过程中加快设计和供应速度。安富利在整个技术价值链中处于中心位置,这种独特的地位和视角让其成为了值得信赖的合作伙伴,能够帮助客户解决复杂的设计和供应链难题,从而更快地实现营收。

-

amd

+关注

关注

25文章

5649浏览量

139049 -

编解码器

+关注

关注

0文章

279浏览量

25236 -

音视频

+关注

关注

4文章

572浏览量

31202 -

VCU

+关注

关注

17文章

86浏览量

21462

原文标题:AMD技术干货|AMD EV系列器件VCU Control Software简介

文章出处:【微信号:AvnetAsia,微信公众号:安富利】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【AMD】BIOS Engineer

【AMD】BIOS Engineer

AMD超威半导体热招 Senior Multi Media Diagnostics Software Engineer

【AMD社招】Graphics Driver Software Engineer

VCU(整车控制器)简介

AMD发布Radeon Software Adrenalin 21.10.3版驱动

AMD Software:Adrenalin Edition 2022版本发布

MPSoC VCU Ctrl-SW 2020.2编码不同Stride的YUV文件

P_数据表(S-1):HEV/EV Motor Control IP MILS Models

P_数据表(S-1):HEV/EV Motor Control IP MILS Models

AMD EV系列器件VCU Control Software简介

AMD EV系列器件VCU Control Software简介

评论