共读好书

本篇文章将探讨用于晶圆级封装(WLP)的各项材料,从光刻胶中的树脂,到晶圆承载系统(WSS)中的粘合剂,这些材料均在晶圆级封装中发挥着重要作用。

光刻胶(Photoresists, PR):由感光剂、树脂和溶剂构成,用于形成电路图案和阻挡层

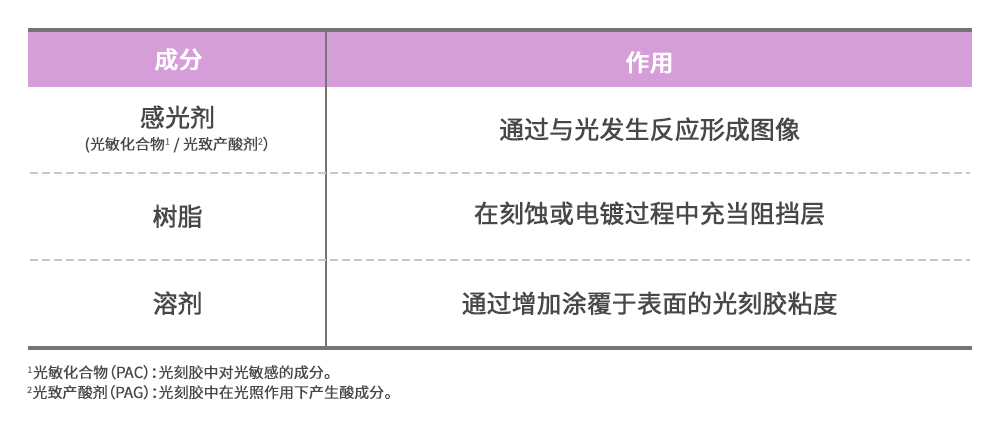

光刻胶是由可溶性聚合物和光敏材料组成的化合物,当其暴露在光线下时,会在溶剂中发生降解或融合等化学反应。在运用于晶圆级封装的光刻(Photolithography)工艺过程中时,光刻胶可用于创建电路图案,还可在后续电镀(Electroplating)¹过程中通过电镀金属丝以形成阻挡层。光刻胶的成分如图1所示。

¹电镀(Electroplating):一项晶圆级封装工艺,通过在阳极上发生氧化反应来产生电子,并将电子导入到作为阴极的电解质溶液中,使该溶液中的金属离子在晶圆表面被还原成金属。

▲ 图1:光刻胶的成分和作用(ⓒ HANOL出版社) 根据光照的反应原理,光刻胶可分为正性光刻胶(Positive PR)和负性光刻胶(Negative PR)。对于正性光刻胶,曝光区域会发生降解反应,导致键合减弱;而未曝光区域则会发生交联(Cross-linking)²反应,使键合增强。因此,被曝光部分在显影过程中会被去除。然而对于负性光刻胶,曝光部分会产生交联反应并硬化,从而被完整保留下来;未曝光部分则被去除。负性光刻胶的粘度通常高于正性光刻胶,旋涂过程中的涂覆厚度更厚,因而通常被用于形成较高的焊接凸点(Solder Bump)。而正性光刻胶则至少需要涂覆两次。 光刻过程中所使用的光源可根据波长进行分类,波长以纳米(nm)为单位。对于细微化(Scaling)的半导体而言,在光刻过程中通常采用波长较短的光源,以增强光刻效果,从而形成更精细的电路图案。因此,光敏化合物(PAC)用于制作曝光波长较长的g线(g-line)³光刻胶和i线(i-line)⁴光刻胶。而化学放大型抗蚀剂(CAR)⁵则用于制作曝光波长较短的光刻胶。晶圆级封装通常使用i线步进式光刻机(Stepper)⁶。 ²交联(Cross-link):通过化学键将聚合物链连接在一起的化学反应。

▲ 图1:光刻胶的成分和作用(ⓒ HANOL出版社) 根据光照的反应原理,光刻胶可分为正性光刻胶(Positive PR)和负性光刻胶(Negative PR)。对于正性光刻胶,曝光区域会发生降解反应,导致键合减弱;而未曝光区域则会发生交联(Cross-linking)²反应,使键合增强。因此,被曝光部分在显影过程中会被去除。然而对于负性光刻胶,曝光部分会产生交联反应并硬化,从而被完整保留下来;未曝光部分则被去除。负性光刻胶的粘度通常高于正性光刻胶,旋涂过程中的涂覆厚度更厚,因而通常被用于形成较高的焊接凸点(Solder Bump)。而正性光刻胶则至少需要涂覆两次。 光刻过程中所使用的光源可根据波长进行分类,波长以纳米(nm)为单位。对于细微化(Scaling)的半导体而言,在光刻过程中通常采用波长较短的光源,以增强光刻效果,从而形成更精细的电路图案。因此,光敏化合物(PAC)用于制作曝光波长较长的g线(g-line)³光刻胶和i线(i-line)⁴光刻胶。而化学放大型抗蚀剂(CAR)⁵则用于制作曝光波长较短的光刻胶。晶圆级封装通常使用i线步进式光刻机(Stepper)⁶。 ²交联(Cross-link):通过化学键将聚合物链连接在一起的化学反应。

³g线(g-line):在汞光谱中,一条对应波长约为436纳米的谱线。

⁴i线(i-line):在汞光谱中,一条对应波长约为356纳米的谱线。

⁵化学放大型抗蚀剂(CAR):一种用于提高光刻胶材料光敏性的抗蚀剂。

⁶步进式光刻机(Stepper):用于曝光晶圆的设备。不同类型的设备用于不同精度晶圆的曝光,具体取决于对应的光源类型。

电镀液:由金属离子、酸和添加剂组成,用于可控电镀工艺

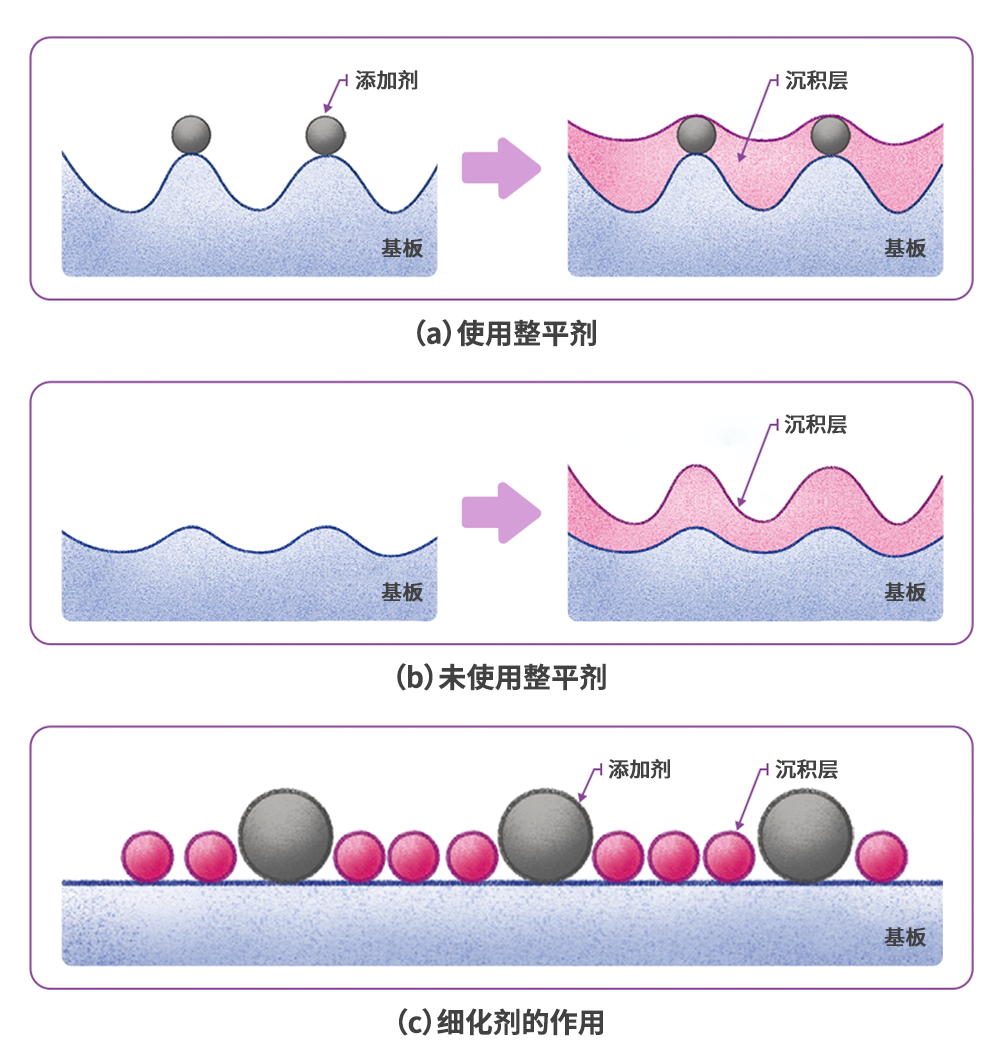

电镀液(Plating Solution)是一种在电镀过程中使用的溶液,由金属离子、酸和添加剂组成。其中,金属离子是电镀过程中的待镀物质;酸作为溶剂,用于溶解溶液中的金属离子;多种添加剂用于增强电镀液和镀层的性能。可用于电镀的金属材料包括镍、金、铜、锡和锡银合金,这些金属以离子的形式存在于电镀液中。常见的酸性溶剂包括硫酸(Sulfuric Acid)和甲磺酸(Methanesulfonic Acid)。添加剂包括整平剂(Leveler)和细化剂(Grain Refiner),其中,整平剂用于防止材料堆积,提高电镀层平整性;而晶粒细化剂则可以防止电镀晶粒的横向生长,使晶粒变得更加细小。

▲ 图2:电镀液中添加剂的作用(ⓒ HANOL出版社)

▲ 图2:电镀液中添加剂的作用(ⓒ HANOL出版社)

光刻胶剥离液(PR Stripper):使用溶剂完全去除光刻胶

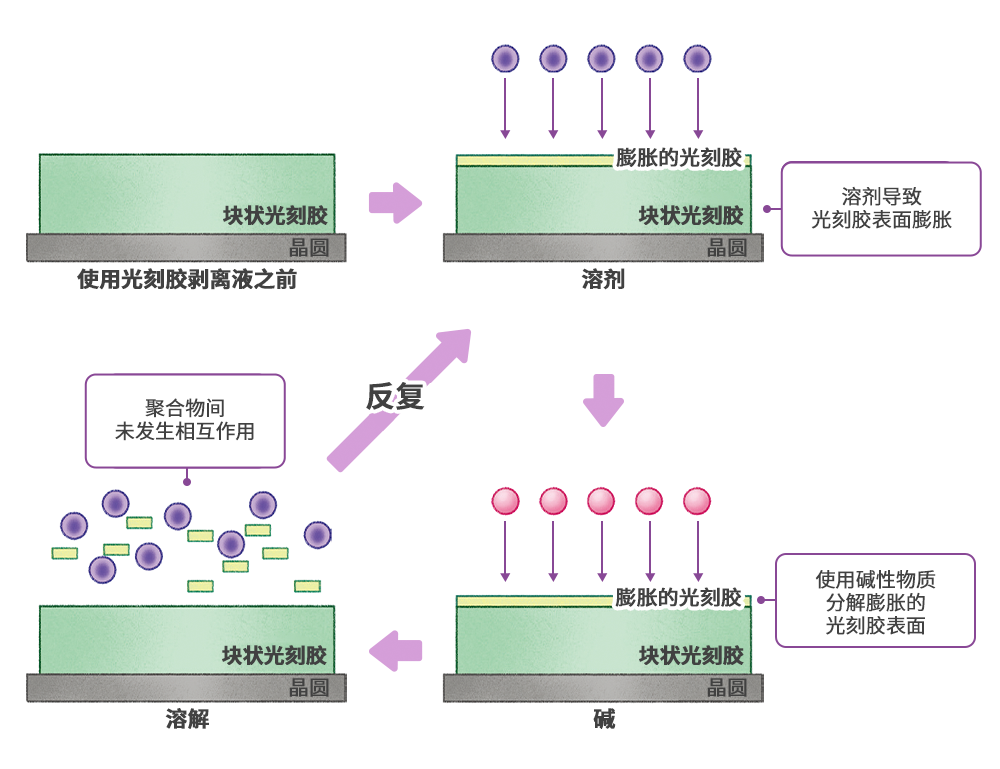

电镀工艺完成后,需使用光刻胶剥离液去除光刻胶,同时注意避免对晶圆造成化学性损伤或产生残留物。图3展示了光刻胶去胶工艺的过程。首先,当光刻胶剥离液与光刻胶表面接触时,两者会发生反应,使光刻胶膨胀;接下来,碱性剥离液开始分解并溶解膨胀的光刻胶。

▲ 图3:光刻胶剥离液的去胶工序(ⓒ HANOL出版社)

▲ 图3:光刻胶剥离液的去胶工序(ⓒ HANOL出版社)

刻蚀剂:使用酸、过氧化氢等材料精确溶解金属

晶圆级封装需要通过溅射(Sputtering)⁷工艺形成籽晶层(Seed Layer),即通过溅射或蒸馏的方式形成的一层用于电镀的薄金属。电镀和光刻胶去胶工序完成后,需使用酸性刻蚀剂来溶解籽晶层。 ⁷溅射(Sputtering):一种用高能离子轰击金属靶材,使喷射出来的金属离子沉积到晶圆表面的物理气相沉积工艺。

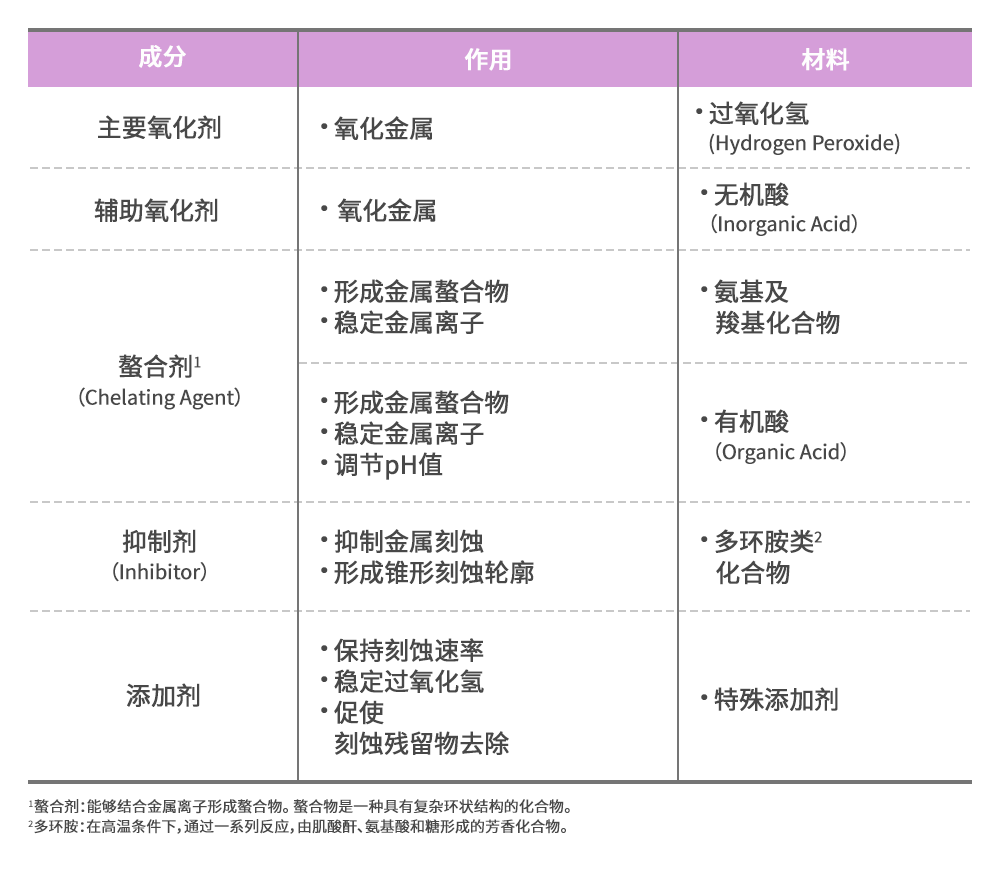

图4展示了刻蚀剂的主要成分和作用。根据不同的待溶解金属,可选用不同刻蚀剂,如铜刻蚀剂、钛刻蚀剂、银刻蚀剂等。此类刻蚀剂应具有刻蚀选择性——在有选择性地溶解特定金属时,不会溶解或仅少量溶解其它金属;刻蚀剂还应具备较高的刻蚀速率,以提高制程效率;同时还应具备制程的均匀性,使其能够均匀地溶解晶圆上不同位置的金属。

▲ 图4:刻蚀剂的主要成分和作用(ⓒ HANOL出版社)

▲ 图4:刻蚀剂的主要成分和作用(ⓒ HANOL出版社)

溅射靶材:将金属沉积于基板上

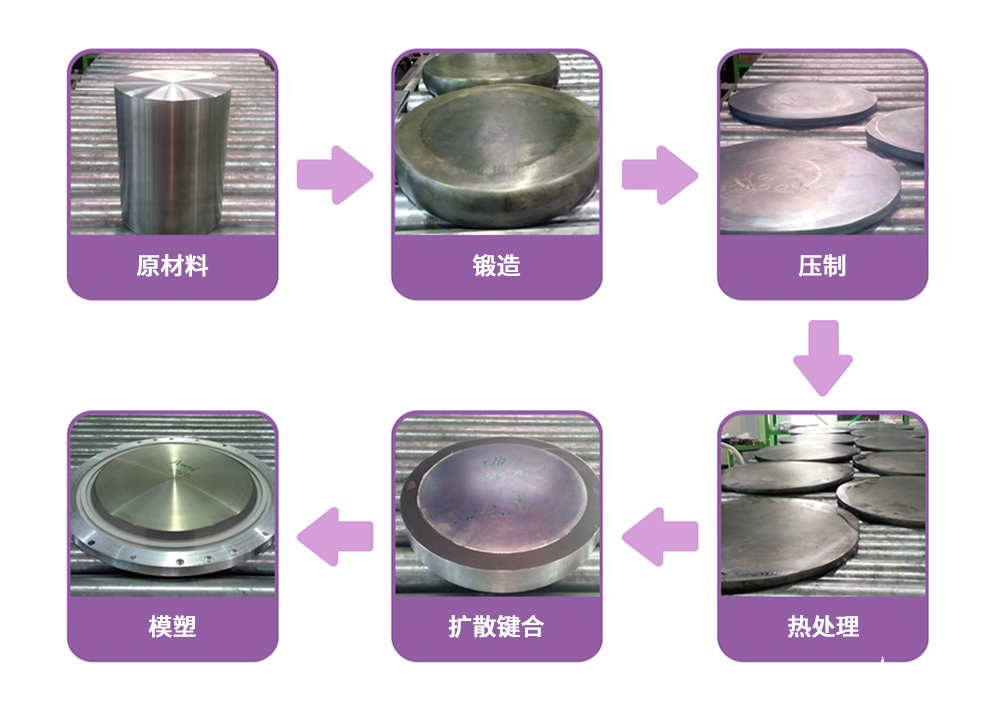

溅射靶材是一种在物理气相沉积(PVD)⁸过程中,采用溅射工艺在晶圆表面沉积金属薄膜时使用的材料。图5展示了靶材的制造工序。首先,使用与待溅射金属层成分相同的原材料制成柱体;然后经过锻造、压制、和热处理最终形成靶材。

⁸物理气相沉积(PVD):一种采用物理方法将材料分离并沉积在特定表面的薄膜沉积工艺。 ▲ 图5:溅射靶材的制作工序(ⓒ HANOL出版社)

▲ 图5:溅射靶材的制作工序(ⓒ HANOL出版社)

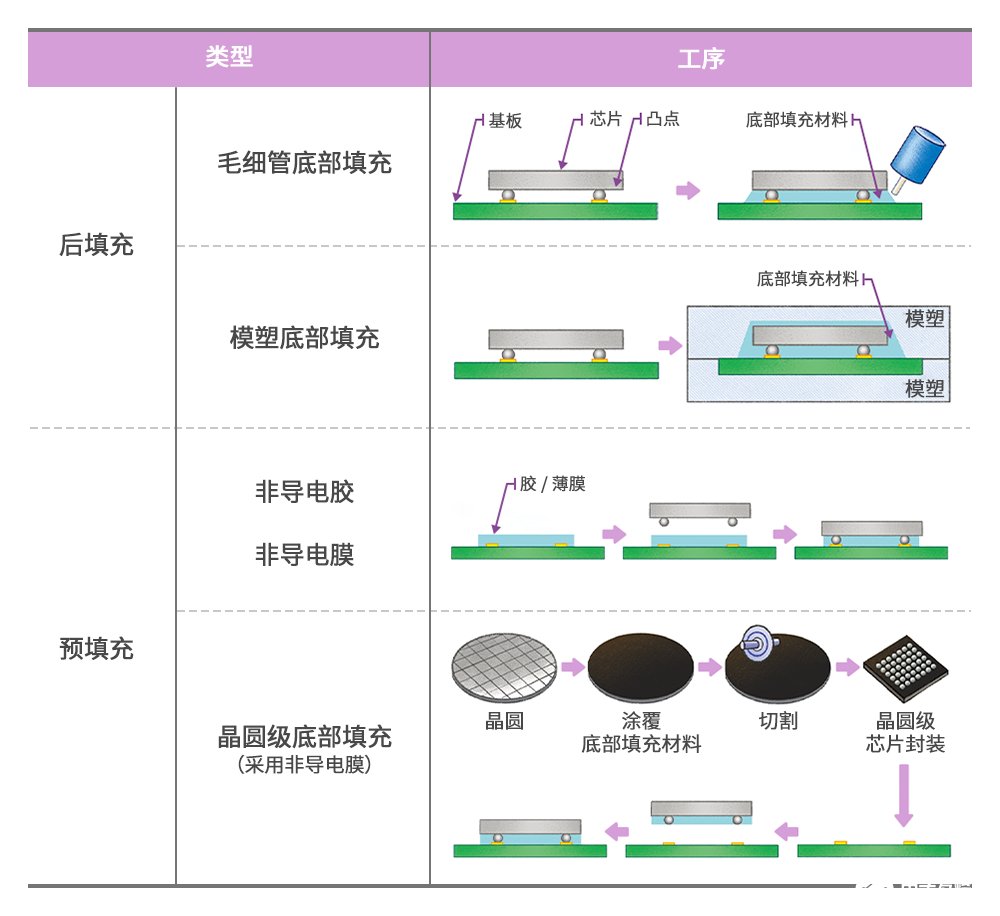

底部填充:使用环氧树脂模塑料(EMC)、胶和薄膜填充孔洞,实现接缝保护 与倒片键合(Flip Chip Bonding)相同,通过填充基板与芯片间的空隙、或以凸点链接的芯片与芯片之间的空隙,底部填充增强了接合处的可靠性。用于填充凸点之间空间的底部填充工艺分为后填充(Post-Filling)和预填充(Pre-applied Underfill)两种。后填充是指完成倒片键合之后填充凸点之间的空间,而预填充则是指在完成倒片键合之前进行填充。此外,后填充可进一步细分为毛细管⁹底部填充(Capillary Underfill, CUF)和模塑底部填充(Molded Underfill, MUF)。完成倒片键合之后,采用毛细管底部填充工艺,利用毛细管在芯片侧面注入底部填充材料来填充凸点间隙,此种工艺增加了芯片和基板之间的间隙内表面张力。而模塑底部填充则是在模塑过程中使用环氧树脂模塑料(EMC)作为底部填充材料,从而简化工序。 ⁹毛细管(Capillary):一种用于将液体封装材料输送到半导体封装体的极细管材。

在预填充过程中,芯片级封装和晶圆级封装采用的填充方法也有所不同。对于芯片级封装,会根据接合处的填充物,如非导电胶(NCP)或非导电膜(NCF),根据不同的填充物,其采用的工艺和材料也不尽不同;而对于晶圆级封装,非导电膜则被作为底部填充的主材。图6说明了不同类型的底部填充材料和相关工序。

▲ 图6:不同类型的底部填充工艺(ⓒ HANOL出版社)

▲ 图6:不同类型的底部填充工艺(ⓒ HANOL出版社)

在倒片封装和硅通孔(TSV)型芯片堆叠工艺中,底部填充材料是保证接合处可靠性的关键组成部分。因此,相关材料需满足腔体填充、界面粘附、热膨胀系数(CTE)¹⁰、热导性和热阻性等等方面的特定要求。 ¹⁰热膨胀系数(CTE):一种材料属性,用于表示材料在受热情况下的膨胀程度。

晶圆承载系统:使用载片、临时键合胶(TBA)、承载薄膜(Mounting tape)实现封装组装

晶圆承载系统工艺需充分支持薄晶圆载片和临时键合胶等相关工序。载片脱粘后,需使用承载薄膜将正面和背面已形成凸点的薄晶圆固定在环形框架上。 在晶圆承载系统所使用的材料中,临时键合胶尤为重要。在键合晶圆与载片形成硅通孔封装时,临时键合胶必须在晶圆背面加工过程中保持较强的黏附力, 以防止晶圆上的凸点等受损。此外,需确保不会出现排气(Outgassing)¹¹、空隙(Voids)¹²、分层(Delamination)¹³和溢出——键合过程中粘合剂从晶圆侧面渗出等现象。最后,载体还必须具备热稳定性和耐化学性,在保证载片易于去除的同时,确保不会留下任何残留物。

¹¹排气(Outgassing):气体从液体或固体物质中释放出来。如果这种气体凝结在半导体器件表面,并对器件性能产生影响,则会导致半导体器件存在缺陷。

¹²空隙(Voids):因气泡的存在,在材料内部形成的空隙,有可能在高温工艺或脱粘过程中会膨胀,增加使器件发生损坏或故障的风险。

¹³分层(Delamination):半导体封装中两个相连的表面互相分离的现象。 尽管首选材料为硅载片,但玻璃载片的使用频率也很高。尤其是在脱粘过程中使用激光等光源的工艺时,必需使用玻璃载片。

通过这些关于传统封装和晶圆级封装所需材料的文章介绍,我们不难发现,材料的类型和质量需不断与时俱进,以满足半导体行业的发展需求。

来源:未来半导体

欢迎扫码添加小编微信

扫码加入知识星球,领取公众号资料

审核编辑 黄宇

-

晶圆

+关注

关注

53文章

5449浏览量

132760 -

光刻胶

+关注

关注

10文章

357浏览量

31859 -

晶圆级封装

+关注

关注

5文章

47浏览量

11823

发布评论请先 登录

Keithley静电计6514在晶圆级测量中的关键应用

什么是晶圆级扇入封装技术

不同材料在晶圆级封装中的作用

不同材料在晶圆级封装中的作用

评论