文章来源:学习那些事

原文作者:前路漫漫

本文主要介绍扇出型(先上晶且面朝下)晶圆级封装。

本文主要介绍扇出型(先上晶芯片面朝下)晶圆级封装(FOWLP)。首个关于扇出型晶圆级封装(FOWLP)的美国专利由英飞凌(Infineon)于2001年10月31日提交,最早的技术论文则由英飞凌与其行业合作伙伴日本长濑(Nagase)、日东电工(Nitto Denko)和日本山田(Yamada)等公司,在ECTC2006和EPTC2006会议上联合发表。当时该技术被命名为嵌入式晶圆级焊球(embedded wafer-level ball,eWLB)阵列,这种方法摒弃了引线键合、晶圆凸点成型工艺,同时不再使用引线框和封装基板,有望实现低成本、高性能、小型化的封装效果。该方法需借助临时支撑片完成合格芯片(known-good die,KGD)的晶圆重构、环氧模塑料(epoxy molding compound,EMC)模塑以及再布线层(redistribution layer, RDL)的制备。ECTC2007会议上,飞思卡尔(Freescale)发表了一项类似技术,并将其命名为重构芯片封装(redistributed chip package,RCP)。ECTC2008会议上,新加坡微电子所(IME)研发出支持多芯片及多芯片3D堆叠的FOWLP技术;ECTC2009会议上,IME发表4篇FOWLP相关论文,分别聚焦于模压成型过程中芯片移位的预测新方法、超薄芯片的横向放置与垂直堆叠、3D FOWLP的可靠性,以及高质量、低损耗毫米波无源器件FOWLP的演示。

扇出型(先上晶面朝下)晶圆级封装可用于异质集成,相关技术中采用液态环氧模塑料(EMC)进行模压成型,所制备的RDL金属线宽/线距为10/15μm。本节采用全新的干膜EMC层压方法,替代传统液态EMC模塑方式,所制备的RDL金属线宽/线距可缩小至5~10μm。同时,为节省昂贵的EMC材料并实现小型化(薄型)封装,提出了一种特殊的组装工艺。

测试芯片

图1为所采用的两颗测试芯片。图1a为大测试芯片及其焊盘排布,该芯片尺寸为5mm×5mm×150μm,共包含160个焊盘,内侧焊盘节距为100μm。铝焊盘上SiO₂钝化层开窗尺寸为50μm×50μm,铝焊盘本身尺寸为70μm×70μm。小芯片尺寸为3mm×3mm×150μm,图1b为该芯片的实物图,其包含80个焊盘,内侧焊盘节距同样为100μm,焊盘截面及尺寸与大测试芯片完全一致。

图1

测试封装体

图2a为测试封装体的结构示意图,封装体尺寸为10mm×10mm,包含1颗大芯片(5mm×5mm)和3颗小芯片(3mm×3mm),大芯片与小芯片之间的间距为100μm。该封装体设有2层再布线层(RDL),图2b为芯片到RDL1的再布线层结构,图2c为RDL1到RDL2的再布线层结构,图2d为RDL2到PCB的连接结构,图2e为封装体的整体轮廓。封装体全部在12in临时玻璃重构晶圆上制备完成,晶圆上封装体的节距为10.2mm。实际应用中,大芯片可作为应用处理器芯片,小芯片可作为存储芯片,这种制备方式效率极高,可一次性实现629个封装体(10mm×10mm,每个含4颗芯片)的异质集成。

图2

图3为测试封装体的截面示意图,从中可清晰看到2层RDL结构,其中RDL1的金属层厚度为3μm,RDL2的金属层厚度为7.5μm;RDL1的金属线宽和线距均为5μm,RDL2的金属线宽和线距均为10μm。DL1和DL2的介质层厚度为5μm,DL3的介质层厚度为10μm。连接测试芯片铜焊盘与RDL1、穿过介质层(DL1)的孔(VC1)直径为20~30μm,RDL1焊盘直径为55μm,通过直径30~40μm的过孔(V12)与RDL2连接,RDL2焊盘直径为65μm。最终在RDL2上形成直径220μm的焊球铜焊盘,钝化层(DL3)开窗直径为180μm,焊球直径为200μm,节距为0.4mm。

图3

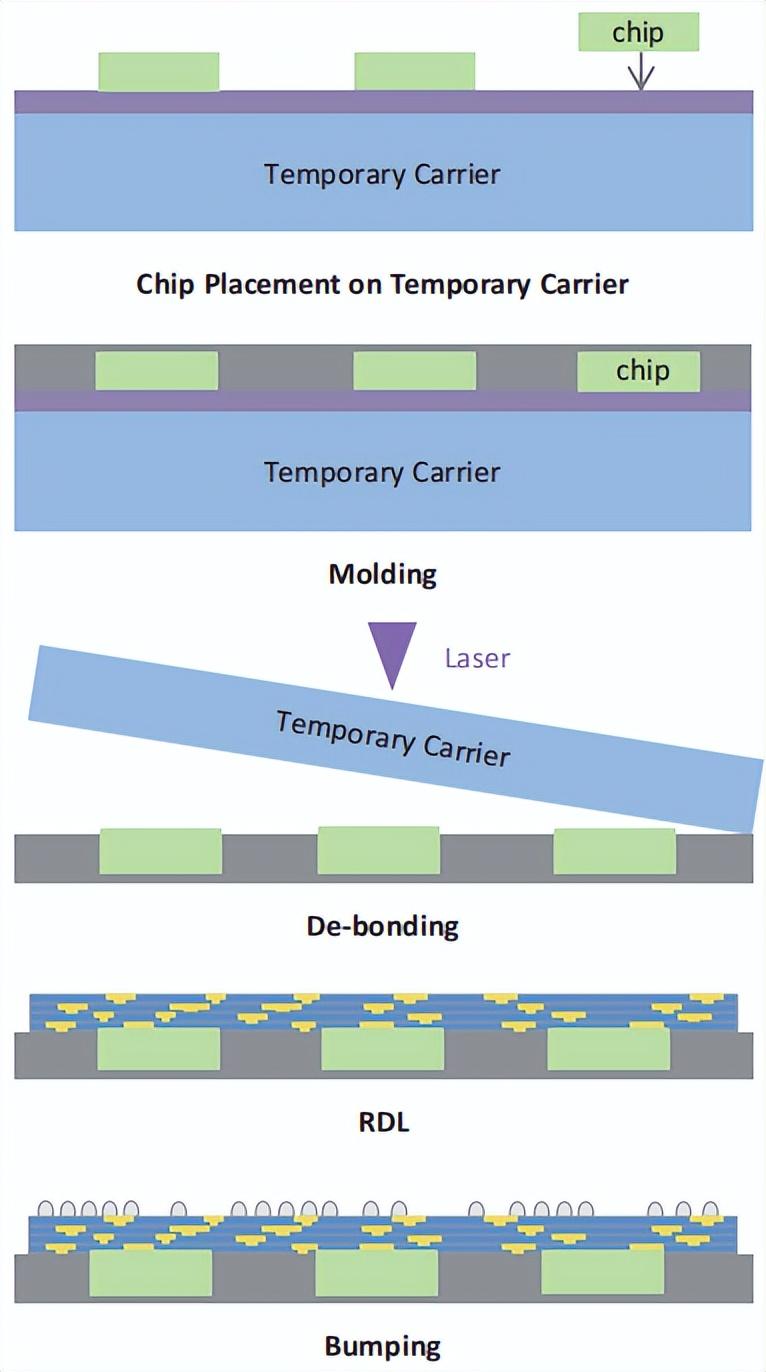

传统的先上晶(面朝下)晶圆级工艺 图4为传统先上晶面朝下FOWLP工艺流程图。首先,对器件晶圆进行合格芯片(KGD)测试,测试合格后切割得到单颗芯片;随后拾取KGD,将其面朝下放置在圆形(晶圆状)或矩形(面板状)的临时支撑片上(支撑片可选用金属、硅或玻璃材质),如图4b所示。临时载具上预先粘贴双面热剥离胶带,如图4a所示。KGD放置完成后,对重构支撑片进行EMC模塑处理(见图4c),模塑过程采用模压+后固化处理(post mold cure,PMC)。模塑完成后,去除临时支撑片并剥离胶带(见图4d),接着在重构晶圆上制备RDL(见图4e),最后进行植球操作,并将包含KGD、RDL和焊球的整个重构晶圆划片切割,得到单独的封装体(见图4f)。

图4

异质集成封装的新工艺

本文未采用传统工艺中的模压模塑及常规RDL制备方法,而是采用图5所示的全新工艺流程,以实现更优的封装效果和成本控制。

图5

干膜EMC层压

本文采用新型干膜EMC材料,其材料特性见表1,通过层压方式完成模塑操作,替代了传统液态EMC模塑方法。如图5a、5b所示,拾取KGD并放置在支撑片上后,在其表面层压一层厚度为200μm的干膜EMC(见图5c和图6),层压温度设定为100℃,层压时间为30min。

表1

图6

临时键合另一块玻璃支撑片

传统FOWLP工艺中,EMC模塑完成后需解键合支撑片并剥离胶带(见图4d),此时重构晶圆的厚度通常不小于450μm,之后再进行RDL制备和植球操作(见图4e)。本研究中,为节省昂贵的EMC材料并实现小型化(薄型)封装,无支撑片状态下重构晶圆的总厚度仅为300μm,这种超薄晶圆极易破碎,会给RDL制备和植球操作带来极大困难。

针对这一问题,解决方案为将薄重构晶圆粘接至另一块预先涂覆光热转换层的1mm厚玻璃晶圆(热膨胀系数为6.4×10⁻⁶/℃)上,如图5d所示。随后对干膜EMC进行130℃、60min的预固化处理,之后去除第一块临时支撑片并剥离胶带(见图5e),最后对干膜EMC进行180℃、90min的固化处理,确保其性能稳定。

再布线层

如图5e所示,固化完成后开始制备RDL。图7为RDL制备的关键工艺步骤:首先在重构晶圆上旋涂一层光敏聚酰亚胺(polyimide,PI);随后采用步进式光刻机(每4个封装体作为一个单元),在PI层上完成对准、曝光、显影操作,制备出过孔;之后将PI材料在200℃下固化1h,获得厚度为4~5μm的PI层;接着在整块晶圆上采用物理气相沉积法,在175~200℃条件下溅射Ti层和Cu层;再次涂覆光刻胶,通过步进式光刻技术获得RDL布线图形,采用电化学方法在开窗后的Ti/Cu层上电镀Cu线路,剥离光刻胶并刻蚀掉多余的Ti/Cu层,即可得到RDL1;重复上述工艺步骤,可制备得到RDL2。

图7

图8

图9

图8所示为RDL1的金属线宽/线距实拍图,可见其线宽/线距与设计值(5μm)高度吻合。图9为通过扫描电镜(scanning electron microscope,SEM)观察到的RDL1截面图,清晰展示了芯片、光敏聚酰亚胺与RDL1的结构,其中RDL1的金属线宽/线距为5μm,符合设计要求。

焊球植球

如图5e所示的植球工艺中,需使用两套不同的模板,分别用于助焊剂模板印刷和焊球模板植球。本研究采用SAC305(Sn3wt%Ag0.5%Cu焊球,焊球直径为200μm,节距为0.4mm,焊料回流的峰值温度设定为245℃,确保焊球与焊盘连接牢固、性能稳定。

最终解键合

图5f所示的玻璃支撑片解键合操作,通过从玻璃支撑片一侧采用激光(355nm DPSS Nd:YAG UV)扫描完成。激光束斑为240μm,扫描速度为500mm/s,扫描步进距离为100μm。光热转换材料在激光照射下会转化为粉末状,使得玻璃支撑片可轻松移除,解键合完成后需进行化学清洗,去除残留杂质。

图10为无任何支撑片的重构晶圆及单个封装体的特写照片,可见一个封装体中包含4颗芯片,芯片排布精准、定位准确。将重构晶圆按照图5g所示进行划片,得到单个芯片单元,其X射线图像如图11所示,从中可清晰观察到RDL1和RDL2的结构分布。

图10

图11

图12为典型异质集成封装体的截面图,可见封装体包含2层RDL,其中RDL2的金属层厚度(7.5μm)大于RDL1(3μm)。RDL2设计较厚的原因是,在无凸点下金属化层(UBM)的情况下,可获得较厚的铜焊盘,从而有效防止焊球回流及器件工作过程中铜层被耗尽,保障封装体的长期可靠性。

图12

采用C模式扫描超声波显微镜(C-mode scanning acoustic microscopy,C-SAM)对层压干膜EMC中的模塑空洞进行检测。为平衡检测分辨率与信号穿透深度,选用75MHz超声换能器开展空洞检测,经过一系列扫描参数优化与检测,未在晶圆中检测到任何空洞(包括EMC内部及间隔空间),检测结果如图13所示,表明干膜EMC层压工艺的稳定性和可靠性良好。

图13

-

芯片

+关注

关注

463文章

54379浏览量

468992 -

晶圆

+关注

关注

53文章

5445浏览量

132713 -

晶圆级封装

+关注

关注

5文章

47浏览量

11819

原文标题:扇出型(先上晶且面朝下)晶圆级封装

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

扇出型晶圆级封装技术介绍

扇出型晶圆级封装技术介绍

评论