11月6日消息,据彭博社报道,佳能公司正计划将其新的基于“纳米压印”技术的芯片制造设备的价格定为ASML的EUV***的1/10。由于该设备可以用于制造5nm尖端制程芯片,且不是基于光学技术,或将成为中国绕过美国限制来制造尖端制程芯片的可行方案。但是,佳能首席执行官三井藤夫在采访中表示,该设备无法出口到中国。

尖端制程严重依赖EUV***

总部位于荷兰的ASML是目前全球最大的***厂商,同时也是全球唯一的极紫外光刻设备供应商。EUV***是目前世界上最先进的芯片制造设备,每台成本高达数亿美元。

虽然目前在***市场,还有尼康和佳能这两大供应商,但是这两家厂商的产品主要都是被用于成熟制程芯片的制造,全球市场份额仅有10%左右,ASML一家占据了90%的市场份额,并垄断了尖端的EUV***的供应。

目前7nm以下的先进制程芯片的大规模生产主要都是依赖于ASML的EUV***,但只有少数现金充裕的公司才有能力投资购买这些EUV***。

即便如此,EUV***仍因为其在尖端芯片制造供应链中的关键地位而一直受到出口管制审查。多年前,美国就有向其盟友——荷兰施压,要求其限制EUV设备出口到中国。今年6月30日,荷兰政府正式出台了新的半导体出口管制措施,ASML被禁止向中国客户出口EUV系统以及先进的浸没式DUV系统。

这也意味着中国想要突破到5nm,甚至更尖端的制程工艺将会面临极大的困难。

绕过EUV,佳能纳米压印技术可量产5nm

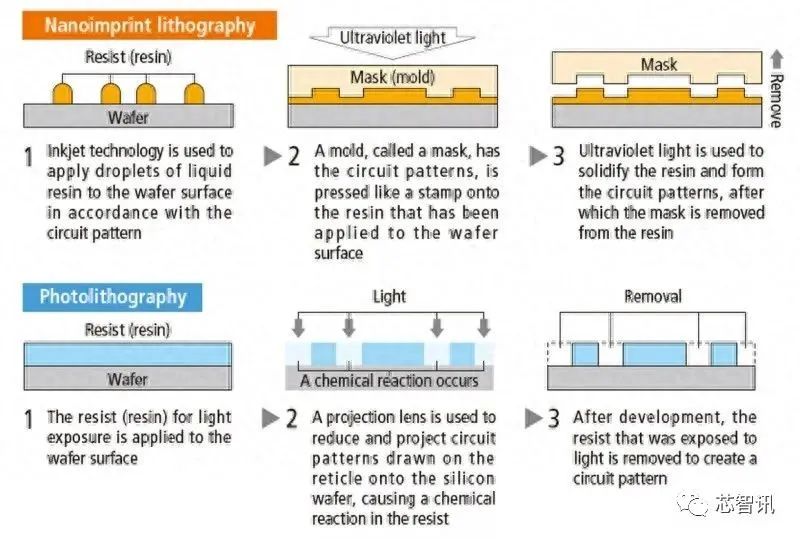

今年10月中旬,佳能公司宣布开始销售基于“纳米压印”(Nanoprinted lithography,NIL)技术的芯片生产设备 FPA-1200NZ2C。佳能表示,该设备采用不同于复杂的传统光刻技术的方案,可以制造5nm芯片。

此前佳能一直专注于制造不太先进***产品。直到2014年,佳能收购了Molecular Imprints股份有限公司,开始押注纳米压印技术

近十年来,佳能一直在与日本光罩等半导体零组件制造商大日本印刷株式会社(DNP)和存储器芯片制造商铠侠(Kioxia)合作研发纳米压印工艺。该技术可以不使用EUV***,就能使制程技术推进到5nm。

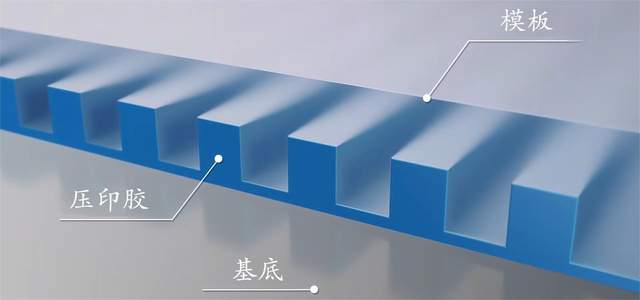

佳能表示,这套生产设备的工作原理和行业领导者 ASML 的***不同,其并不利用光学图像投影的原理将集成电路的微观结构转移到硅晶圆上,而是更类似于印刷技术,直接通过压印形成图案。

相较于目前已商用化的EUV光刻技术,尽管纳米压印技术的芯片制造速度要比传统光刻方式慢,但铠侠在2021年就曾表示,纳米压印技术可大幅减少耗能,并降低设备成本。原因在于纳米压印技术的制程较为简单,耗电量可压低至EUV 技术的10%,并让设备投资降低至仅有EUV设备的40%。

佳能首席执行官三井藤夫在最新的采访中表示,这项新的纳米压印技术将为小型半导体制造商生产先进芯片开辟一条道路。“价格将比ASML的EUV***低一位数(即仅有10%)”这位88岁的老人上一次退出日常运营是在2016年,现在是他第三次担任佳能公司总裁。他补充说,佳能尚未做出最终定价决定。

另外,纳米压印设备还可以使得芯片制造商降低对于ASML的EUV***的依赖,使得台积电、三星等晶圆代工厂可以有第二个路线选择,可以更灵活的为客户生产小批量芯片。甚至,芯片设计厂商可以不依赖于晶圆代工厂来自己生产小批量的芯片。

因为NAND闪存的图形更为简单,因为其采取是多层几乎相同的层的堆叠,所以更容易适应基于纳米压印的技术制程。铠侠数年前就表示,已解决纳米压印的基本技术问题,正在进行量产技术的推进工作,希望能较其他竞争对手率先引入到NAND 生产当中。但随后的消息显示,铠侠在对纳米压印技术进行测试之后,遭到了潜在客户提出的投诉,认为产品缺陷率较高,最后并未实际应用。

另外,相对于更为复杂的,逻辑芯片来说,应用纳米压印技术的来制造还是面临着很多的挑战。不过,佳能在推动纳米技术量产NAND的同时,也致力于将纳米压印量产技术广泛的应用于制造DRAM 及PC 用的CPU 等逻辑芯片的设备上,以在未来供应多的半导体制造商,也希望能应用于手机应用处理器等最先进制程上。

据了解,佳能目前正在日本东京北部的宇都宫建造20年来第一家新的光刻设备工厂,将于2025年上线。

佳能最新发布的这套纳米压印设备可以应用于最小14平方毫米的硅晶圆,从而可以生产相当于5nm工艺的芯片。佳能表示会继续改进和发展这套系统,未来有望用于生产 2nm 芯片。

对于纳米压印技术市场前景,三井藤夫说:“我不认为纳米压印技术会超过EUV,但我相信这将创造新的机会和需求。我们已经接到了很多客户的咨询。”

纳米压印设备无法出口到中国

受美国及荷兰出台对于先进半导体设备的出口管制影响,国内业界对于佳能最新推出基于纳米压印技术的芯片制造设备可以绕过EUV生产5nm充满了兴趣,认为这可能会是一条能够绕过美国限制制造更先进制程芯片的路径。

虽然在今年7月日本实施了新的半导体出口管制措施,限制了可以被用于先进制程的浸没式***的出口,其中似乎并未新增对于限制基于纳米压印技术的***的出口。

但是事实上,芯智讯查阅日本的出口管制清单,当中就有限制“可实现45nm以下线宽的压印光刻装置”。

佳能CEO三井藤夫也在最新的采访中表示,佳能可能无法将这些(基于纳米压印技术的)芯片制造设备出口到中国。“我的理解是,任何超过14nm技术的出口都是被禁止的,所以我认为我们无法销售。”

日本经济省的一名官员表示,他无法评论出口限制将如何影响特定的公司或产品。

-

存储器

+关注

关注

39文章

7760浏览量

172286 -

光刻机

+关注

关注

31文章

1201浏览量

49042 -

EUV

+关注

关注

8文章

615浏览量

88985

原文标题:可绕过EUV量产5nm!佳能CEO:纳米压印设备无法卖到中国!

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

俄罗斯亮剑:公布EUV光刻机路线图,挑战ASML霸主地位?

烧结银的中国创新之路:从280℃到130℃

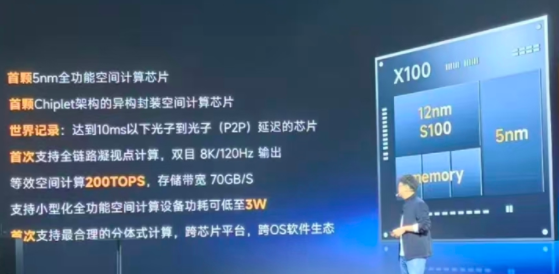

芯擎科技“龍鹰二号”:5nm舱驾融合芯片开启智能汽车AI新纪元

芯擎首发5nm“龍鹰二号”! 200TOPS算力+7B大模型,2027年Q1量产适配

「纳米光栅无损检测」告别破坏性表征,光谱椭偏仪实现99.97%精度无损测量

纳米压印的光栅图形形貌3D测量-3D白光干涉仪应用

1600TOPS!美国新势力车企自研5nm芯片,转用激光雷达硬刚特斯拉

2分钟压印周期,良率将冲95%!魔飞光电如何破解光波导量产困局

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

佳能9月启用新光刻机工厂,主要面向成熟制程及封装应用

今日看点丨蔚来自研全球首颗车规5nm芯片!;沃尔沃中国区启动裁员计划

压电纳米定位系统如何重塑纳米压印精度边界

可绕过EUV量产5nm!佳能CEO:纳米压印设备无法卖到中国!

可绕过EUV量产5nm!佳能CEO:纳米压印设备无法卖到中国!

评论