芯片异构集成的概念已经在推动封装技术的创新。

混合键合支持各种可能的芯片架构,主要针对高端应用,包括高性能计算 (HPC)、人工智能 (AI)、服务器和数据中心。随着技术的成熟,消费类应用、包括高带宽存储器 (HBM) 在内的存储器件以及移动和汽车应用预计将进一步增长,这些应用可受益于高性能芯片间连接。

异构集成的背景故事

玩积木的乐趣之一就是可以用看似无限的方式将它们组合在一起。想象一下,将这一概念应用于半导体行业,您可以采用不同类型的芯片并将它们像块一样组合起来以构建独特的东西。首先为半导体产品确定性能、尺寸、功耗和成本目标,然后通过将不同类型的芯片组合到单个封装中来满足要求。这种芯片异构集成的概念已经在推动封装技术的创新。

最近,封装中异构集成的采用不断加速,以满足对更复杂功能和更低功耗日益增长的需求。异构集成允许 IC 制造商在单个封装中堆叠和集成更多硅器件。这可以包括来自不同晶圆、不同半导体技术和不同供应商的芯片的组合。异构集成还使小芯片集成能够克服大型芯片的产量挑战以及掩模版尺寸限制。

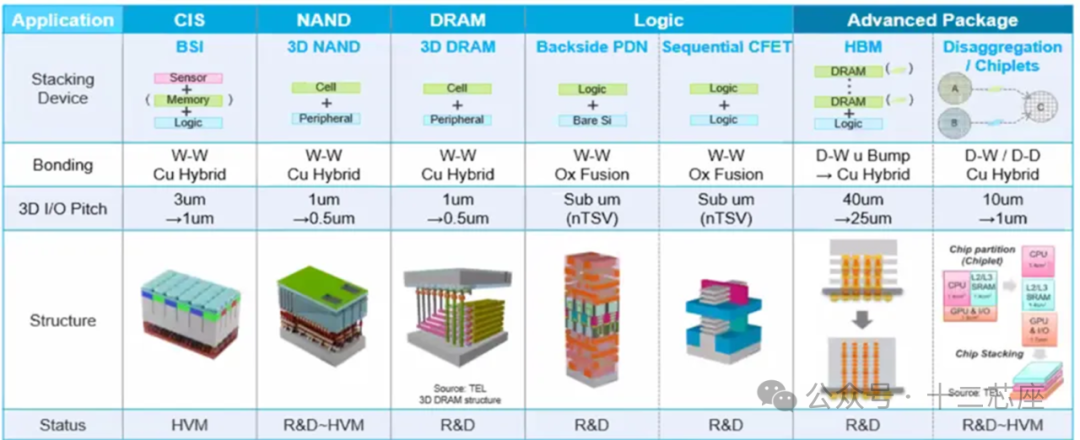

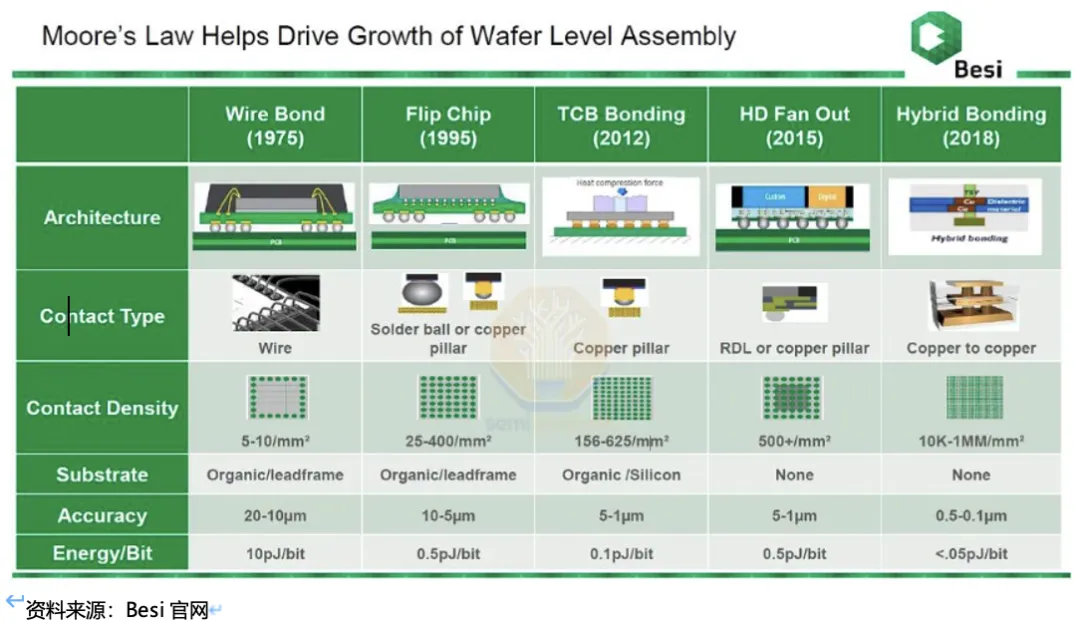

随着 2.5D、3D 和扇出封装技术的发展,铜微凸块已在单个集成产品中提供了所需的垂直金属器件到器件互连。铜微凸块的间距通常为 40μm(凸块尺寸为 25μm,间距为 15μm),现已缩小至 20μm 和 10μm 间距,以提高封装密度和功能。然而,低于 10μm 的键合间距,微凸块开始遇到产量和可靠性的挑战。因此,虽然传统的铜微凸块将继续使用,但新技术也正在开发中,以继续提高互连密度。混合键合技术正在成为互连间距为 10μm 及以下的高端异构集成应用的可行途径。

什么是混合键合?

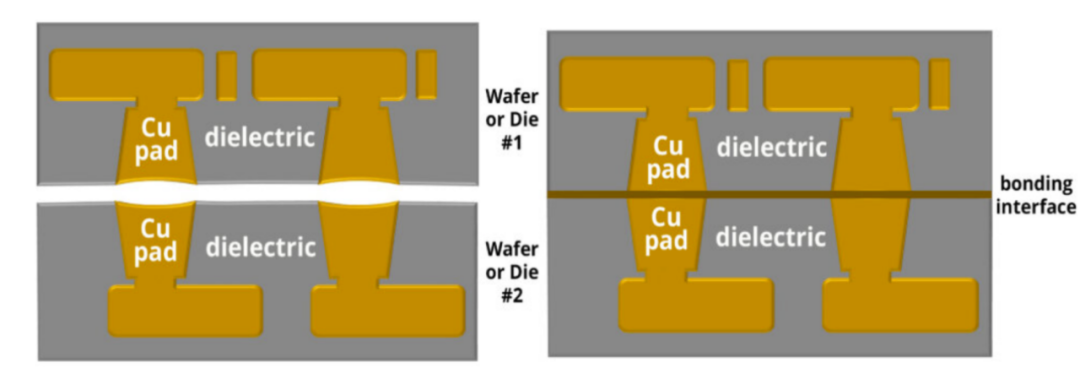

混合键合是在异质或同质芯片之间创建永久键合的过程。“混合”是指在两个表面之间形成电介质-电介质和金属-金属键。使用紧密嵌入电介质中的微小铜焊盘可提供比铜微凸块多 1,000 倍的 I/O 连接,并将信号延迟驱动至接近零水平。其他优点包括扩展的带宽、更高的内存密度以及更高的功率和速度效率。

混合键合技术

关键工艺步骤包括预键合层的准备和创建、键合工艺本身、键合后退火以及每个步骤的相关检查和计量,以确保成功键合。

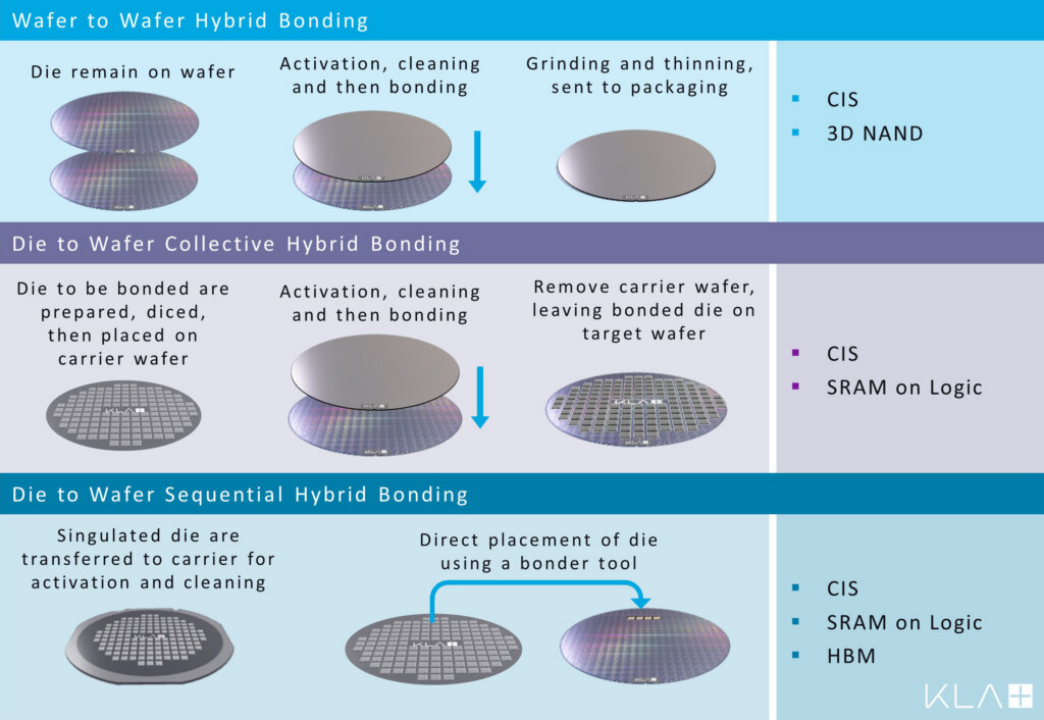

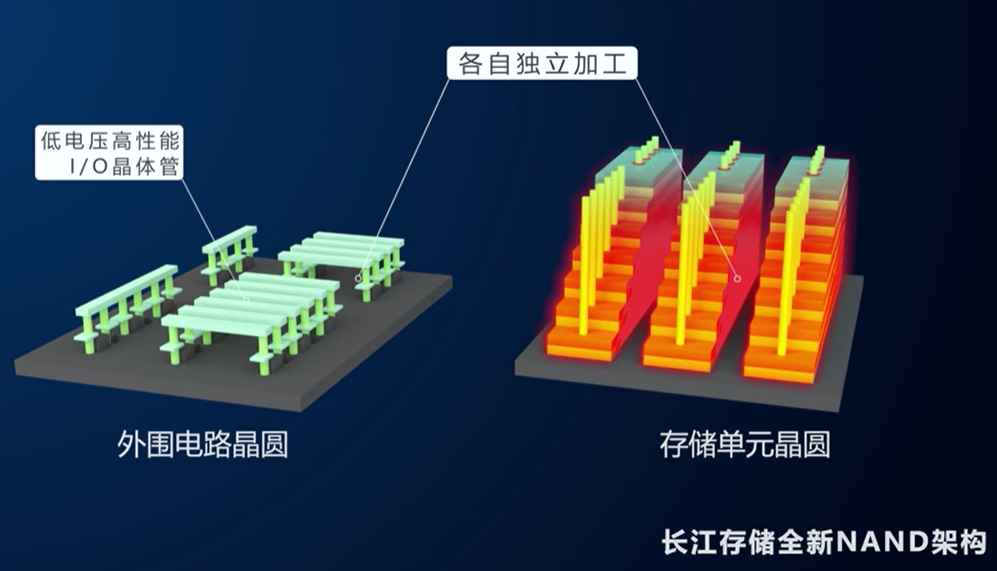

有两种方法可以实现混合键合:晶圆到晶圆 (W2W) 和芯片到晶圆 (D2W) 。

图 2:W2W 和 D2W 混合键合技术和应用。

D2W 是异构集成中混合键合的主要选择,因为它支持不同的芯片尺寸、不同的晶圆类型和已知的良好芯片,而所有这些对于 W2W 方案来说通常是不可能的。对于每种芯片,首先在半导体工厂中制造晶圆,然后利用混合键合工艺垂直堆叠芯片。

混合键合将封装转向“前端”

由于涉及先进的工艺要求和复杂性,混合键合发生在必须满足污染控制、工厂自动化和工艺专业知识要求的环境中,而不是像许多其他封装集成方法那样在典型的封装厂中进行。为了准备用于键合的晶圆,需要利用额外的前端半导体制造工艺在晶圆上创建最终层以连接芯片。这包括电介质沉积、图案化、蚀刻、铜沉积和铜 CMP。半导体工厂拥有混合键合工艺所需的环境清洁度、工艺工具、工艺控制系统和工程专业知识。

需要已知良好的模具

使用 D2W 混合键合将多个芯片异构集成到一个封装中,从而产生高性能、高价值的器件。当您考虑到包含一个坏芯片可能会导致整个封装报废时,风险就很高。为了保持高产量,需要仅使用已知良好的模具。需要优化工艺并实施敏感的工艺控制步骤,以实现芯片完整性,以增加可用芯片的数量,并提供在进入 D2W 等工艺之前将好芯片从坏芯片中分类所需的准确信息。

无空洞键合,实现高产量

无空隙键合取决于电介质区域和铜焊盘的成功键合。在键合过程中,初始键合发生在室温、大气条件下的电介质与电介质界面处。随后,通过退火和金属扩散形成铜金属到金属连接。

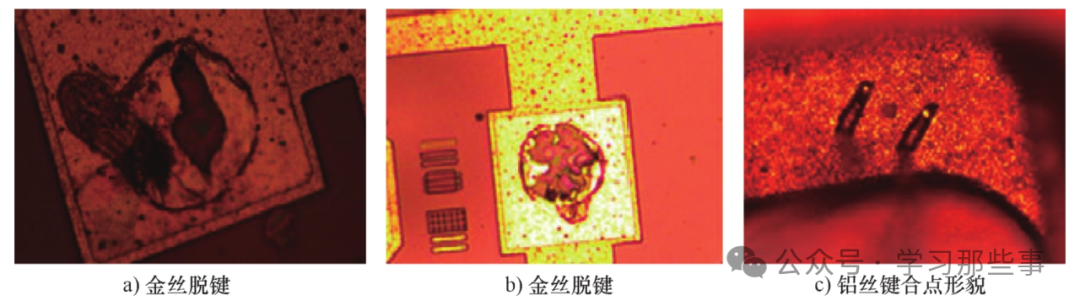

混合键合表面必须超级干净,因为即使是最微小的颗粒或最薄的残留物也可能会扰乱工艺流程并导致设备故障。需要进行高灵敏度检查来发现所有缺陷,以验证芯片表面是否保持清洁,以实现成功的无空隙接合。

SiCN 已被证明比 SiN 或 SiO2等替代电介质具有更高的结合强度。最近的开发工作已证明 SiCN 的等离子体增强化学沉积 (PECVD) 温度足够低,足以满足任何临时条件的限制。粘合层(<200 °C )。薄膜的特性还包括所需的稳定性,以避免在去除临时粘合层后随着随后的铜退火温度升高(> 350°C)而解吸氢气或碳氢化合物(这可能导致形成空隙)。

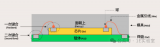

在混合键合之前,铜焊盘必须具有最佳的碟形轮廓,以允许铜在金属键合过程中膨胀。

图 3:描绘所需铜焊盘凹陷轮廓的预键合晶圆(或芯片)图像(左)和显示成功的芯片到芯片连接的键合后图像(右)。

为了实现无空隙接合,需要浅且均匀的铜凹槽。在这里,高分辨率计量可用于监控和驱动过程控制和改进。

等离子切割可实现更清洁、更坚固的芯片

在每个工艺步骤中,必须仔细控制许多潜在的空隙、缺陷和不均匀性来源。即使是小至 100 纳米的颗粒也可能导致数百个连接失败和有缺陷的堆叠封装。例如,在 D2W 混合键合中,单个芯片在被转移并键合到第二个完整晶圆之前被切割,传统的切割方法(例如机械锯或激光开槽/切割)可能会引入颗粒或表面缺陷,特别是在模具边缘,这会干扰后续的混合键合过程。等离子切割是一种替代方法,已在特定应用中的大批量生产中得到验证,其中每个晶圆更多芯片或增强芯片强度等优势超过了任何增加的加工成本。在混合键合的情况下,等离子切割工艺会产生极其干净的芯片表面和边缘,没有与刀片切割相关的颗粒污染或边缘碎片,也没有激光碎片/重铸/激光凹槽裂纹。在混合键合之前进行等离子切割芯片将导致更一致的键合、更低的缺陷率和更高的器件良率。

混合键合工艺控制

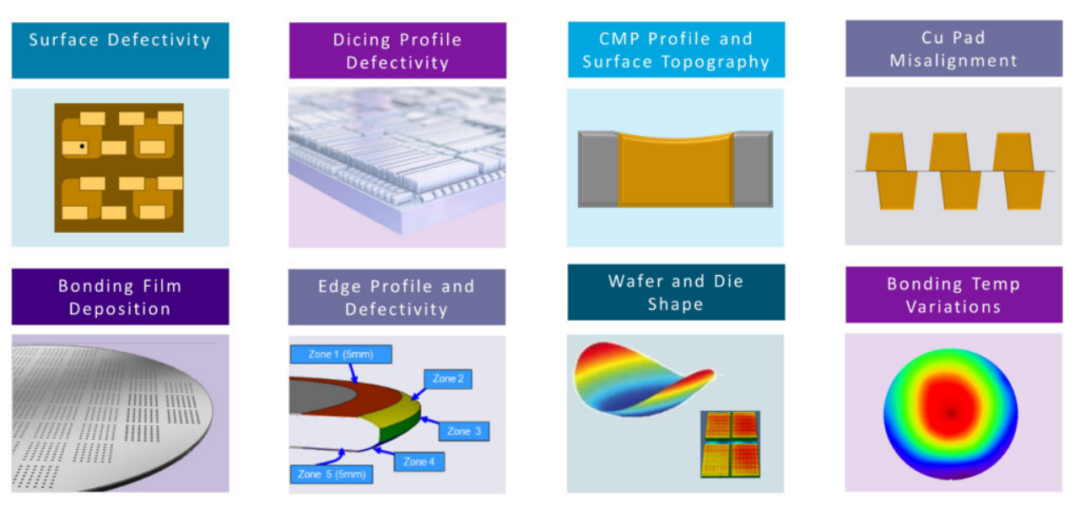

为了使混合键合成功过渡到高产量的大批量制造 (HVM),工艺控制至关重要。晶圆上的预键合不均匀性、空隙和其他缺陷会在键合过程中直接干扰铜互连并降低产品产量。影响键合的其他不均匀性来源包括 CMP 轮廓和表面形貌、铜焊盘未对准、晶圆形状以及键合温度的变化。这些问题中的每一个都必须从源头仔细衡量和控制。

图 4:可能对产品质量产生不利影响的因素示例

混合键合的一些关键工艺控制要求包括:

薄膜厚度和均匀性:必须仔细控制芯片内、整个晶圆以及晶圆与晶圆之间形成最终预粘合层的电介质膜厚度。

覆盖对准:为了成功地以非常小的间距(目前约为 1-10μm)粘合表面,需要严格控制接合焊盘对准,以确保要接合的铜焊盘完美对齐,从而推动对覆盖计量精度的需求不断增加和芯片焊接控制。

缺陷率:混合键合中的直接电介质对电介质键合和铜对铜键合需要更清洁的表面,不含颗粒和残留物,以最大限度地减少界面处的空洞。与传统的焊料凸块接口相比,这推动了等离子切割等优化工艺的采用,以及显著更高的检测灵敏度和严格的缺陷减少工作。

轮廓和粗糙度:成功的键合需要将表面轮廓和粗糙度控制在纳米级,需要更精确的计量技术来帮助开发和控制 HVM 环境中预键合表面的制备。在键合之前,铜焊盘必须具有特定的碟形轮廓。

形状和弓形:W2W 和 D2W 混合键合对晶圆形状和弓形都很敏感,因此对晶圆级和芯片级形状计量的需求日益增加,以进行表征和控制。

在实际键合工艺之后还需要额外的工艺和工艺控制步骤,例如 D2W 键合中的芯片间间隙填充,其中电介质沉积在单独键合芯片之间和顶部上方。通过适当的应力控制措施,PECVD 可以使用 TEOS 前驱体生产极厚、无裂纹的 SiO,并且能够承受后续步骤,例如 CMP 和光刻。

审核编辑:刘清

-

存储器

+关注

关注

39文章

7714浏览量

170853 -

CMP

+关注

关注

6文章

159浏览量

27573 -

HPC

+关注

关注

0文章

342浏览量

24825 -

HBM

+关注

关注

2文章

426浏览量

15698

原文标题:混合键合将异构集成提升到新的水平

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

通信不发愁,PROFINET转DEVICENET网关诊断解决方案将状态监测提升到新水平

3D集成赛道加速!混合键合技术开启晶体管万亿时代

LG电子重兵布局混合键合设备研发,锁定2028年大规模量产目标

从微米到纳米,铜-铜混合键合重塑3D封装技术格局

混合键合市场空间巨大,这些设备有机会迎来爆发

闪存冲击400层+,混合键合技术传来消息

将2.5D/3DIC物理验证提升到更高水平

混合键合将异构集成提升到新的水平

混合键合将异构集成提升到新的水平

评论