为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟器件作为合成器、抖动滤除功能时的噪声特性。

2013-06-21 15:40:41 19925

19925

AD9518-3A / PCBZ,用于AD9518-3A的评估板,2000 MHz超低噪声PLL时钟合成器,具有集成VCO,时钟分频器。 AD9518具有自动保持功能和灵活的参考输入电路,可实现非常

2019-03-05 06:04:50

AD9517-1A / PCBZ,用于AD9517-1A的评估板,2500 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9517具有自动保持功能和灵活的参考输入电路,可实现非常

2019-03-05 09:15:52

”三种方式。没有规定数据的加密处理方式。NFC标准与索尼开发的“FeliCa”以及荷兰恩智浦半导体(NXP Semiconductors)的“Mifare”所采用的非接触式IC卡技术,在物理层上具有兼容性

2011-07-13 15:11:55

噪声环境下的语音识别技术研究

2012-08-20 12:57:55

噪声抑制和出色的电源抑制比 (PSRR) 来帮助改进无错数据传输。图2显示的是使用LMK03328时对PSRR和TX眼图性能的改进,其原因就在于LMK03328集成了一个LDO。图2:SAW示波器和TI LMK03328时钟发生器的PSRR请在下方给我们留言,告诉我们你在正在研究的、最能从超低抖动中受益的应用。

2018-09-05 16:07:30

AD9520-0 / PCBZ,用于AD9520-0的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9520具有自动hoLDOver和灵活的参考输入电路,可

2020-04-03 09:59:24

AD9522-0 / PCBZ,用于AD9522-0的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

2019-02-22 09:34:18

AD9520-5 / PCBZ,用于AD9520-5的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9520具有自动hoLDOver和灵活的参考输入电路,可

2020-04-06 15:26:40

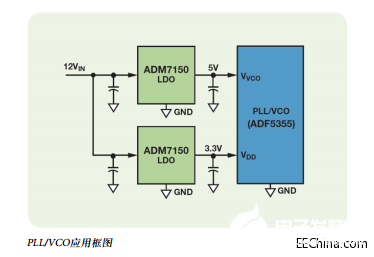

超低噪声调节器是怎样为VCO和PLL供电的

2021-04-06 08:05:27

AD9520-2 / PCBZ,用于AD9520-2的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9520具有自动hoLDOver和灵活的参考输入电路,可

2020-04-03 07:34:56

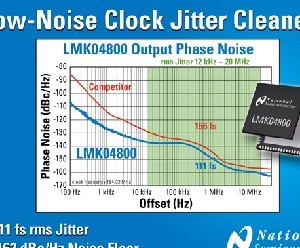

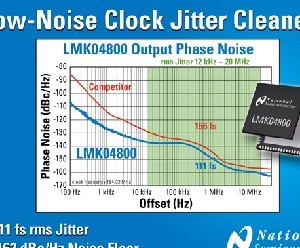

3200 MHz时的超低噪声:61-fs RMS抖动(12 kHz至20 MHz)RMS抖动67-fs(100 Hz至100 MHz)–156.5-dBc / Hz的本底噪声锁相环2PLL FOM为

2021-03-24 16:13:02

是4个分量(390 ps)的平方和的平方根?或者在级联结束时使用PLL来清除先前PLL和放大器的一些抖动。 DCM可以产生更低的抖动?以上来自于谷歌翻译以下为原文I need to produce a

2019-07-23 14:02:15

免费三分钟回拨电话,,绿色的,对号码有次数限制.有三分钟通话时长,,反其道而行不就又是三分钟,请各位灵活运用(见例)假如我的电话是1301309****,而我要打的电话是1386551****.把

2009-03-02 17:27:22

关于虚拟现实中立体显示技术研究知识点看完你就懂了

2021-06-03 06:00:25

DC1795A,用于LTC6950的演示板,具有时钟分配的1.4GHz低相位噪声,低抖动PLL。演示电路1795A采用具有时钟分配的LTC6950,1.4 GHz低相位噪声,低抖动PLL。为了便于

2019-02-25 09:55:24

用于处理高负载电流的LT1021BCH-5电压基准的典型应用。 LT1021是一款精密基准电压源,具有超低漂移和低噪声特性,极佳的长期稳定性以及对输入电压变化的几乎完全抗扰度。参考输出的源电流和吸收电流均高达10mA

2020-03-27 06:55:58

具有电流限制的升压输出电流的LT1021DCN8-10参考电压的典型应用。 LT1021是一款精密基准电压源,具有超低漂移和低噪声特性,极佳的长期稳定性以及对输入电压变化的几乎完全抗扰度。参考输出的源电流和吸收电流均高达10mA

2020-04-02 06:23:44

AD9522-4 / PCBZ,用于AD9522-4的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

2019-02-22 09:35:23

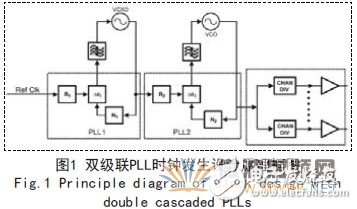

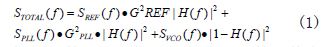

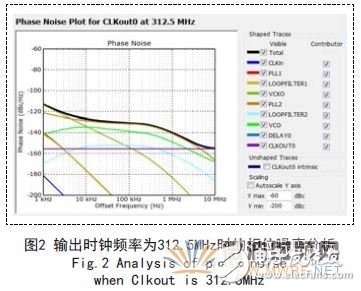

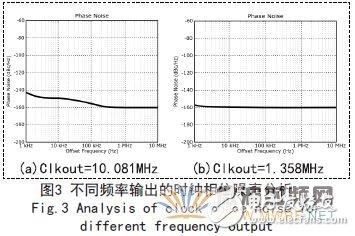

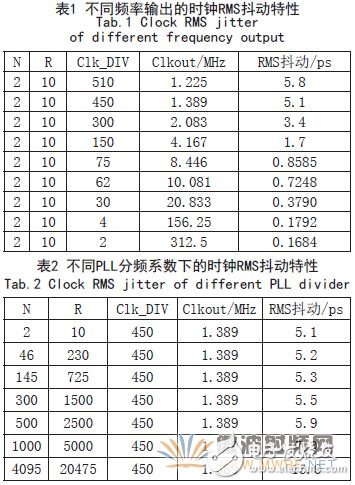

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

AD9522-5 / PCBZ,用于AD9522-5的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达24个输出。 AD9522具有自动保持功能和灵活的参考输入电路,可实现非常

2019-02-25 09:47:08

现需要为一个pd范围约在160-280uA的光电传感芯片选择一超低噪声跨阻放大器(最好增益可调,噪声nA及以下),OPA857的可测电流范围过小,寻求合适的选型推荐。如果可以,还希望推荐几个同样低噪声的后端ADC芯片,谢谢!

2024-07-31 07:57:46

AD9516-0 / PCBZ,用于AD9516-0评估板,2800 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9516具有自动保持功能和灵活的参考输入电路,可实现非常

2019-03-04 10:04:21

AD9518-1A / PCBZ,用于AD9518-1A的评估板,2500 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9518具有自动保持功能和灵活的参考输入电路,可实现非常

2019-03-05 09:20:31

(SYNERGY DXO11751220-5)组成。图1.基于MAX2880的12GHz超低相位噪声小数N分频PLL。主要特点:超低相位噪声:92-Femtosecond RMS抖动

2018-12-10 09:50:52

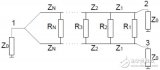

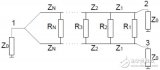

电阻、感抗、容抗、阻抗究竟谁是老大?三分钟理清它们的关系电感、电阻、电容电阻、感抗、容抗、阻抗四个名词活跃在各种电路中,它们是什么关系了?且听慢慢道来。一、电阻:这是我们最熟悉不过的东东了,在初中

2019-12-06 08:55:40

也无法写好。 明白这一点,你就会意识到,有些工作的确需要大块的时间,但如果不是提前做够铺垫,这些大块的时间并不会有效率。 所以我自己的习惯是“五分钟方案法”。也就是说: 一份完整的方案=5分钟构思

2015-08-07 14:06:32

本帖最后由 我想看看太阳 于 2022-6-9 11:52 编辑

让这个程序运行三分钟,停一分钟,循环下去,直到设置停止循环的位置,需要添加什么模块才能实现呢

2022-06-08 15:03:49

AD9517-3A / PCBZ,用于AD9517-3A的评估板,2000 MHz超低噪声PLL时钟合成器,集成VCO,时钟分频器。 AD9517具有自动保持功能和灵活的参考输入电路,可实现非常

2019-03-05 07:07:34

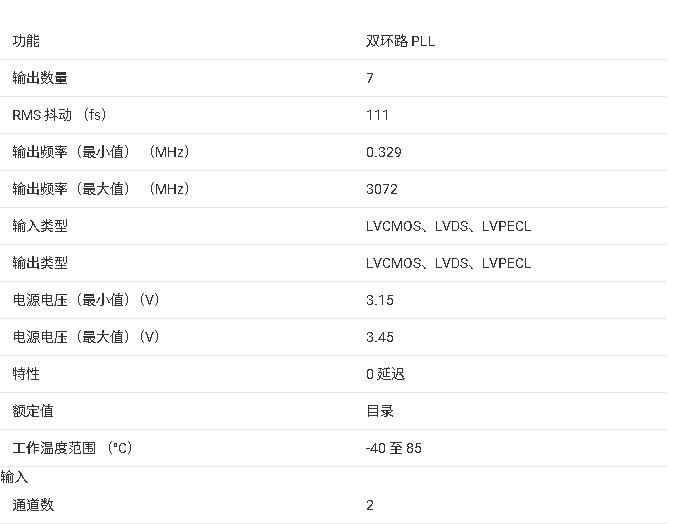

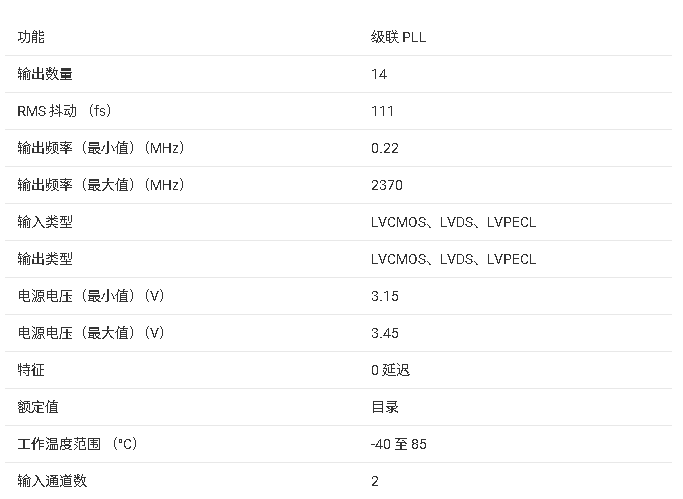

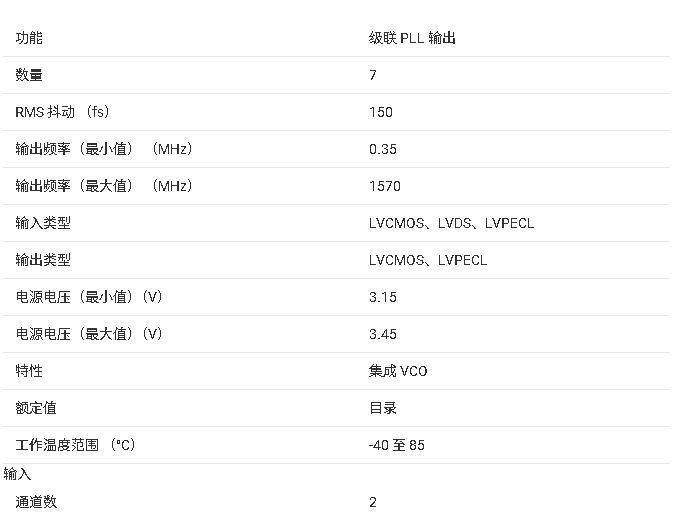

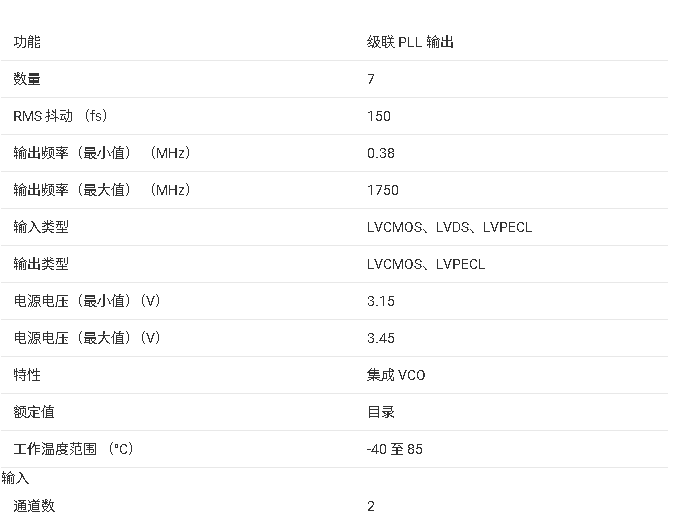

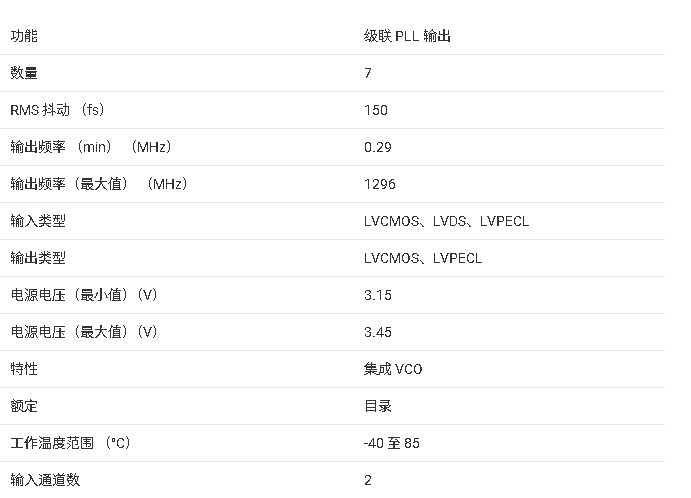

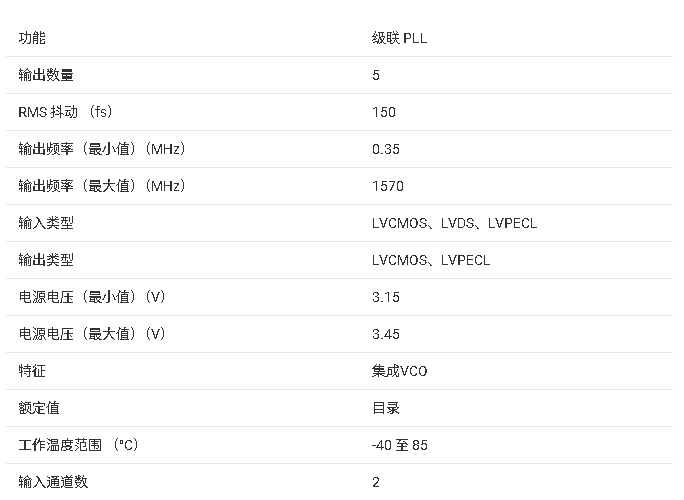

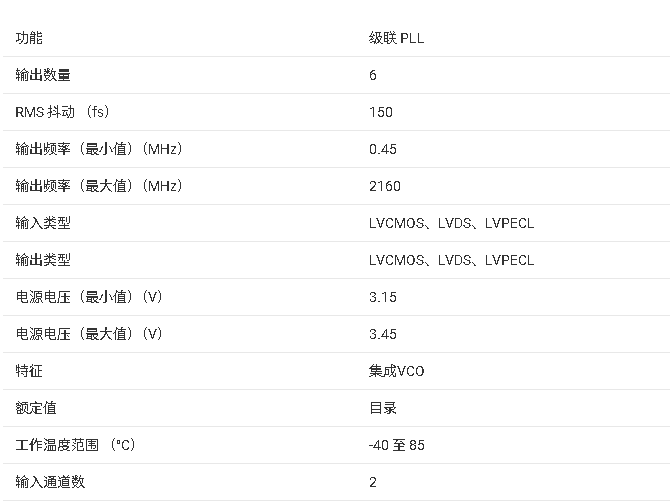

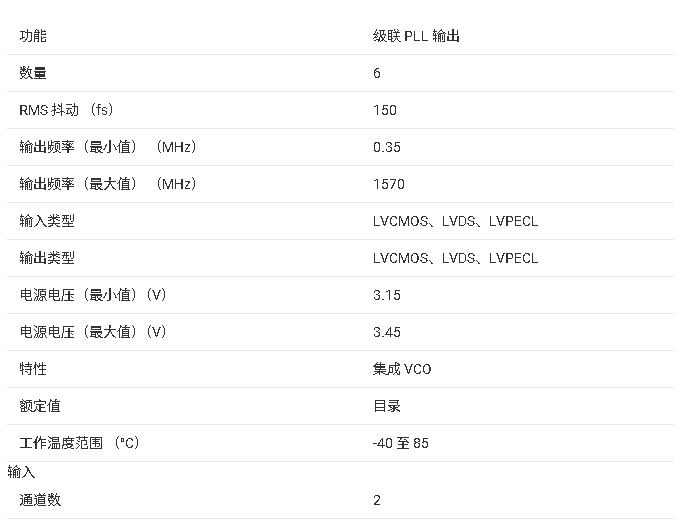

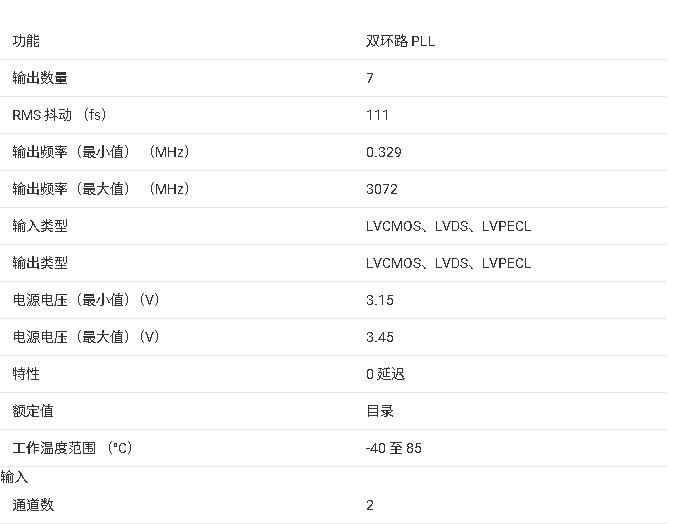

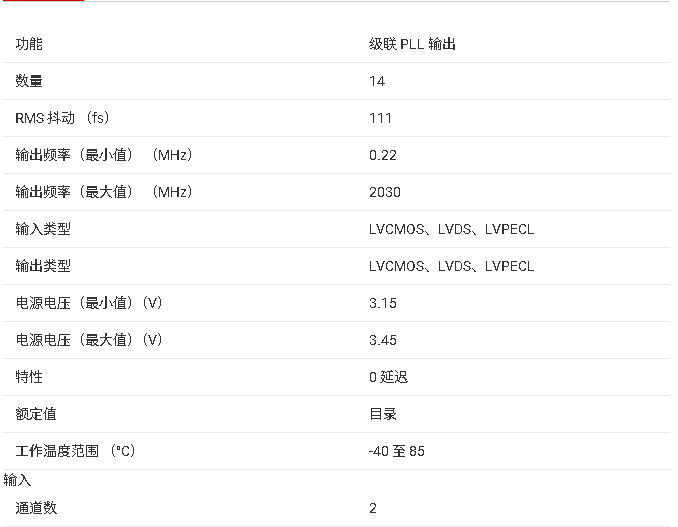

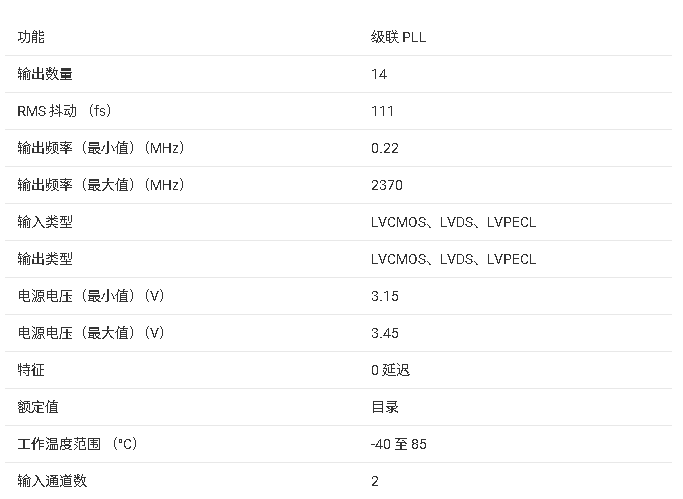

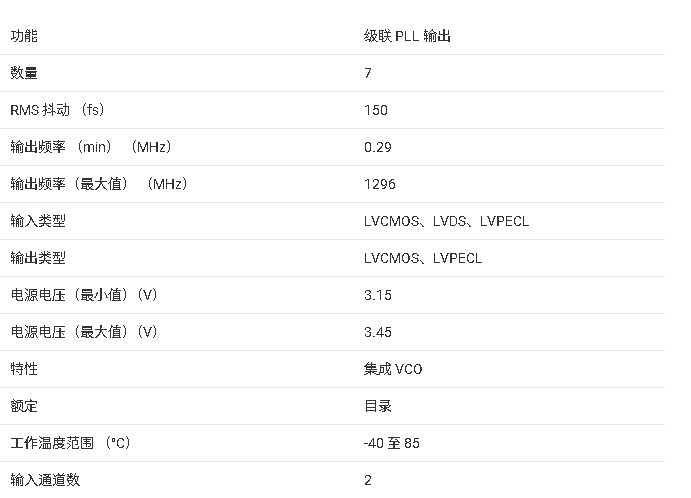

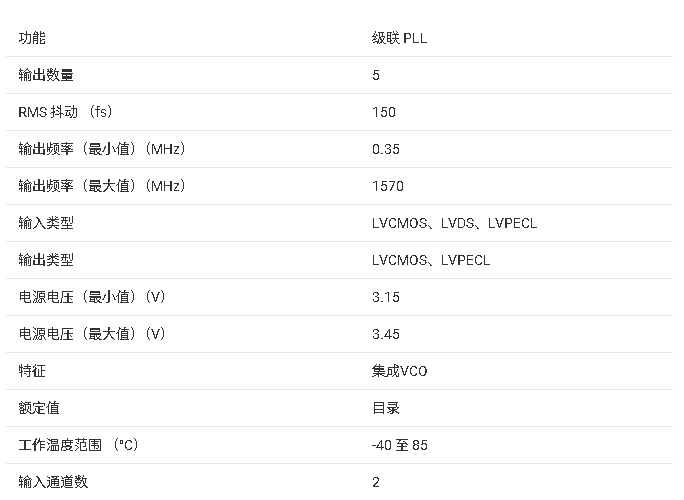

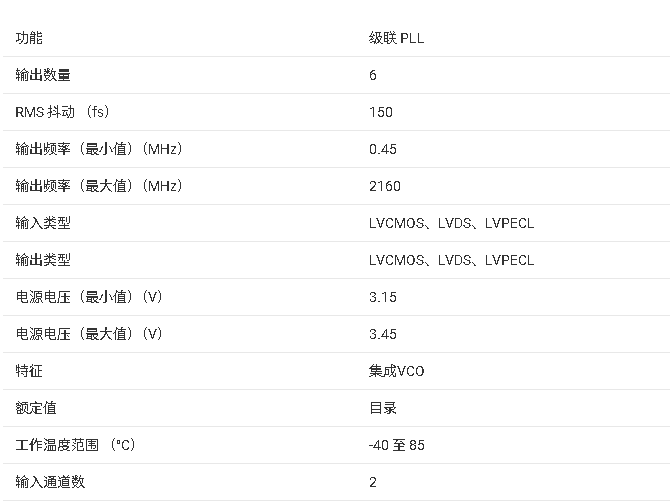

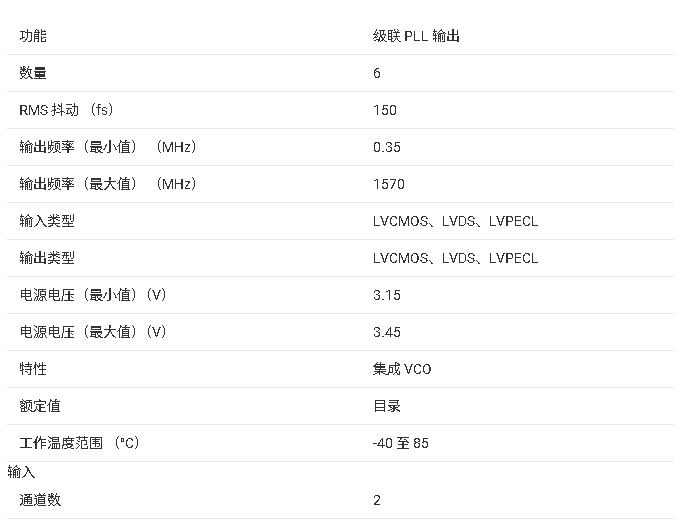

具有级联 PLL 的精密时钟调节器低噪声时钟抖动消除器 Function Cascaded PLLs Number of outputs 7 RMS jitter (fs

2022-12-02 13:48:04

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 4761

4761

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1853

1853

三分钟让你明白电

2009-11-12 08:18:26 71552

71552 MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1615

1615

美国国家半导体公司宣布推出一系列全新的时钟抖动滤除器,该系列产品拥有业界最低的相位噪声和均方根抖动性能

2011-03-23 09:33:48 2614

2614

级联SVG控制策略及死区补偿技术研究_杨荣峰

2017-01-08 13:49:17 0

0 苹果系统是以稳定著称,不过这位网友发来求助,称自己的iPhone6s三分钟时间重启了N次。并且拍了视频,系统为IOS10.2.1。

2017-02-25 10:18:07 2785

2785 首批小米扫地机器人于4月6日如约在台湾地区开售,售价8895台币(约合1915元人民币),开售三分钟,5000台扫地机器人在小米台湾官网即告售罄。

2017-04-07 10:45:04 1424

1424 在单片机中,为了获得更高的内部时钟频率,正越来越多地使用锁相环(Phase Locked Loop,PLL)电路。由于融合了PLL电路,能够得到更好的性能,同时还降低了总体噪声。Microchip

2018-04-24 10:25:07 0

0 无线能量传输(WPT) 是指发射和接收单元之间的能量传输,这项技术主要用于对电子设备进行无线充电,比如手机和电动汽车。虽然无线能量传输可以带来多项优势,但它仍面临一些亟待解决的难题。

2018-05-17 15:06:00 7210

7210 功分器在微波电路中用途非常广泛,特别是在相控阵/固态功率合成如火如荼的今天,几乎每个微波产品里都有它的身影。

2018-05-24 10:56:00 40198

40198

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2020-09-23 10:45:00 2

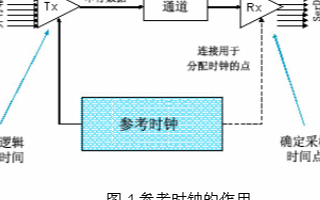

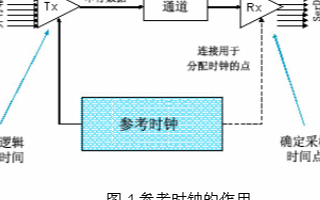

2 发射机必须用适当的因数乘以参考时钟获得数据速率,才能确定逻辑变换定时。例如,对于100 MHz参考时钟和5 Gb/s输出信号,发射机将用PLL给参考时钟乘以因数50。PLL乘法器不仅放大时钟抖动,还

2020-08-05 08:57:09 7881

7881

三分钟来快速回顾一下! 日本计划减少对中国无人机依赖 11月2日消息,日本为保护国家敏感信息数据安全,正计划在政府采购无人机时,排除与中企相关的产品,具体排除部分主要围绕信息技术、供应链、网络安全和知识产权等方面。与此同

2020-11-23 18:05:56 2861

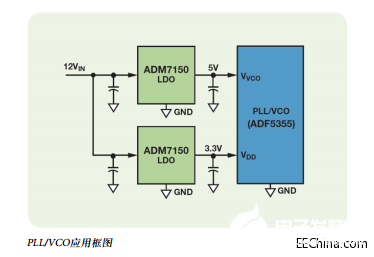

2861 该12 V系统轨由感应开关元件生成,该元件会在轨上引起波纹和噪声。为了获得干净的供电轨,需要超低噪声调节器来生成5 V供电轨,为宽带PLL和VCO供电。在5 V供电轨上出现的任何噪声或波纹都会使PLL或VCO性能下降。

2021-03-15 15:35:10 2584

2584

具 PLL 的 5 输出超低抖动时钟分配器提供独特的多芯片输出同步方法

2021-03-19 10:54:50 10

10 电子发烧友网为你提供三分钟概述8类常用元器件资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-28 08:40:58 6

6 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 KOYUELEC光与电子提供技术支持,有容微电子GM50101:超低附加抖动时钟缓冲器。

2022-05-07 11:40:15 1917

1917 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 三分钟看懂工字型功率电感外观破损的常见原因gujing 编辑:谷景电子 关于功率电感的相关问题最近给大家做了一些小科普,有关注选型的、有关于性能特点方面、以及有关于如何解决功率电感使用中温升高

2022-11-09 13:54:58 1219

1219

什么是超精密运动控制技术? 超精密运动控制技术是一门集精密机械、精密控制、精密驱动、精密传感、精密测量、精密集成技术于一体,实现在纳米精度范围内的运动控制的综合技术,也是三英精控最主要的核心技术

2023-01-12 11:22:59 4151

4151 采用PLL的时钟发生器广泛用于网络设备中,用于生成高精度和低抖动参考时钟或保持同步网络操作。大多数时钟振荡器使用理想、干净的电源给出其抖动或相位噪声规格。然而,在实际的系统环境中,电源可能会因板载开关电源或嘈杂的数字ASIC而受到干扰。为了在系统设计中实现最佳性能,了解这种干扰的影响非常重要。

2023-03-08 15:33:00 2184

2184

1.1.1. 抖动定义和分类 ITU-T G.701对抖动的定义为:“抖动是指数字信号在短期内相对于理想位置发生的偏移重大影响的短时变化”。 对于真实物理世界中的时钟源,比如晶振、DLL、PLL,它们的时钟输出周期都不可能是一个单点的固定值,而是随时间而变化的

2023-03-10 14:54:32 1847

1847

三分钟看懂贴片电感器怎么看大小 编辑:谷景电子 在贴片电感器的选型中有两个特别需要注意的地方那就是封装规格大小和电性能信息。这两个方面的信息都直接影响到选型是不是正确的,所以要做好贴片电感器的选型

2023-04-07 13:41:48 1955

1955 本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 2462

2462

理想值附近的一个范围内,从而造成相邻的时钟边沿存在偏差。在时序分析时,时钟抖动是一个重要的因素。多种因素会导致时钟抖动,包括PLL回路噪声、电源纹波、热噪声以及信号之间的串扰等。

2023-06-09 09:40:50 3109

3109

Erupt一个通用后台管理框架,据说有 超低代码量 、 零前端代码 、零 CURD操作 、无需建表 ,纯Java注解开发 等特色,号称三分钟就可以搭建一个完整的后台管理系统。

2023-07-28 11:27:52 1953

1953

电子发烧友网站提供《Brocade帮助Netzlink实现三分钟云服务供应.pdf》资料免费下载

2023-08-29 10:12:59 0

0 快乐解说MCU:三分钟,带你了解低功耗MCU

2023-09-18 10:56:24 2102

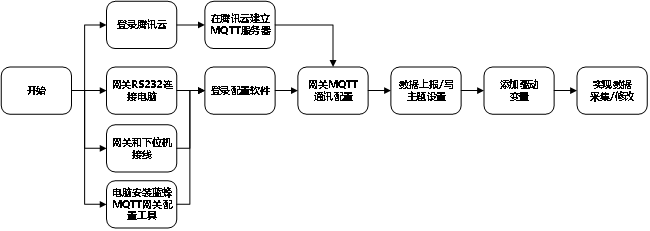

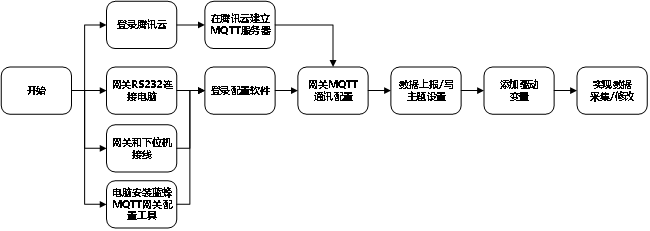

2102 三分钟实现MQTT协议网关串口连接三菱FX3UPLC上传腾讯云

2023-10-23 16:23:36 1910

1910

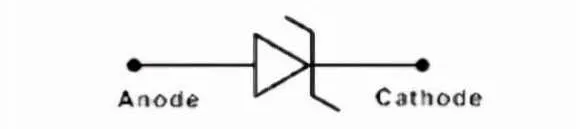

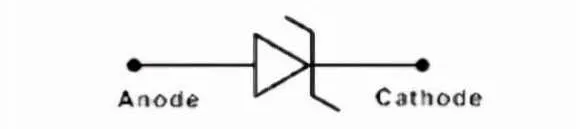

三分钟看懂雪崩光电二极管

2023-11-23 09:09:06 3469

3469

三分钟了解飞创直线电机运动模组特点、选型及应用-FCL系列

2024-02-05 16:28:28 1321

1321

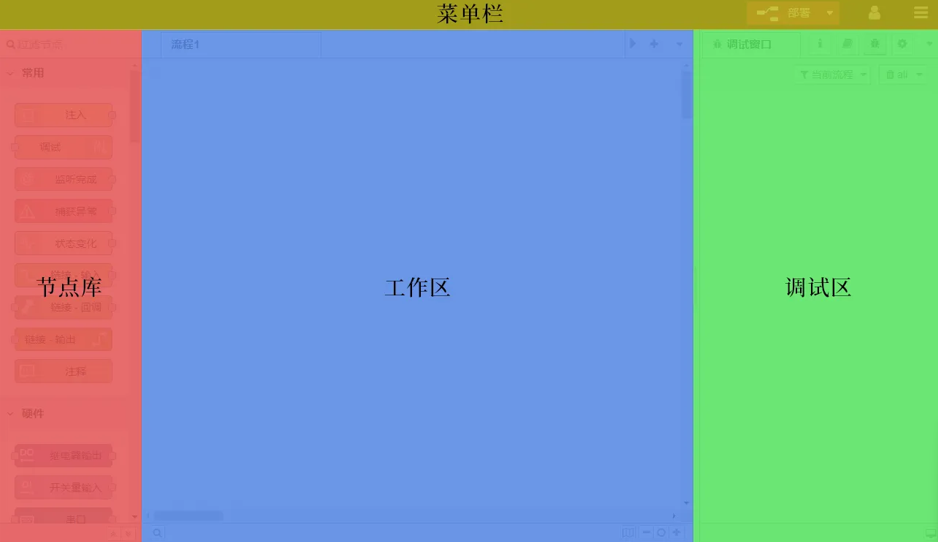

通过这短短三分钟的教程,你已经掌握了Node-RED的基本操作。你可以利用Node-RED的强大功能来创建更复杂的数据流和自动化任务,无论是物联网应用、API集成还是数据处理。Node-RED简化了编程过程,让开发更直观、更高效。继续探索Node-RED,你会发现更多强大且有趣的功能。

2024-06-27 17:09:16 6856

6856

电子发烧友网站提供《LMK04714-Q1符合JESD204B/C标准的汽车级、超低噪声、双环路时钟抖动清除器数据表.pdf》资料免费下载

2024-08-20 10:37:26 0

0 电子发烧友网站提供《LMK04832-SEP符合JESD204B/C标准的航天级、超低噪声、双环路时钟抖动清除器数据表.pdf》资料免费下载

2024-08-20 10:39:30 0

0 电子发烧友网站提供《LMK04368-EP符合JESD204B/C标准的超低噪声、双环路时钟抖动清除器数据表.pdf》资料免费下载

2024-08-20 09:52:49 0

0 电子发烧友网站提供《LMK04832-SP符合JESD204B标准的航天级、超低噪声、双环路时钟抖动清除器数据表.pdf》资料免费下载

2024-08-20 09:32:15 0

0 电子发烧友网站提供《LMK04000系列低噪声时钟抖动消除器数据表.pdf》资料免费下载

2024-08-21 09:56:12 0

0 电子发烧友网站提供《LMK03318超低噪声抖动时钟发生器系列数据表.pdf》资料免费下载

2024-08-21 09:53:40 0

0 电子发烧友网站提供《LMK0482x超低噪声JESD204B兼容时钟抖动消除器数据表.pdf》资料免费下载

2024-08-21 09:19:01 1

1 电子发烧友网站提供《带双环路PLL且符合JESD204B标准的LMK04832超低噪声时钟抖动清除器数据表.pdf》资料免费下载

2024-08-21 09:20:21 0

0 电子发烧友网站提供《LMK04906带6路可编程输出的,超低噪声时钟抖动清除器和乘法器数据表.pdf》资料免费下载

2024-08-21 09:21:31 0

0 电子发烧友网站提供《具有双环路PLL的LMK04228超低噪声且符合JESD204B标准的时钟抖动清除器数据表.pdf》资料免费下载

2024-08-21 09:12:01 0

0 电子发烧友网站提供《LMK04208具有双环PLL的低噪声时钟抖动消除器数据表.pdf》资料免费下载

2024-08-22 11:22:10 0

0 电子发烧友网站提供《LMK04816具有双环PLL的三输入低噪声时钟抖动消除器数据表.pdf》资料免费下载

2024-08-22 12:21:23 0

0 电子发烧友网站提供《LMK0480x低噪声时钟抖动消除器数据表.pdf》资料免费下载

2024-08-22 11:16:04 0

0 电子发烧友网站提供《LMK04616超低噪声和低功耗时钟抖动消除器数据表.pdf》资料免费下载

2024-08-22 11:42:40 0

0 电子发烧友网站提供《LMK04610超低噪声和低功耗时钟抖动消除器数据表.pdf》资料免费下载

2024-08-22 10:11:59 2

2 通过上一期我们了解到:数字电子产品中电源轨噪声和时钟抖动是有关联的,以及测量电源轨噪声的方案,接下来我们基于实际测量,揭示电源轨噪声对系统时钟抖动的影响。

2024-11-22 16:11:22 1176

1176

随着现代电子系统对高精度、高可靠性时钟信号需求的不断提升,时钟抖动成为影响系统性能的关键因素。核芯互联科技有限公司重磅推出CLF04828超低噪声去抖时钟,凭借其领先的双PLL架构、超低相位噪声和灵活的输出配置,为多领域高性能应用提供了强大的技术支持。

2025-03-04 12:38:02 1465

1465

LMK04208是一款高性能时钟调节器,具有卓越的时钟抖动清除功能, 生成和分发具有高级功能,以满足下一代系统要求。 双环路PLLatinum™架构能够 使用低噪声VCXO模块的RMS抖动(12

2025-09-13 10:16:27 1116

1116

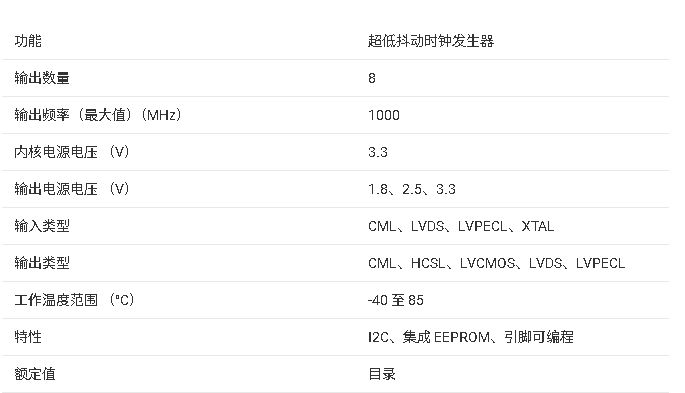

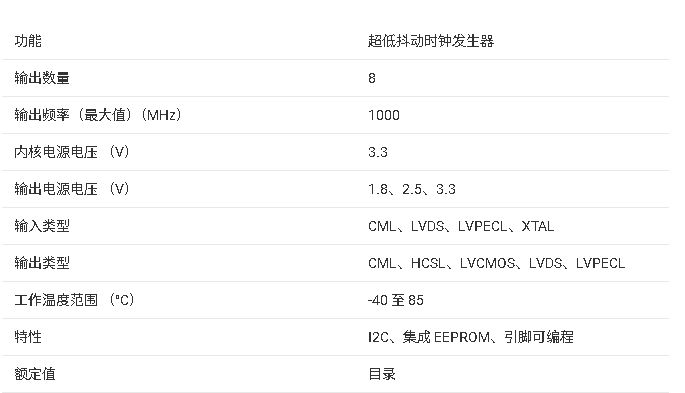

LMK03318器件是一款超低噪声PLLATINUM™时钟发生器,具有一个小数N频率合成器,集成了VCO、灵活的时钟分配和扇出,以及存储在片上EEPROM中的引脚可选配置状态。该器件可以为各种多千兆

2025-09-13 17:35:11 1194

1194

LMK03328器件是一款超低噪声时钟发生器,具有两个集成VCO的小数N频率合成器、灵活的时钟分配和扇出,以及存储在片内EEPROM中的引脚可选配置状态。该器件可为各种多千兆串行接口和数字器件生成

2025-09-14 09:37:32 888

888

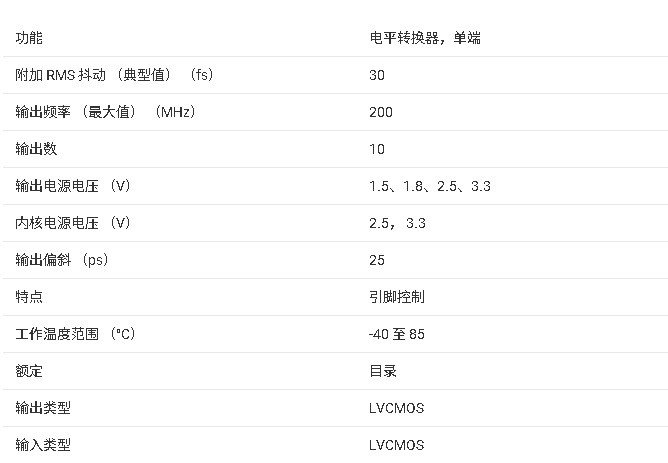

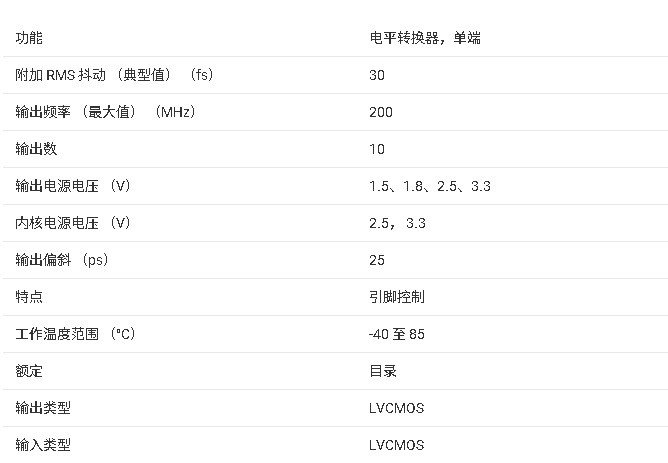

LMK00101是一款高性能、低噪声的LVCMOS扇出缓冲器,可分配 10个来自差分、单端或晶体输入的超低抖动时钟。The LMK00101 支持同步输出使能,实现无毛刺作。超低偏斜、低抖动和 高

2025-09-15 15:41:45 745

745

。该LMK03806集成了高性能整数N PLL、低噪声VCO和可编程输出分频器,可从低成本晶体为SONET、以太网、光纤通道、XAUI、背板、PCIe、SATA和网络处理器生成多个参考时钟。

2025-09-16 09:45:23 660

660

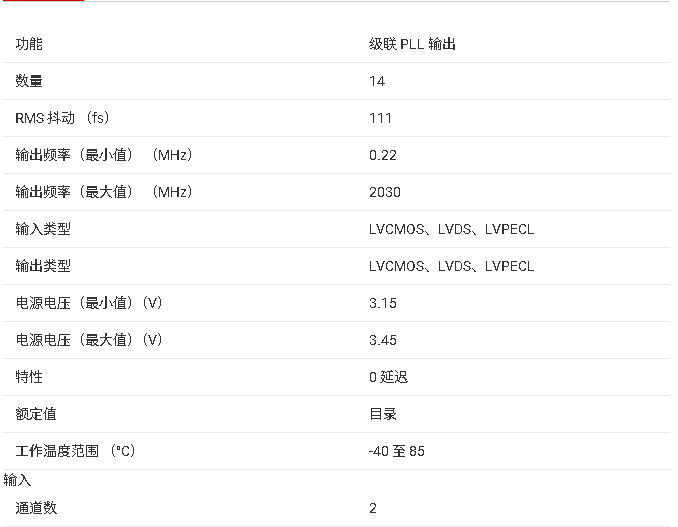

LMK0480x 系列是业界性能最高的时钟调节器,具有卓越的 时钟抖动清理、生成和分配,具有满足下一代需求的高级功能 系统要求。双回路PLLatinum 该架构能够使用低噪声VCXO模块实现111

2025-09-16 10:37:21 687

687

LMK0480x 系列是业界性能最高的时钟调节器,具有卓越的 时钟抖动清理、生成和分配,具有满足下一代需求的高级功能 系统要求。双回路PLLatinum 该架构能够使用低噪声VCXO模块实现111

2025-09-16 10:42:44 728

728

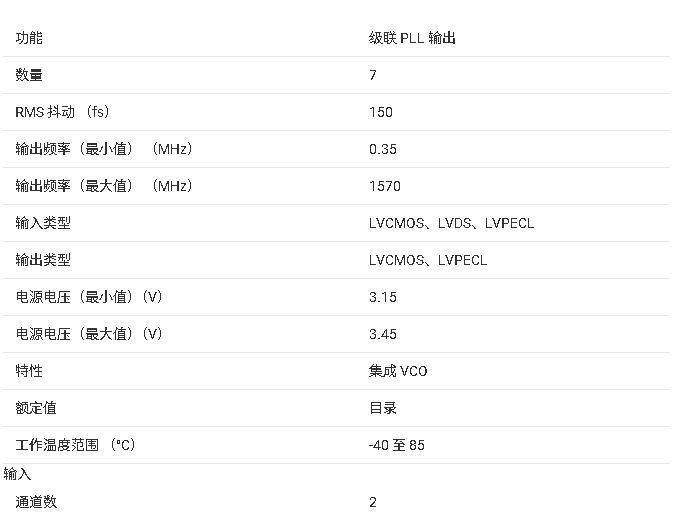

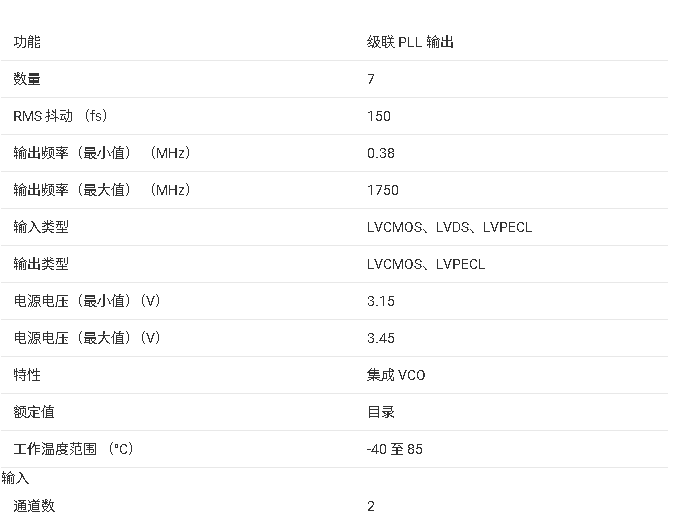

LMK04000系列精密时钟调节器提供低噪声抖动清除、时钟乘法和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

2025-09-17 09:22:37 643

643

LMK04000系列精密时钟调节器提供低噪声抖动清除、时钟乘法和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

2025-09-17 09:27:32 669

669

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

2025-09-18 09:55:12 645

645

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

2025-09-18 10:45:32 670

670

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

2025-09-18 11:33:20 596

596

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

2025-09-18 14:06:01 580

580

可以使用直流和交流耦合来提供。不仅限于JESD204B应用,14个输出均可单独配置为传统高性能时钟系统输出。 超低噪声时钟抖动消除器SC6301具有高性能

2024-02-19 09:41:40

电子发烧友App

电子发烧友App

评论