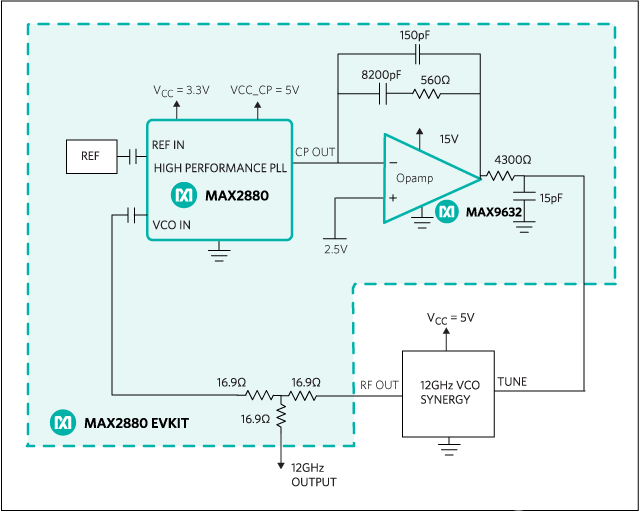

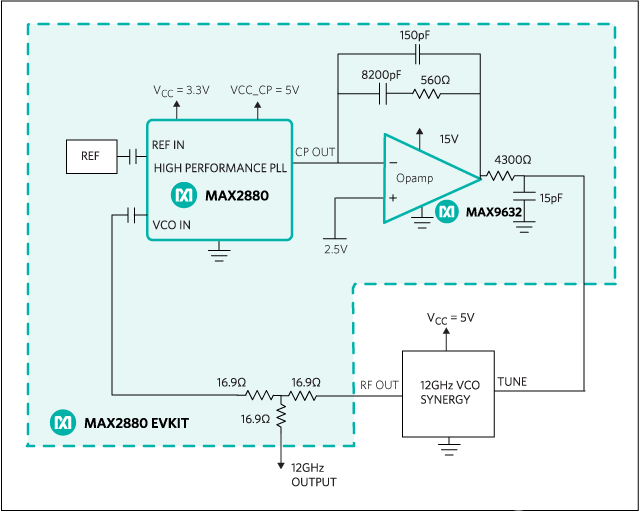

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)组成。

2018-12-10 10:02:53 1718

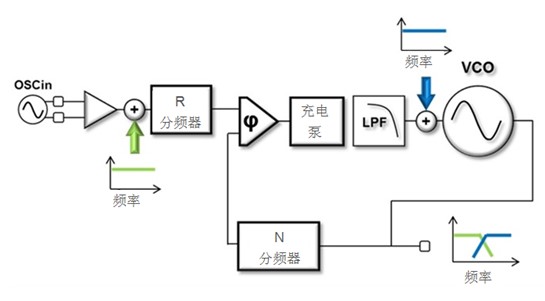

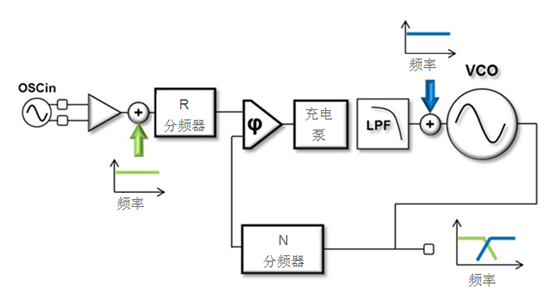

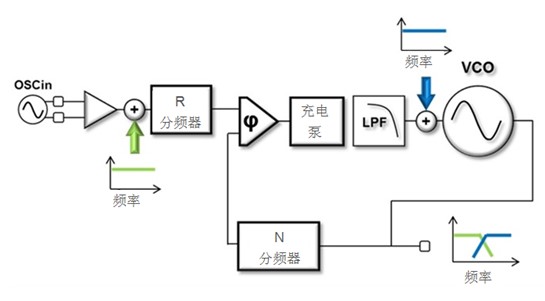

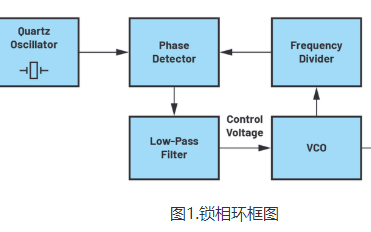

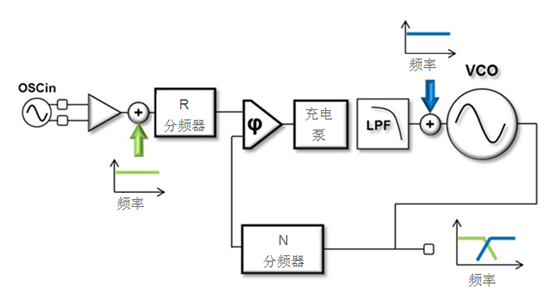

1718 锁相环英文名称PLL(Phase Locked Loop),中文名称相位锁栓回路,现在简单介绍一下锁相环的工作原理。

2023-04-28 09:57:31 9825

9825

本文是关于相位噪声建模、仿真和传播在锁相环中的应用的第三部分。文章介绍了相位噪声的理论和测量方法,并探讨了相位噪声的分析与建模过程。

2023-10-27 11:42:47 2939

2939

PLL(锁相环)电路原理是什么?

2022-01-21 07:03:37

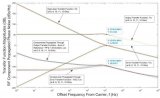

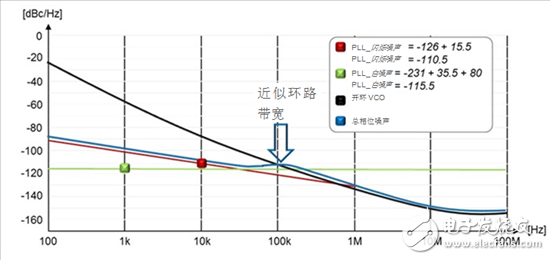

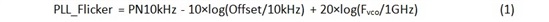

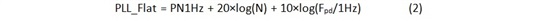

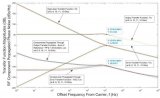

:锁相环中的两个已建模的噪声源(绿色和蓝色)及其对系统输出的频率响应环路带宽内部(低通频率响应)PLL产生的噪声分为两个部分——闪烁噪声和白噪声,但环路带宽外部(高通频率响应)的噪声在数据表中通常表示为开环VCO性能。…

2022-11-17 06:57:28

),因为它具有更佳的总带内相位噪声。相反,若要求具有较小的频率步进,则应首选小数N 分频PLL(如ADF4153),因为它的总噪声性能优于整数N 分频PLL。相位噪声是一个基本的PLL 规格,但数据

2018-10-22 09:45:08

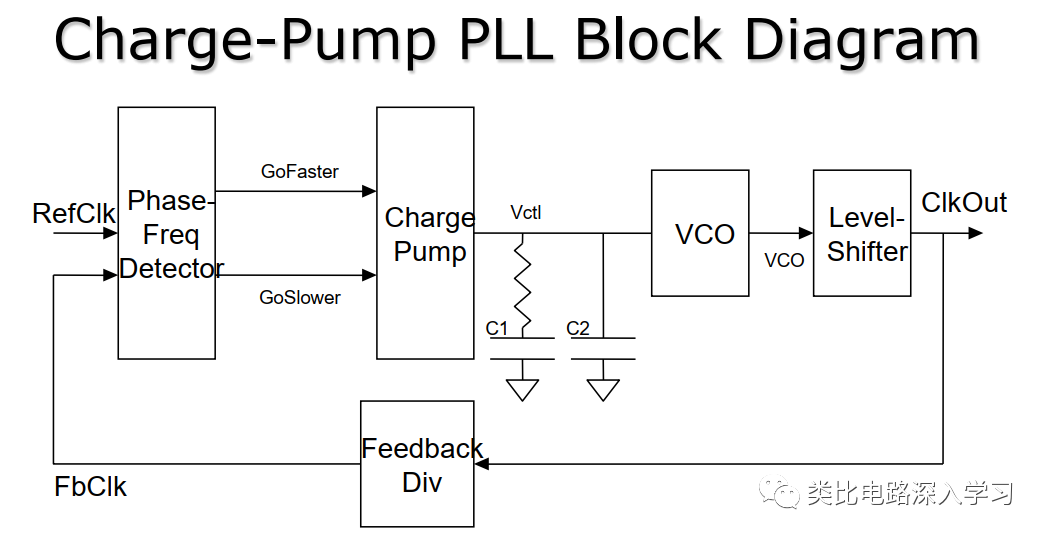

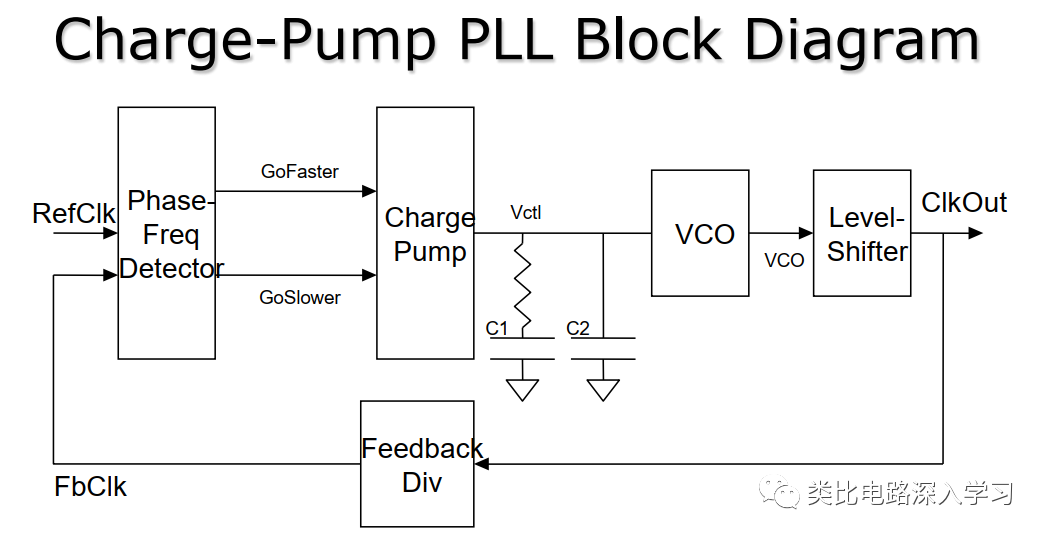

电荷泵锁相环的基本原理是什么?电荷泵锁相环的噪声模型与相位噪声特性是什么?电荷泵锁相环的相位噪声与环路带宽关系是什么?

2021-06-07 06:57:53

锁相环,而他们都是属于软件锁环的范畴。在电力仿真软件中,一般都有PLL模块,只需要将该模块应用一下即可实现锁相环的功能,即该模块可输出系统相角。其实,所谓的PLL模块就是实现上面说的这么一团东西的,在

2015-01-04 22:57:15

本帖最后由 gk320830 于 2015-3-7 20:18 编辑

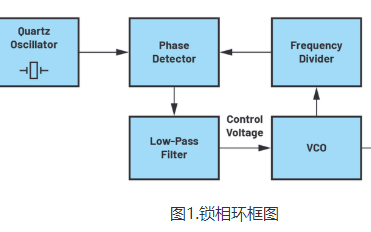

锁相环的原理,特性与分析所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL 表示。

2008-08-15 13:18:46

电路会不断根据外部信号的相位来调整本地晶振的时钟相位,直到两个信号的相位同步。编辑添加图片注释,不超过 140 字(可选)在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以

2022-05-31 19:58:27

在使用K60的过程中发现自己pllinit()不清楚,才发觉自己锁相环的概念还不懂,so,赶紧补补……锁相环(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制

2021-11-04 08:57:18

的步长。 PLL系列产品有几种不同尺寸可供选择从0.866英寸x 0.63英寸到小至0.5英寸x 0.5英寸。整数N和分数N低相位噪声紧凑的尺寸RFS4300A-LF锁相环RFS4500A-LF锁相环

2021-04-03 17:00:58

信号源的任何应用的理想选择,并且利用微带或陶瓷谐振器拓扑结构可提供出色的相位噪声性能。测试仪器雷达系统SFS10500H-LF锁相环SFS10625H-LF锁相环SFS10640H-LF锁相环

2021-04-03 17:05:46

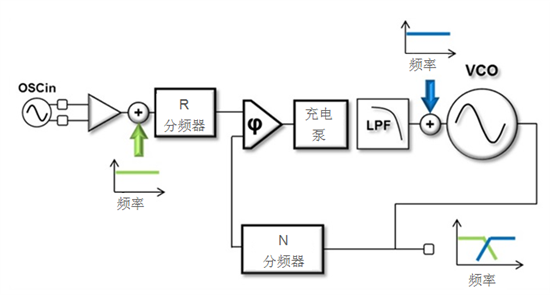

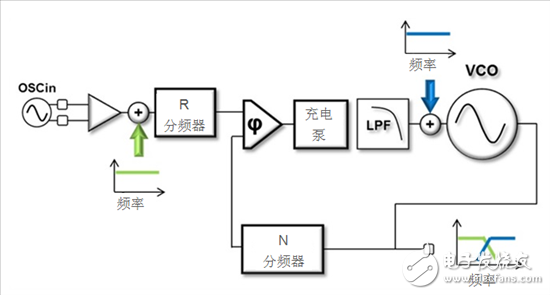

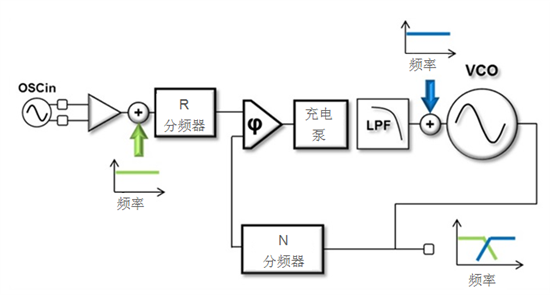

(ADI公司内部PLL电路仿真器)来演示不同电路性能参数。基本配置:时钟净化电路锁相环的最基本配置是将参考信号(FREF)的相位与可调反馈信号(RFIN)F0的相位进行比较,如图1所示。图2中有一个在

2019-10-02 08:30:00

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。今天斑竹带来干货好文,参考上述各种应用来

2019-01-28 16:02:54

本文设计了一种宽频率范围的CMOS锁相环(PLL)电路,通过提高电荷泵电路的电流镜镜像精度和增加开关噪声抵消电路,有效地改善了传统电路中由于电流失配、电荷共享、时钟馈通等导致的相位偏差问题。设计了

2019-07-08 07:37:37

阶Δ∑调制器作为VCO。初级输出在频率和相位上都是锁定的。倍频的二次输出。输出用于可选的锁定检测。不消耗CPU。附加存档包含组件库、组件数据表和几个用于PSoC5的演示项目。请阅读Read M.TXT中的安装

2018-11-07 17:06:05

也许你也会跟我一样认为典型数据表中的某些规格难以理解,这是因为其中涵盖了一些你不太熟悉的隐含惯例。对许多RF系统工程师而言,其中一种规格便是锁相环(PLL)中的相位噪声。当信号源被用作本机振荡器

2018-08-31 09:46:39

噪声。相反,若要求具有较小的频率步进,则应首选小数N分频PLL(如ADF4153),因为它的总噪声性能优于整数N分频PLL。相位噪声是一个基本的PLL规格,但数据手册无法针对所有可能的应用指定

2017-03-17 16:25:46

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO

2018-12-10 09:50:52

锁相环频率合成器:相位噪声问题和宽带循环:

In this chapter we locate the context of this thesis by introducing

2009-07-25 17:18:33 0

0 锁相环常见问题解答:1 AD公司锁相环产品概述2 PLL主要技术指标21 相位噪声22 参考杂散23 锁定时间3 应用中常见问题31 PLL芯片接口相关问题311 参考晶振有哪些要求

2009-09-27 15:43:34 95

95 Skyworks Solutions 的 SKY72302-21 是一款锁相环,频率为 400-6100 MHz,相位噪声 -80

2023-06-12 17:22:25

Skyworks Solutions 的 SKY72300-362 是一款锁相环,频率为 100-2100 MHz,相位噪声 -91

2023-06-12 17:30:57

利用锁相环进行载波跟踪是获取本地载波的一种重要方法,针对锁相环的噪声性能和跟踪速度不能同时达到最优的限制,在锁相环PLL中引入自适应模块,根据环路所处

2010-11-25 17:19:33 29

29 锁相环原理

锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位同步。因锁相环可以

2007-08-21 14:46:04 5484

5484 锁相环(PLL)和相移键控(PSK)系统的相位噪声振荡器的相位噪声有可能导致相位变换的错误检测,即在用相位键控法进行数字调制时产生误码。例如,

2008-11-24 12:40:59 2307

2307

锁相环CD4046应用

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。它广泛应用于广播通信、

2009-03-18 15:11:18 2405

2405

锁相环(PLL),锁相环(PLL)是什么意思

PLL的概念

我们所说的PLL。其

2010-03-23 10:47:48 6368

6368 模拟锁相环,模拟锁相环原理解析

背景知识:

锁相技术是一种相位负反馈控制技术,它利用环路的反馈原理来产生新的频率点。它的主要

2010-03-23 15:08:20 6264

6264 本文涉及的锁相环路是基于相位控制的时钟恢复系统。目的是用锁相环电路-PLL和DLL实现USB2.0收发器宏单远UTM的时钟恢复木块。其中PLL环路构成的时钟发生器奖外部晶振的12MHZ的正弦信号

2011-03-03 14:58:34 51

51 本书是图解电子工程师实用技术丛书之一,本书主要介绍锁相环(PLL)电路的设计与应用,内容包括PLL工作原理与电路构成、PLL电路的传输特性、PLL电路中环路滤波器的设计方法、PLL电路

2011-09-14 17:55:24 0

0 锁相环英文为PLL,即PLL锁相环。可以分为模拟锁相环和数字锁相环。两种分类的锁相环原理有较大区别,通过不同的锁相环电路实现不同的功能。

2011-10-26 12:40:28

锁相环是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。锁相环可用来从固定的低频信号生成稳定的输出高频信

2012-06-08 18:09:18 355

355 利用锁相环的等效噪声模型,重点分析电荷泵锁相环系统的相位噪声特性,得出系统噪声特性的分布特点以及与环路带宽的关系。

2012-11-22 10:44:47 23975

23975 如何设计并调试锁相环(PLL)电路 pdf

2016-01-07 16:20:08 0

0 PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。

2017-05-22 09:16:18 56551

56551

PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

2017-05-22 10:11:40 13196

13196

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2018-01-22 11:18:45 15350

15350

锁相环(phase locked loop),顾名思义,就是锁定相位的环路。学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出

2018-02-21 11:43:00 49580

49580

也许你也会跟我一样认为典型数据表中的某些规格难以理解,这是因为其中涵盖了一些你不太熟悉的隐含惯例。对许多RF系统工程师而言,其中一种规格便是锁相环(PLL)中的相位噪声。当信号源被用作本机振荡器

2018-07-02 09:37:36 4849

4849

通过演示简要介绍锁相环(PLL)中可实现的领先相位噪声和杂散性能。

2019-05-21 06:23:00 6527

6527 锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

2019-09-20 07:05:00 4322

4322

锁相在无线系统和需要在电路板上实现精确时钟和信号同步的系统中,环路具有许多重要功能。使用PLL可能是比重复调整PCB中走线长度以补偿承载并行或串行数据的通道中的偏差更好的选择。通过与压控振荡器(VCO)同步,锁相环也可用于消除参考信号的相位噪声。

2019-07-23 10:56:47 4586

4586 的相位变换,提出了一种基于锁相环(PLL)的QPSK调制器。由于采用了三输入异或门和求和电路,该系统中的锁相环电路不同于传统的锁相环电路。利用这些附加组件,所提出的PLL在QPSK信号中提供连续的相位变化。因此,当使用所述电路时,传输QPSK信号所需的带宽

2020-05-15 08:00:00 3

3 锁相环路是一种反馈控制电路,简称锁相环( PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常

2020-08-06 17:58:25 26

26 锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

2020-10-06 14:43:00 5774

5774

CN-0369:低相位噪声的转换锁相环频率合成器

2021-03-20 13:21:15 7

7 MT-086: 锁相环(PLL)基本原理

2021-03-21 01:00:51 31

31 LTC6950:1.4 GHz低相位噪声、低抖动锁相环,带时钟分布数据表

2021-04-19 12:13:04 3

3 锁相环(Phase Locked Loop,PLL)是一个闭环负反馈相位控制系统,至少包含3个基本单元电路。

2021-04-27 15:17:11 7422

7422

AD9578:双锁相环精密合成器数据表

2021-05-13 13:45:46 1

1 AD9576:双锁相环异步时钟发生器数据表

2021-05-16 12:57:55 0

0 AD800/AD802:时钟恢复和数据重定时锁相环数据表

2021-05-18 14:11:56 9

9 也许你也会跟我一样认为典型数据表中的某些规格难以理解,这是因为其中涵盖了一些你不太熟悉的隐含惯例。对许多RF系统工程师而言,其中一种规格便是锁相环(PLL)中的相位噪声。当信号源被用作本机振荡器

2021-11-24 15:40:06 3348

3348

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

2022-03-29 09:54:55 15826

15826 锁相放大器和相位表(数字相位测量仪)是两种常用于从振荡信号中获取相位信息的仪器。锁相放大器可以被视为开环相位检测器。相位是由本地振荡器、混频器和低通滤波器直接计算出来的。

2022-06-21 10:10:12 1896

1896 切勿让不良参考信号破坏锁相环/合成器中的相位噪声

2022-11-02 08:15:59 1

1 如何根据基本的数据表规格估算出P L L的相位噪声

2022-11-03 08:04:29 0

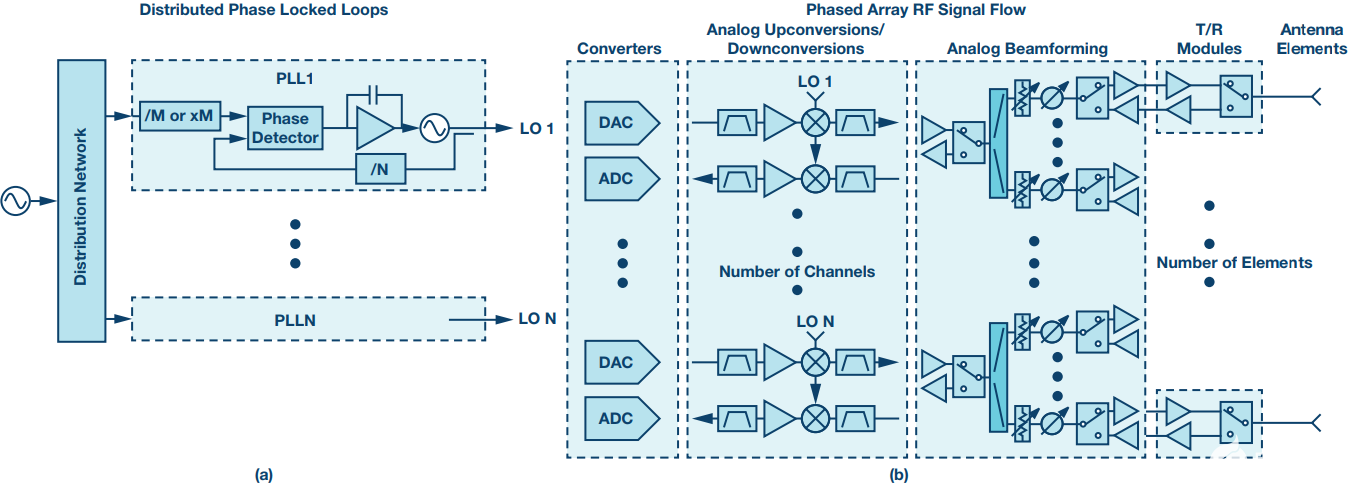

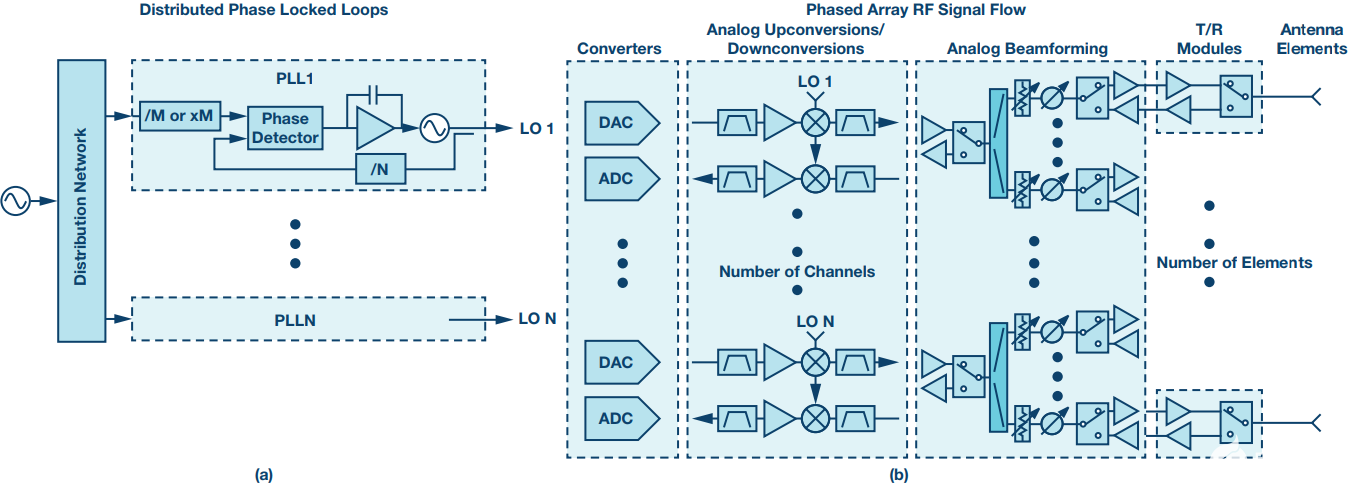

0 对于数字波束成形相控阵,LO生成考虑的常见实现方法是将公共参考频率分配给分布在天线阵列内的一系列锁相环。利用这些分布式锁相环,评估组合相位噪声性能的方法在当前文献中没有很好的记录。

2022-12-22 16:26:39 1954

1954

锁相环 (PLL) 电路存在于各种高频应用中,从简单的时钟清理电路到用于高性能无线电通信链路的本振 (LO),再到矢量网络分析仪 (VNA) 中的超快速开关频率合成器。本文解释了锁相环电路的一些构建模块,并参考了每种应用,以帮助指导新手和锁相环专家导航器件选择以及每种不同应用固有的权衡取舍。

2022-12-23 14:03:54 6671

6671

本应用笔记详细介绍了集成外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880)、基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)组成。

2023-01-16 11:27:08 2339

2339

PLL锁相环倍频是一种用于改变输入信号频率的技术,它可以将输入信号的频率放大或缩小,以达到某种特定的目的。

2023-02-14 15:56:35 3653

3653 PLL是指锁相环,是一种用于控制频率和相位的电路,它可以将一个输入信号的频率和相位转换成另一个输出信号的频率和相位,从而实现频率和相位的控制。

2023-02-14 17:19:51 12978

12978 模拟锁相环和数字锁相环的主要区别在于它们的控制方式不同。模拟锁相环是通过模拟电路来控制频率和相位,而数字锁相环是通过数字信号处理技术来控制频率和相位。此外,模拟锁相环的精度较低,而数字锁相环的精度较高。

2023-02-15 13:47:53 6625

6625 虽然并非精确的比较,但这一概念适用的前提是您将输入参考信号视为食物,由锁相环(PLL)/合成器摄入,这会影响PLL/合成器的性能,可在图1所示的输出相位噪声中可见一斑。在本博文中,我将提供一些实际示例来说明什么是良好的输入参考,不良输入参考会造成何种损坏,以及如何分析给定的输入参考。

2023-04-07 10:24:43 1931

1931

当信号源被用作本机振荡器(LO)或高速时钟时,相位噪声性能对满足系统要求起到了重要作用。最初从数据表中推断出该规格时似乎就像一个独立的项目。下面我来讲解一下如何通过读取PLL的相位噪声规格来对您的无线电或高速应用可达到的性能进行初步评估。

2023-04-14 10:32:30 1675

1675

锁相环(PLL),作为Analog基础IP、混合信号IP、数字系统必备IP,广泛存在于各类电子产品中。

2023-06-02 15:25:14 9070

9070

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。PLL锁相环倍频的原理涉及到锁相环,倍频器

2023-09-02 14:59:24 4879

4879 锁相环频率合成器的优缺点 锁相环频率合成器,又称为PLL(Phase Locked Loop),是一种广泛应用的电路,能够将输入信号的频率合成为电路所需要的频率,并且能够实现对信号的相位和频率

2023-09-02 14:59:33 3701

3701 锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

2023-09-02 14:59:37 5118

5118 PLL和DLL都是锁相环,区别在哪里? PLL和DLL都是常用的锁相环(Phase Locked Loop)结构,在电路设计中具有广泛的应用。它们的共同作用是将输入信号和参考信号的相位差控制在一定

2023-09-02 15:06:31 5467

5467 锁相环PLL和锁频环FLL的区别 锁相环(PLL,Phase Locked Loop)和锁频环(FLL,Frequency Locked Loop)是两种常用于信号调节和数据传输的控制回路。虽然它们

2023-09-02 15:06:39 12513

12513 pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 5284

5284 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 2233

2233 什么是锁相环?PLL和DLL都是锁相环区别在哪里? 锁相环(Phase Locked Loop,PLL)是一种基于反馈的控制系统,用于提供稳定的时钟信号。它可以将参考信号的相位与输出信号的相位进行

2023-10-13 17:39:53 3088

3088 作为电力系统中的一种重要控制策略。三相锁相环(PLL)是一种基于锁相环原理的控制系统,它能够将输入的三相电压信号转化成可用于控制其他系统的数字信号。 三相锁相环(PLL)的作用是使得输出电压与输入电压之间保持恒定的相位差,这样可以得到一个相对稳定的输出电压。

2023-10-13 17:39:56 2168

2168 是将某一参考信号的频率和相位锁定到一个输出信号的频率和相位。 然而,在一些情况下,锁相环无法锁定输入信号。特别是在输入信号频率发生了剧烈变化时,锁相环的反应速度跟不上变化,导致无法锁定。此外,输入信号中存在噪声干扰,也会

2023-10-13 17:39:58 3085

3085 锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将输入信号的相位锁定到参考信号的相位。在锁相环中,反馈回路

2023-10-23 10:10:15 4763

4763 了解锁相环(PLL)瞬态响应 如何优化锁相环(PLL)的瞬态响应? 锁相环(PLL)是一种广泛应用于数字通信、计算机网络、无线传输等领域的重要电路。PLL主要用于时钟恢复、频率合成、时钟同步等领域

2023-10-23 10:10:20 3060

3060 锁相环在相位检测中的应用 锁相环(PLL)是一种电子技术中广泛应用的电路,用于调整一个输出信号的相位来精确匹配一个参考信号。锁相环在各种不同的应用领域都有着广泛的应用,例如通信系统、控制系统、测量

2023-10-29 11:35:19 1738

1738 、无线通信、数据转换、模拟信号处理等众多应用领域。然而,频繁的开关PLL的电源可能对其造成不良影响。 PLL芯片是由多个模拟电路和数字电路组成的。在PLL芯片中,锁相环控制器是最重要的组成部分。这个控制器包含一个相位检测器

2023-10-30 10:16:40 1291

1291 应用。本文将重点介绍载波同步电路中的锁相环设计的关键点。 1. 基本原理 PLL 的基本原理是将一个输入信号与一个内部参考频率比较,通过不断调整内部振荡电路的频率和相位,使得输入信号和参考信号在相位上保持一致。通常情况下,PLL 由相位检测器、环路滤波

2023-10-30 10:51:28 1376

1376 如何用锁相环恢复载波同步信号? 锁相环(PLL)是一种电路,可用于恢复和跟踪输入信号的频率和相位。PLL常用于电信、通讯和控制系统中,以恢复和跟踪载波同步信号。本文将介绍锁相环如何恢复载波同步信号

2023-10-30 10:56:38 1535

1535 电子发烧友网站提供《带有分布式锁相环的相控阵系统级LO相位噪声模型.pdf》资料免费下载

2023-11-22 16:12:41 1

1 今天想来聊一下芯片设计中的一个重要macro——PLL,全称Phase lock loop,锁相环。我主要就介绍一下它是什么以及它是如何工作的。

2023-12-06 15:21:13 3126

3126 锁相环到底锁相还是锁频? 锁相环(PLL)是一种常用的控制系统,主要用于同步时钟。它通过将被控信号的相位与稳定的参考信号进行比较,并产生相应的控制信号,使被控信号的相位保持与参考信号同步。这种控制

2024-01-31 15:25:00 4017

4017 锁相环是保证相位一致,还是相位差一致?锁相环的输入输出相位一致吗? 锁相环(PLL)是一种回路控制系统,用于保持输出信号的相位与参考信号的相位之间的恒定关系。简单来说,锁相环的目的是保证相位一致

2024-01-31 15:45:48 2420

2420 锁相环(Phase Locked Loop, PLL)相位噪声是评估锁相环性能的重要指标之一,它描述了输出信号相位的不稳定性。相位噪声的存在会直接影响系统的性能,如降低信号的信噪比、增加误码率、影响雷达系统的目标分辨能力等。以下将详细分析锁相环相位噪声的影响因素,并从多个方面进行归纳和总结。

2024-07-30 15:31:57 4497

4497 电子发烧友网站提供《CDCVF2510A锁相环(PLL)时钟驱动器数据表.pdf》资料免费下载

2024-08-22 09:27:49 0

0 锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,它能够自动调整输出信号的相位,使其与输入信号的相位同步。这种电路在电子工程领域有着广泛的应用,特别是在频率合成、时钟恢复、调制

2024-11-06 10:42:14 3778

3778 在现代电子系统中,频率控制和信号生成是至关重要的。锁相环(PLL)和频率合成器是实现这些功能的两种关键技术。尽管它们在某些应用中可以互换使用,但它们在设计、工作原理和应用领域上存在显著差异。 一

2024-11-06 10:46:53 1812

1812 ,可以实现对输出频率的精确控制,从而满足不同通信标准的要求。 2. 调制与解调 锁相环在调制和解调过程中也扮演着重要角色。在调制过程中,PLL可以用来跟踪载波的相位变化,确保信号的准确传输。在解调过程中,PLL可以用来恢复原始信号的相

2024-11-06 10:49:54 1308

1308 锁相环(PLL)是一种反馈控制系统,用于锁定输入信号的相位和频率。它在现代电子系统中扮演着至关重要的角色,从无线通信到数字信号处理,PLL的应用无处不在。然而,由于其复杂性,PLL也可能出现各种故障

2024-11-06 10:52:09 2964

2964 锁相环(PLL)是一种反馈控制系统,它通过比较输入信号和输出信号的相位差异,调整输出信号以实现相位锁定。在许多应用中,如无线通信、频率合成和时钟同步,PLL的性能直接关系到系统的整体性能。相位噪声

2024-11-06 10:55:53 4449

4449 (Phase-LockedLoop,PLL)技术在可编程晶振中扮演着关键角色,以下是对可编程晶振中锁相环技术的详细讲解:一、锁相环技术的基本原理1、锁相环是一种利用相位同步产生

2025-01-08 17:39:41 1053

1053

锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的反馈控制系统,主要用于频率合成和相位同步。本文将从锁相环的工作原理、基本组成、应用案例以及设计考虑等方面进行详细阐述,以帮助读者全面理解这一重要技术。

2025-02-03 17:48:00 2320

2320

电子发烧友App

电子发烧友App

评论