通过演示简要介绍锁相环(PLL)中可实现的领先相位噪声和杂散性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锁相环

+关注

关注

36文章

633浏览量

90860 -

噪声

+关注

关注

13文章

1154浏览量

48924

发布评论请先 登录

相关推荐

热点推荐

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

该CDCVF2510是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用锁相环 (PLL) 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对

IGBT功率模块动态测试中夹具杂散电感的影响

在IGBT功率模块的动态测试中,夹具的杂散电感(Stray Inductance,Lσ)是影响测试结果准确性的核心因素。杂散电感由测试夹具的layout、材料及连接方式引入,会导致开关

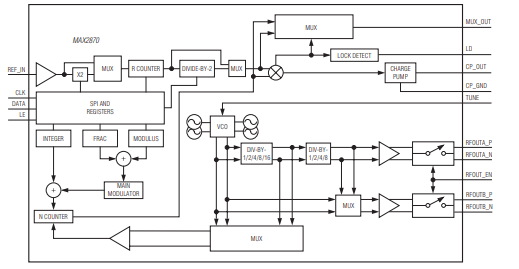

MAX2870 23.5MHz至6000MHz分数/整数N分频合成器/VCO技术手册

MAX2870为超宽频带锁相环(PLL),集成压控振荡器(VCO),能够工作在整数和分数N分频模式。配合外部参考时钟振荡器和环路滤波器,MAX2870可构成高性能频率合成器,产生23.5MHz至6.0GHz频率范围的时钟,并可保持优异的

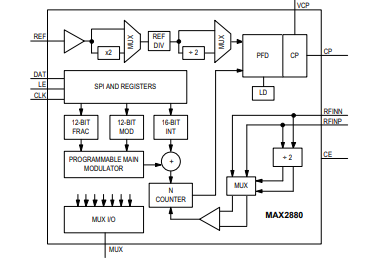

MAX2880 250MHz-12.4GHz、高性能、分数/整数型N分频PLL技术手册

MAX2880为高性能锁相环(PLL),提供整数或分数N分频工作模式。器件配合外部参考时钟振荡器、环路滤波器和VCO,可以构成超低噪声、低杂散

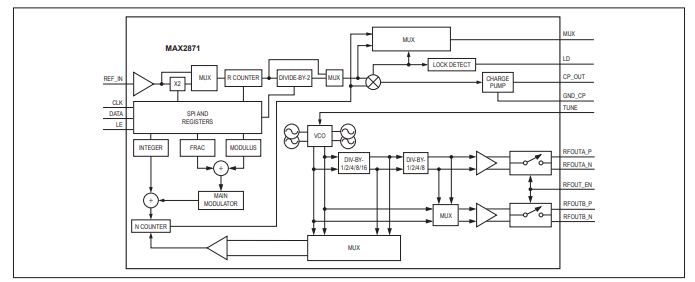

MAX2871 23.5MHz至6000MHz小数/整数N分频频率合成器/VCO技术手册

MAX2871是一款超宽带锁相环(PLL),集成压控振荡器(VCO),可在整数N分频和小数N分频模式下工作。与外部基准振荡器和环路滤波器结合使用时,MAX2871是一款高性能频率合成器,能够合成23.5MHz至6.0GHz的频率,同时保持出色的

普源DSG3000系列如何实现低相位噪声

普源(Rigol)DSG3000系列信号发生器是一款高性能、功能强大的信号发生器,广泛应用于通信、电子测试和科研实验等领域。相位噪声是信号发生器在输出信号时的一项重要指标,它对系统的性能

锁相环是什么意思

锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的反馈控制系统,主要用于频率合成和相位同步。本文将从锁相环的工作原理、基本组成、应用案例以及设计考虑等方面进行详细阐述,以帮助读者全面理解这一重要

AN-1154: 采用恒定负渗漏电流优化ADF4157和ADF4158 PLL的相位噪声和杂散性能

电子发烧友网站提供《AN-1154: 采用恒定负渗漏电流优化ADF4157和ADF4158 PLL的相位噪声和杂散性能.pdf》资料免费下载

发表于 01-13 14:19

•0次下载

AN-1420:利用数字锁相环(DPLL)实现相位增建和无中断切换

电子发烧友网站提供《AN-1420:利用数字锁相环(DPLL)实现相位增建和无中断切换.pdf》资料免费下载

发表于 01-13 14:07

•0次下载

可编程晶振的锁相环原理

锁相环(Phase-LockedLoop,PLL)是一个能够比较输出与输)入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号。而锁相环

ADC10D1500采样数据杂散的原因?

系列FPGA读取ADC的量化数据,使用Matlab对数据做FFT,观察信号频谱,在750MHZ处有明显杂散,该硬件电路板为个人设计电路板,现在找不到引起750M杂散的原因,图片在附件

发表于 01-08 07:22

边带杂散和开关杂散的含义是什么?会对电路造成什么影响?

我在看ADC供电部分的时候,看到边带杂散和开关杂散这两词不知道它的含义。请问下大家它们的含义以及它们将会对电路造成什么影响?

谢谢大家了!!!!!

发表于 12-31 06:32

如何在锁相环中实现相位噪声和杂散性能

如何在锁相环中实现相位噪声和杂散性能

评论