“人如其食”是一个常见说法,建议您仔细选择食物,因为它会直接影响我们的健康和福祉。

虽然并非精确的比较,但这一概念适用的前提是您将输入参考信号视为食物,由锁相环(PLL)/合成器摄入,这会影响PLL/合成器的性能,可在图1所示的输出相位噪声中可见一斑。在本博文中,我将提供一些实际示例来说明什么是良好的输入参考,不良输入参考会造成何种损坏,以及如何分析给定的输入参考。

图1:输入参考噪声也乘以PLL

往后倒推一步,当与压控振荡器(VCO)配对时,PLL成为可锁定到低频信号(来自稳定晶体振荡器的10MHz)的控制环系统,并将其乘以更高的频率(LMX2592可径直乘以9.8GHz)。

示例1

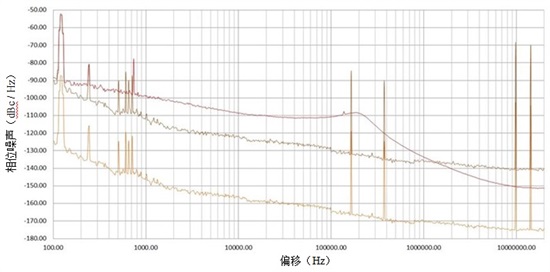

图2所示为单边带相位噪声图。橙色线是100MHz输入参考信号,它使用非常低的相位噪声晶振作为输入参考。本例中的LMX2582合成器将100MHz倍频到5,160.96MHz。如此以来,输入参考噪声也以[20×LOG(5,160.96 / 100)= 34.25dB]的系统成比例增大。棕色线显示放大结果(以数学方式调整)。红色线表示5160.96MHz时LMX2582的输出。

图2:低相位噪声100MHz输入参考和5160.96MHz LMX2582输出

使用类似于图2中的一个输入参考显示合成器的性能,因为输入参考相位噪声足够低。注意,关键区域在环路带宽(〜300kHz偏移)下,因为超过该偏移频率,输入参考噪声也被过滤,并且将以与红线(在该示例中未示出)相同的方式下降。

还要注意输入参考在约120Hz的峰值。这直接影响输出相位噪声。您可能已在此处看到危险。若噪声在较低偏移处在某处耦合到输入参考源中,那么它可能损坏合成器相位噪声。

示例2

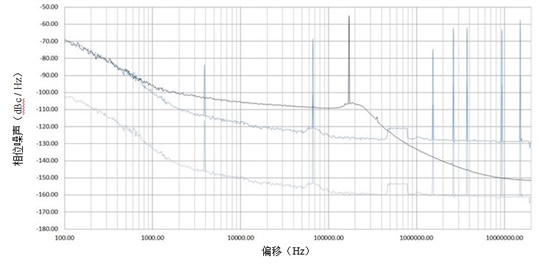

图3考虑了另一个输入参考,这次是一个122.88MHz的晶体振荡器。输出频率仍为5,160.96MHz。此时,输入参考噪声按[20 x LOG(5,160.96 / 122.88)= 32.46dB]的系数进行缩放。查看相位噪声部分2kHz偏移及以下,并将其与图2的输出相位噪声进行比较;您可看到,这个更高的输入参考噪声贡献量直接提高了来自合成器的输出相位噪声。为了从LMX2582实现最佳性能,您还必须为它提供一个足够好的输入参考。并且了解噪声如何缩放和贡献有助于通过其基本相位噪声电平来选择输入参考信号。

图3:一个122.88MHz输入参考和5160.96MHz LMX2582输出

示例3

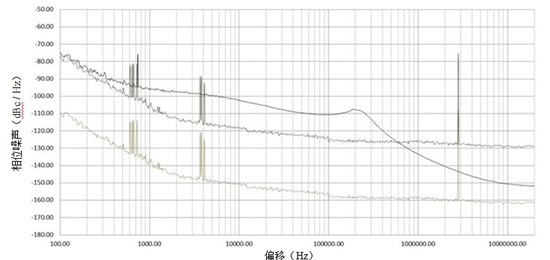

图4探讨了另一种情况。本例还使用了一个122.88MHz的晶体振荡器,但这次是从振动产生相位噪声的影响。当您点击靠近振荡器的手指时,会出现图4中的那些尖峰。这是在某些基于晶体的振荡器中的已知行为。它的损坏方式与不良相位噪声相同,但若您只是将其留在工作台上并进行测量,您可能不会了解它。这表明在选择输入参考时,重要的是不仅要了解设备的基本相位噪声,还要了解其对振动、老化、温度变化、对电源噪声的弹性和许多其它影响的响应。考虑到这一点,可以帮助选择部件并调试整个信号链。

图4:噪声122.88MHz输入参考和5160.96MHz LMX2582输出

要了解这在示例设计中如何工作,请查看我们从降压转换器工作的9.8 GHz RF高性能合成器参考设计。

参考表

作为指导,观察到计算的缩放输入参考噪声的影响是有帮助的。在表1中,您可看到(如预期的那样)若缩放的输入参考相位噪声与PLL相位噪声(表1中的0dB)相同,则您将获得3dB的噪声增量,因为您正将噪声量加倍。同样,若您进一步降低输入参考的相位噪声电平,那么对相位噪声的影响越来越小。

表1:来自缩放输入参考相位噪声的相位噪声

通过这些示例,我希望我已展示一个良好的输入参考对于从合成器获得最佳性能的重要性。不良输入参考不仅是相位噪声电平过高,且是更易受外部影响(振动,老化,温度,电源)的参考。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18707浏览量

261323 -

振荡器

+关注

关注

28文章

4155浏览量

142303 -

pll

+关注

关注

6文章

976浏览量

137568

发布评论请先 登录

一种基于ADF4106的锁相环频率合成器应用实例介绍

锁相环频率合成器:相位噪声问题和宽带循环

不要让不良信号摄入破坏锁相环(PLL)/合成器

快速了解Pasternack推出的高性能USB控制锁相环频率合成器

CN0369 低相位噪声的转换锁相环频率合成器

切勿让不良参考信号破坏锁相环/合成器中的相位噪声

切勿让不良参考信号破坏锁相环/合成器中的相位噪声

评论