时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll

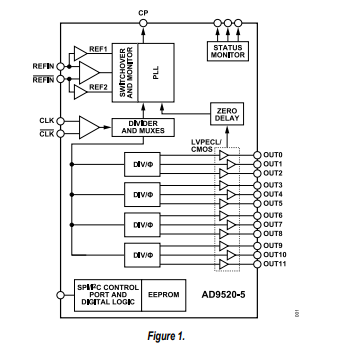

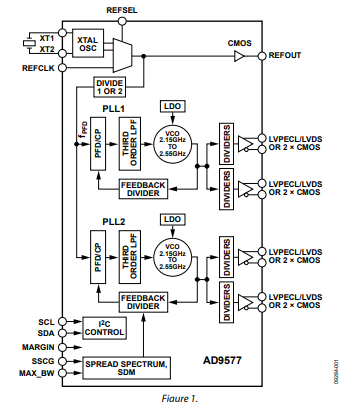

时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环PLL(Phase-Locked Loop)电路。PLL是一种闭环反馈电子电路,其基本原理是通过不断比较输入信号和产生的时钟信号之间的相位差来调节输出信号,使得输出信号与输入信号相位同步。PLL的特点包括高精度、输出纹波小、抗噪声干扰能力强,并且可以实现频率倍频和分频等功能。

PLL电路由三部分组成:相频控振荡器(VCO)、频率控制电路和相位比较器。其中,相频控振荡器是PLL电路的核心部件,它负责产生比输入信号高若干倍的时钟信号;频率控制电路用于控制输出时钟频率,使其与输入信号的频率相匹配;相位比较器则用于监测输入信号和时钟信号之间的相位差,并将控制信号送至频率控制电路。PLL还包括一个使能电路,在输入信号失效时,能够在一定时间内维持输出时钟的频率和相位。

要用硬件配置PLL,需要按照以下步骤进行:

1.确定输入信号的频率范围和精度。这可以通过测量输入信号,并根据需要,选择适当的 PLL 设计参数。

2.确定输出时钟信号的频率范围和精度。这需要根据所连接的电路要求和具体应用场景选择。

3.确定 PLL 的设计参数,包括 VCO 频率、参考信号频率、N 倍频、分频参数等。

4.根据设计参数计算 PLL 的电路元件参数,例如反相放大器增益、电容值、电阻值等。

5.按照电路设计方案,选配电路元件,布局设计,最后进行电路搭建和测试。

总之,PLL电路是时钟发生器的核心部分,它能够实现高精度、低抖动、抗干扰的时钟信号输出,并且可以根据应用需要进行倍频和分频等功能。通过上述步骤,我们可以在硬件上配置PLL电路,从而实现高质量的时钟发生器设计。

-

锁相环

+关注

关注

36文章

633浏览量

90810 -

振荡器

+关注

关注

28文章

4155浏览量

142322 -

pll

+关注

关注

6文章

976浏览量

137584 -

时钟发生器

+关注

关注

1文章

268浏览量

69882

发布评论请先 登录

探索时钟发生器的竞争优势

CDCE421A 时钟发生器芯片技术文档总结

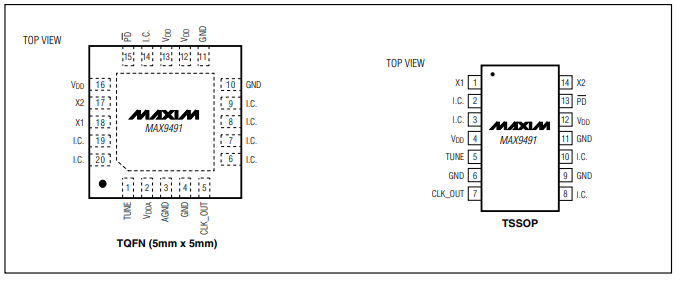

MAX9491工厂可编程、单PLL时钟发生器技术手册

锁相环(PLL)电路设计与应用(全9章)

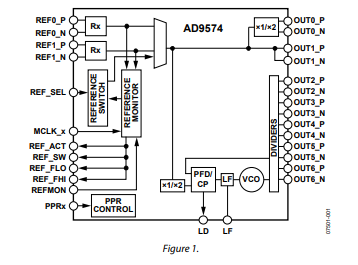

AD9574以太网 千兆以太网时钟发生器技术手册

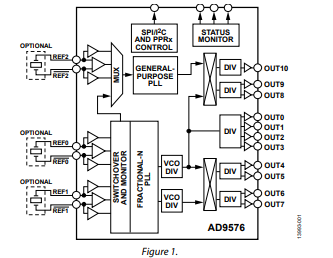

AD9576双通道PLL、异步时钟发生器技术手册

时钟发生器的特点和应用

锁相环是什么意思

可编程晶振的锁相环原理

时钟发生器由哪些部分组成?锁相环pll的特点是什么?

时钟发生器由哪些部分组成?锁相环pll的特点是什么?

评论