锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639180 -

锁相环

+关注

关注

36文章

637浏览量

91299 -

pll

+关注

关注

6文章

990浏览量

138374

发布评论请先 登录

相关推荐

热点推荐

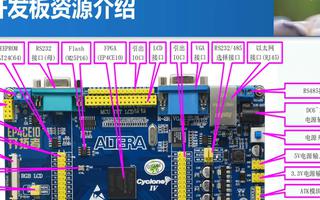

正点开拓者FPGA开发板使用问题

求问各位大佬,刚刚入门正点开拓者FPGA开发板,用板载pcf8591采集信号发生器单一频率正弦波,再用ip核做fft,结果和matlab上fft不一样,请问是怎么回事呢?

发表于 01-04 09:34

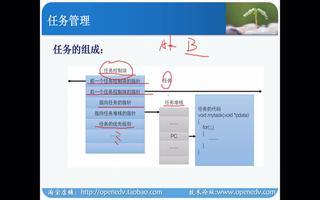

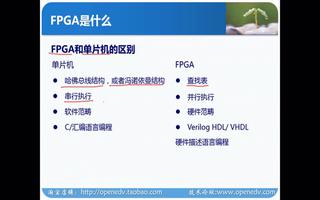

正点原子开拓者FPGA Qsys视频:uCOS II任务管理与时间管理(2)

该课程是正点原子团队编写,详细讲解了quartus中的qsys。也可以从我头像点进去看FPGA verilog相关的视频。

锁相环(PLL)的工作原理及应用

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

pll锁相环倍频的原理

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。

正点原子开拓者FPGA视频:PLL锁相环实验

正点原子开拓者FPGA视频:PLL锁相环实验

评论