锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。

锁相环是一种反馈系统,其中电压控制振荡器和相位比较器 相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率 或相位调制信号的频率。锁相环可用来从固定的低频信号生 成稳定的输出频率信号。首批锁相环由法国工程师de Bellescize 在20世纪30年代初实现。然而,直到20世纪60年代中期,集 成式PLL成为一种成本相对较低的元件之后,锁相环才得到 市场的广泛认可。

01锁相环的基本组成

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

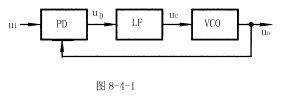

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

02锁相环的工作原理

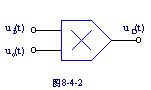

锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

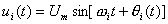

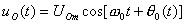

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:

(8-4-1)

(8-4-1)

(8-4-2)

(8-4-2)

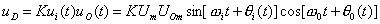

式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为:

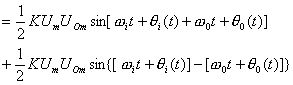

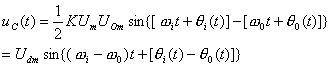

用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为:

(8-4-3)

(8-4-3)

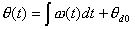

式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θo(t)分别为输入信号和输出信号的瞬时相位,根据相量的关系可得瞬时频率和瞬时相位的关系为:

即 (8-4-4)

(8-4-4)

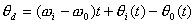

则,瞬时相位差θd为

(8-4-5)

(8-4-5)

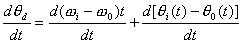

对两边求微分,可得频差的关系式为

(8-4-6)

(8-4-6)

上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。当上式不等于零时,说明锁相环的相位还未锁定,输入信号和输出信号的频率不等,uc(t)随时间而变。

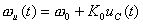

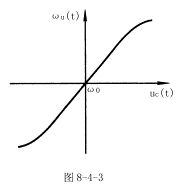

因压控振荡器的压控特性如图8-4-3所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压uc(t)的变化而变化。该特性的表达式为

(8-4-6)

(8-4-6)

上式说明当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。

03锁相环的应用

[1] 锁相环在调制和解调中的应用

(1)调制和解调的概念

为了实现信息的远距离传输,在发信端通常采用调制的方法对信号进行调制,收信端接收到信号后必须进行解调才能恢复原信号。

所谓的调制就是用携带信息的输入信号ui来控制载波信号uc的参数,使载波信号的某一个参数随输入信号的变化而变化。载波信号的参数有幅度、频率和位相,所以,调制有调幅(AM)、调频(FM)和调相(PM)三种。

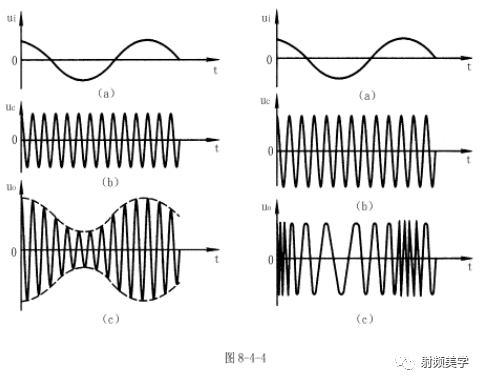

调幅波的特点是频率与载波信号的频率相等,幅度随输入信号幅度的变化而变化;调频波的特点是幅度与载波信号的幅度相等,频率随输入信号幅度的变化而变化;调相波的特点是幅度与载波信号的幅度相等,相位随输入信号幅度的变化而变化。调幅波和调频波的示意图如图8-4-4所示。

上图的(a)是输入信号,又称为调制信号;图(b)是载波信号,图(c)是调幅波和调频波信号。

解调是调制的逆过程,它可将调制波uo还原成原信号ui。

[2] 锁相环在调频和解调电路中的应用

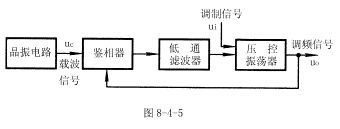

调频波的特点是频率随调制信号幅度的变化而变化。由8-4-6式可知,压控振荡器的振荡频率取决于输入电压的幅度。当载波信号的频率与锁相环的固有振荡频率ω0相等时,压控振荡器输出信号的频率将保持ω0不变。若压控振荡器的输入信号除了有锁相环低通滤波器输出的信号uc外,还有调制信号ui,则压控振荡器输出信号的频率就是以ω0为中心,随调制信号幅度的变化而变化的调频波信号。由此可得调频电路可利用锁相环来组成,由锁相环组成的调频电路组成框图如图8-4-5所示。

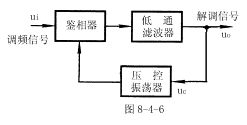

根据锁相环的工作原理和调频波的特点可得解调电路组成框图如图8-4-6所示。

若输入FM信号时,让环路通带足够宽,使信号调制频谱落在带宽之内,这时压控振荡器的频率跟踪输入调制的变化,如图6.1所示。对于锁相环的详细分析可参阅有关锁相技术的书籍。在此仅说明锁相环鉴频原理。可以简单地认为压控振荡器频率与输入信号频率之间的跟踪误差可以忽略。因此任何瞬时,压控振荡器的频率ωv(t)与FM波的瞬时频率ωFM(t)相等。

[3] 锁相环在频率合成电路中的应用

在现代电子技术中,为了得到高精度的振荡频率,通常采用石英晶体振荡器。但石英晶体振荡器的频率不容易改变,利用锁相环、倍频、分频等频率合成技术,可以获得多频率、高稳定的振荡信号输出。

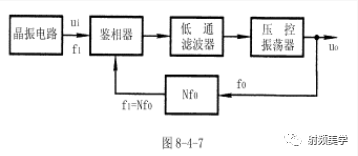

输出信号频率比晶振信号频率大的称为锁相倍频器电路;输出信号频率比晶振信号频率小的称为锁相分频器电路。锁相倍频和锁相分频电路的组成框图如图8-4-7所示。

图中的N大于1时,为分频电路;N小于1时,为倍频电路。

审核编辑 :李倩

-

锁相环

+关注

关注

36文章

637浏览量

91299 -

控制电路

+关注

关注

83文章

1753浏览量

138888

原文标题:一文弄懂锁相环(PLL)的工作原理及应用

文章出处:【微信号:dianyuankaifa,微信公众号:电源研发精英圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高性能低噪声锁相环LTC6948:设计与应用全解析

Altera公司锁相环IP核介绍

探索CDC516:高性能3.3V锁相环时钟驱动器

CDC2516:高性能锁相环时钟驱动器的深度解析

CDC509:高性能3.3V锁相环时钟驱动器

CDCVF25081:高性能锁相环时钟驱动器深度解析

TLC2932A高性能锁相环芯片详解:设计与应用指南

探索TLC2933A高性能锁相环:特性、应用与设计要点

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

CDCVF2509 3.3V锁相环时钟驱动器技术文档总结

CDCVF2510A 3.3V锁相环时钟驱动器技术文档总结

TLC2933A 高性能锁相环 (PLL) 芯片技术文档摘要

高压放大器在锁相环稳定重复频率研究中的应用

Analog Devices Inc. ADF4382x小数N分频锁相环 (PLL)数据手册

锁相环(PLL)的工作原理及应用

锁相环(PLL)的工作原理及应用

评论