16日,三星电子宣布在基于EUV的高级节点方面取得了重大进展,包括7nm批量生产和6nm客户流片,以及成功完成5nm FinFET工艺的开发。 三星电子宣布其5纳米(nm)FinFET工艺技术的开发

2019-04-18 15:48:47 6010

6010 作为业界少数几家加入FinFET俱乐部的公司,中芯国际已经开始使用其14 nm FinFET制造技术批量生产芯片。该公司设法开发了依赖于此类晶体管的制造工艺。有点遗憾的是,中芯国际的FinFET

2019-11-19 10:40:26 6858

6858 全球电子设计创新企业Cadence设计系统公司日前宣布其与TSMC在3D IC设计基础架构开发方面的合作。

2012-06-11 09:47:43 1071

1071 新思科技公司(Synopsys)在过去五年多与行业领导者合作共同开发了对FinFET技术的支持,通过提供经生产验证的设计工具与IP来推进对FinFET技术的采用。

2013-02-19 10:42:54 823

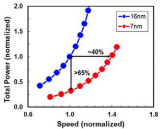

823 16nm/14nm FinFET技术将是一个Niche技术,或者成为IC设计的主流?历史证明,每当创新出现,人们就会勾勒如何加以利用以实现新的、而且往往是意想不到的价值。FinFET技术将开启电脑、通信和所有类型消费电子产品的大跃进时代。

2013-03-28 09:26:47 2161

2161 Cadence系统芯片开发工具已经通过台积电(TSMC) 16纳米 FinFET制程的设计参考手册第0.1版与 SPICE 模型工具认证,客户现在可以享用Cadence益华电脑流程为先进制程所提供的速度、功耗与面积优势。

2013-06-06 09:26:45 1236

1236 在Synopsys 的协助下,台湾联电(UMC)首款基于14nm制程及FinFET晶体管技术的测试用芯片日前完成了流片。联电公司早前曾宣布明年下半年有意启动14nm 制程FinFET产品的制造,而这

2013-06-28 09:57:58 1023

1023 昨日台积电官方宣布,16nm FinFET Plus(简称16FF+)工艺已经开始风险性试产。16FF+是标准的16nm FinFET的增强版本,同样有立体晶体管技术在内,号称可比20nm SoC平面工艺性能提升最多40%,或者同频功耗降低最多50%。

2014-11-14 09:31:58 2127

2127 All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布其与台积公司( TSMC)已经就7nm工艺和3D IC技术开展合作,共同打造其下一代All Programmable FPGA、MPSoC和3D IC。

2015-05-29 09:09:49 1802

1802 TSMC在FinFET工艺量产上落后于Intel、三星,不过他们在10nm及之后的工艺上很自信,2020年就会量产5nm工艺,还会用上EUV光刻工艺。

2016-07-18 10:47:09 989

989 2016年各大晶圆厂的主流工艺都是14/16nm FinFET工艺,Intel、TSMC及三星明年还要推10nm工艺,由于Intel也要进军10nm代工了,这三家免不了一场大战。但是另一家代工厂

2016-08-17 16:59:40 2693

2693 今日,三星电子正式宣布已经开始大规模生产基于10nm FinFET技术的SoC,这是业界内首家提供10nm工艺代工厂商。新工艺下的SoC性能可以提供27%,功耗将降低40%。

2016-10-17 14:07:01 873

873 全球第一大芯片自动化设计解决方案提供商及全球第一大芯片接口IP供应商、信息安全和软件质量的全球领导者Synopsys(NASDAQ:SNPS)宣布,Synopsys IC Validator工具已获得GLOBALFOUNDRIES(GF)认证,将用于GF 14LPP工艺技术的物理验证Signoff。

2018-05-23 17:51:22 6817

6817 Cadence 112G-ELR SerDes IP 系列产品的新成员。在后摩尔时代的趋势下,FinFET 晶体管的体积在 TSMC 3nm 工艺下进一步缩小,进一步采用系统级封装设计(SiP)。通过

2023-05-19 16:25:12 784

784

、90nm、65nm、45nm、32nm、22nm、14nm、10nm...有人说5nm是半导体工艺的极限尺寸,也有人说1nm是半导体工艺的极限尺寸;iPhone6s的 A9处理器更出现了三星14nm

2017-01-06 14:46:20

IC认证发证机构(一) IC:由获得IC场地注册代码的实验室发证(二) IC ID: 由FCB / TCB机构审核发证

2016-12-23 10:35:41

IC认证介绍?IC 是加拿大工业部Industry Canada的简称,作为***机构,负责电子电器产品进入加拿大市场的认证事务。其负责产品大致为广播电视设备、信息技术设备、无线电设备、电信设备、工科医设备等。IC认证主要有两种方式:IC 自我宣告; IC ID 认证证书

2016-12-23 10:29:49

IC认证时间周期及有效期(一)IC:1-2周;(二)IC ID:3-4周. 有效期标准过期更新

2016-12-12 09:30:45

IC设计:Synopsys2018 版本 EDA 工具免费分享1. 下载的文件列表包含一下文件;加群Q:139869702ReadMe:文件就是现在你正在阅读的文件,主要是详细的说明软件的使用和包含

2020-11-30 18:56:05

Synopsys安装包及破解LicenseVerdi,DC,VCS,DFT Compiler,ICC,ICC2,PrimeTime,Library Compiler,S FPGA,PrimePower,Formality,Hspice,SpyGlass....

2020-02-07 23:57:49

各位大神,小弟现在在做运用Synopsys 工具的仿真。现在希望通过仿真模拟获得网表中所有node的值(包括wire和output)。目前使用的软件有design compiler, TetraMax 和VCS。 请问有没有办法可以实现?谢谢。

2017-09-07 02:48:47

想问一下,TSMC350nm的工艺库是不是不太适合做LC-VCO啊,库里就一个电容能选的,也没有电感可以选。(因为课程提供的工艺库就只有这个350nm的,想做LC-VCO感觉又不太适合,好像只能做ring-VCO了)请问350nm有RF工艺嘛,或者您有什么其他的工艺推荐?

2021-06-24 08:06:46

TSMC 65nm HSPICE 蒙特卡罗分析,仿真出现错误,有人做过吗 .prot .lib 'D:\crn65lp_v1d5.l' mc.lib 'D:\crn65lp_v1d5.l

2013-06-21 16:10:47

COMP ck=235PACKAGE EFA_Synopsys_2 snpslmd 2009.5 10E0A051DB52390448F9 COMP ck=221PACKAGE

2009-01-21 13:10:00

工艺认证的 FinFET 和可识别多重图形的设计Signoff 时序、寄生参数提取和功耗分析消除设计迭代从综合到后期布线的高级区域恢复算法,以获得最大利用率

2020-11-14 07:58:53

。该平台通过使用Design Compiler® Graphical 和Design Compiler® NXT综合、IC Compiler™ II 布局布线和Fusion Compiler

2020-10-22 09:40:08

areas.PREFERRED:MS inEngineering or Science.Knowledge in20nm or FinFET technology, circuit design

2014-06-18 10:43:09

转自http://www.eet-china.com/ART_8800697889_480201_NT_08124b24.HTM台积电借16nm FinFET Plus及InFO WLP 通吃英特尔

2014-05-07 15:30:16

增加SRAM单元数量。表1:鳍片的高度、宽度与间距差异:i8 vs. S8另一方面是材料的选择,从图4c、4d的EDS图像显示,两种10nm的FinFET成分组成是大同小异的,而且也没有出现跟以往

2018-06-14 14:25:19

改进,使我们的高端StratixIIIFPGA能够用于高性能计算领域,而低成本CycloneIIIFPGA用于软件无线电,MaxIIZCPLD则适合便携式应用。 在生产工艺方面,Altera在很大程度

2019-07-16 08:28:35

芯片除了核心数超过高通之外,在CPU性能、GPU性能、拍照、网络等方面皆不如骁龙旗舰,而且制程工艺往往落后一代。因此,Helio X30原本规划使用TSMC的16nm FinFET工艺,但同期的竞品

2017-02-16 11:58:05

求TSMC90nm的工艺库,请问可以分享一下吗?

2021-06-22 06:21:52

求一份tsmc 7nm standard cell library求一份28nm或者40nm 的数字库

2021-06-25 06:39:25

求助大神们,需要TSMC90nm RF库用于学习

2021-06-22 06:28:17

反对。TSMC以前曾有些模棱两可,推进了16 nm finFET半节点计划。而影响最大的是,NVIDIA CEO Jen-Hsun Huang公开质疑整个20 nm节点的经济可行性,他认为,每个晶体管

2014-09-01 17:26:49

近日,SIA发了个耸人听闻的新闻,说intel放弃了10nm工艺的研发,当然这肯定是假消息就是了,今天intel也出面辟谣。不过相信很多人也会觉得奇怪,那边TSMC 7...

2021-07-26 08:10:47

之前只用过tsmc 65nm的,在设置电感时候是有indcutor finder的工具的,28nm下没有了吗?只能自己扫描参数一个一个试?28nm下是没有MIM电容了吗?相关的模拟射频器件(比如

2021-06-24 06:18:43

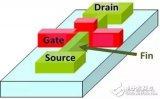

大家都在谈论FinFET——可以说,这是MOSFET自1960年商用化以来晶体管最大的变革。几乎每个人——除了仍然热心于全耗尽绝缘体硅薄膜(FDSOI)的人,都认为20 nm节点以后,FinFET将成为SoC的未来。但是对于要使用这些SoC的系统开发人员而言,其未来会怎样呢?

2019-09-27 06:59:21

, part of the Synopsys suiteof synthesis tools. FPGA Compiler II / FPGA Express reads an RTLVerilog HDL model of a discrete electro

2009-07-23 09:59:06 21

21 , part of the Synopsys suiteof synthesis tools. FPGA Compiler II / FPGA Express reads an RTLVerilog HDL model of a discrete electro

2009-07-23 10:01:29 79

79 设计编译器(Design Compiler)和设计分析器(Design Analyzer) Design Compiler(DC) 是Synopsys逻辑综合工具的命令行接口

2009-11-19 13:32:16 57

57 下一代的实体设计系统IC Compiler,为Synopsys Galaxy Design Platform 2005的核心,其设计概念就在解决这些浮现的挑战,提供从RTL到芯片的一贯解决方案

2011-04-19 11:14:51 970

970 虽然TSMC对于旗下28nm工艺依然保持着较为保守的态度,但是根据近期非官方的报道,由于来自官户的需求不断提升,TSMC将会对28nm晶元进行提价。

2011-09-16 09:30:03 955

955

敦泰科技与TSMC近日共同宣布,由敦泰科技设计并委托TSMC生产制造的触控芯片(Touch-Panel Controller IC)已突破总出货一千万颗的里程碑

2011-09-24 01:24:04 1397

1397 珠海全志科技与TSMC今(26)日共同宣布,成功推出采用TSMC55纳米工艺生产的A10系列系统整合芯片(SoC)平台,藉由搭配珠海全志科技全新的Android 4.0.3 软件开发工具包(Software Devel

2012-03-27 08:52:40 2408

2408 TSMC28nm的产能,目前仍旧无法满足Qualcomm、AMD以及NVIDIA三家客户,似乎已经是不争的实施。

2012-05-15 08:37:20 652

652 Mentor Graphics公司日前宣布Calibre LFD(光刻友好设计)光刻检查工具已获得TSMC的20nm IC制造工艺认证。 Calibre LFD可对热点进行识别,还可对设计工艺空间是否充足进行检查。光学临近校正法

2012-09-29 10:30:46 1761

1761 电子发烧友网核心提示 :Mentor Graphics公司日前宣布Calibre LFD(光刻友好设计)光刻检查工具已获得TSMC的20nm IC制造工艺认证。 Calibre LFD可对热点进行识别,还可对设计工艺空间是否充足进

2012-10-08 16:00:14 915

915 FinFET制程的设计规则手册(DRM)第0.5版的认证,同时从即刻起可以提供一套TSMC 16-nm可互通制程设计套件(iPDK)。凭借其对iPDK标准强大的支持,Synopsys的Laker定制解决方案为用户提供了从180-nm到16-nm的多种TSMC工艺技术的全面对接。

2013-09-23 14:45:30 1050

1050 2013年12月3号,北京——Altera公司(Nasdaq: ALTR)今天发布了Arria 10版Quartus II软件,这是业界第一款支持20 nm FPGA和SoC的开发工具。基于TSMC

2013-12-03 10:48:47 1607

1607 美国加利福尼亚州山景城,2015年3月-- 新思科技公司(Synopsys, Inc.,纳斯达克股票市场代码:SNPS)日前宣布:其 Galaxy™ Design Platform 设计平台支撑

2015-04-01 16:42:27 1007

1007 俄勒冈州威尔逊维尔,2015 年 4 月 6 日—Mentor Graphics公司(纳斯达克代码:MENT )今天宣布,TSMC和Mentor Graphics已经达到在10nm EDA认证合作的第一个里程碑

2015-04-20 14:18:06 1658

1658 Mentor Graphics公司(纳斯达克代码:MENT)今天宣布,Calibre® nmPlatform 已通过TSMC 10nm FinFET V0.9 工艺认证。此外,Mentor

2015-09-21 15:37:10 1300

1300 2016年3月22日,中国上海——楷登电子(美国 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10纳米 FinFET工艺的数字、定制/模拟和签核工具通过台积电(TSMC)V1.0设计参考手册(DRM)及SPICE认证。

2016-03-22 13:54:54 1026

1026 Mentor Graphics公司(纳斯达克代码:MENT)今天宣布,借由完成 TSMC 10 纳米 FinFET V1.0 认证,进一步增强和优化Calibre® 平台和 Analog

2016-03-24 11:13:19 816

816 Custom Compiler™将定制设计任务时间由数天缩短至数小时,消弭了FinFET的生产力差距。

2016-04-13 15:23:31 2571

2571 2016年半导体的主流工艺是14/16nm FinFET工艺,主要有Intel、TSMC及三星/GlobalFoundries(格罗方德)三大阵营,下一个节点是10nm,三方都会在明年量产,不过

2016-05-30 11:53:53 858

858 导语:联发科和华为均已确定下一代处理器将采用10nm工艺制程,高通也紧追其后递交10nm芯片样品给客户,据悉,高通10nm订单均交给三星代工生产。

2016-07-28 19:00:27 680

680 2015年以来,英特尔(Intel)、三星、台积电(TSMC)纷纷发力16/14nm FinFET工艺,而当下芯片厂商正争相蓄力2017款10nm半导体制造工艺。随着高通CEO爆料,高通2017

2016-08-19 14:34:10 809

809 有分析师透露消息指苹果的A11处理器基本确定会采用台积电的10nm工艺生产,这意味着台积电的7nm工艺不会早于明年三季度,必然导致10nm工艺产能非常紧张。这对于寄望多款产品采用台积电的10nm工艺来增强芯片竞争力的联发科来说显然是一个非常不好的消息。

2016-12-19 11:10:02 498

498 有分析师透露消息指苹果的A11处理器基本确定会采用台积电的10nm工艺生产,这意味着台积电的7nm工艺不会早于明年三季度,必然导致10nm工艺产能非常紧张。这对于寄望多款产品采用台积电的10nm工艺来增强芯片竞争力的联发科来说显然是一个非常不好的消息。

2016-12-20 02:31:11 600

600 消息称,预计10纳米工艺的低良率将导致明年的A10X芯片的iPad平板电脑可能推迟生产。台积电的10nm芯片主要是由苹果,海思,联发科操刀,虽然有部分是代工。买方要求2017年第一季度就批量生产,但台积电10纳米芯片工艺技术的良率并不是代工生产公司希望看到的,消息人士说

2016-12-24 09:39:46 640

640 TSMC、三星不仅要争抢10nm工艺,再下一代的7nm工艺更为重要,因为10nm节点被认为是低功耗型过渡工艺,7nm才是真正的高性能工艺,意义更重大。现在ARM宣布已将Artisan物理IP内核授权给赛灵思(Xilinx)公司,制造工艺则是TSMC公司的7nm。

2017-01-13 12:57:11 1581

1581

企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布其与台积公司( TSMC)已经就7nm工艺和3D IC技术开展合作,共同打造其下一代All Programmable

2017-02-09 03:48:04 198

198 2015年,基于FinFET 工艺的IC产品将大量面市,除了英特尔的X86处理器和一些ASIC处理器外,FPGA也正式步入FinFET 3D晶体管时代,2月23日,羊年大年初五,赛灵思率先发布基于16nm FinFET 3D晶体管的FPGA新品,再次创下业界第一,开启了FinFET FPGA的新时代。

2019-10-06 11:57:00 3095

3095 Technology (12FFC) 和最新版本 7nm FinFET Plus 工艺的认证。Nitro-SoCTM 布局和布线系统也通过了认证,可以支持 TSMC 的 12FFC 工艺技术。

2017-10-11 11:13:42 2372

2372 功耗低,面积小的优点,台湾积体电路制造股份有限公司(TSMC)等主要半导体代工已经开始计划推出自己的FinFET晶体管[4],为未来的移动处理器等提供更快,更省电的处理器。从2012年起,FinFET已经开始向20纳米节点和14纳米节点推进。

2018-07-18 13:49:00 119524

119524

台积电南京工厂将会在明年5月提前量产30mm晶圆,据悉,台积电会引进16nm FinFET制造工艺,仅次于10nm FinFET,并在南京设立一个设计服务中心来吸引客户订单。

2017-12-10 09:30:46 910

910 TSMC最新版5nm FinFET 和 7nm FinFET Plus 工艺的认证。Mentor 同时宣布,已更新了 Calibre nmPlatform 工具,可支持TSMC的晶圆堆叠封装 (WoW)技术

2018-05-17 15:19:00 3391

3391 7-nm FinFET Plus工艺的极紫外光刻技术,IC Compiler II 进行了专门的优化,进一步节省芯片面积。 采用TSMC的Wafer-on-Wafer(WoW)技术,平台内全面支持

2018-05-17 06:59:00 4461

4461 Synopsys Synopsys近日宣布, Synopsys 设计平台获得TSMC最新版且最先进的5nm工艺技术认证,可用于客户先期设计。通过与TSMC的早期密切协作,IC CompilerII

2018-06-01 09:35:00 3784

3784 Synopsys宣布,Synopsys Design Platform已通过全球领先半导体技术企业三星电子的工艺认证,支持三星代工部门的8nm LPP(低功耗+)工艺。Synopsys Design

2018-06-06 11:00:00 1441

1441 采用新思科技Sentaurus、Process Explorer、StarRC、SiliconSmart、PrimeTime和IC Compiler II,DTCO方法学降低了先进半导体工艺开发的成本,并加快了上市速度。

2018-09-21 11:53:52 7913

7913 基于7nm工艺技术的控制器和PHY IP具有丰富的产品组合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解决方案支持TSMC 7nm工艺技术所需的先进汽车设计规则,满足可靠性和15年汽车运行要求。

2018-10-18 14:57:21 6541

6541 IC Compiler II和Design Compiler Graphical提供了统一流程,实现最低功耗、最佳性能和最优面积。

StarRC、PrimeTime和PrimeTime PX支持全流程设计实现并提供时序和功耗分析的signoff支持。

2018-10-23 14:29:14 5460

5460 新思科技(Synopsys)推出支持TSMC 7nm FinFET工艺技术的汽车级DesignWare Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2

2018-11-13 16:20:23 1517

1517 关键词:5nm , Compiler , PrimeTime 新思科技(Synopsys)宣布其数字和定制设计平台通过了TSMC最先进的5nm EUV工艺技术认证。该认证是多年广泛合作的结果,旨在

2018-10-27 22:16:01 255

255 关键词: Design Compiler , Synthesis Design Compiler NXT将运行时间缩短2倍,QoR提高5%,并支持5nm及更先进的工艺节点 新思科技(Synopsys

2018-11-14 17:50:01 220

220 新思科技近日宣布采用先进Fusion技术的创新型IC Compiler™ II布局布线解决方案已在瞻博网络(Juniper Networks)部署,为瞻博网络实现了更好的功耗和面积结果。此外,在IC Compiler II布局布线解决方案内执行时,工程变更指令(ECO)周转时间可缩短40%以上。

2019-06-14 08:42:21 3057

3057 最新版IC Compiler II通过新一代分布式并行、智能场景管理、高效基础设施扩展和固有核心引擎算法,提供快2倍的吞吐量

2019-08-13 16:23:53 2424

2424 本文档的主要内容详细介绍的是ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明包括了:1、逻辑综合基本概念 a) Synopsys综合工具及相关工具 b) 逻辑综合

2019-10-23 08:00:00 5

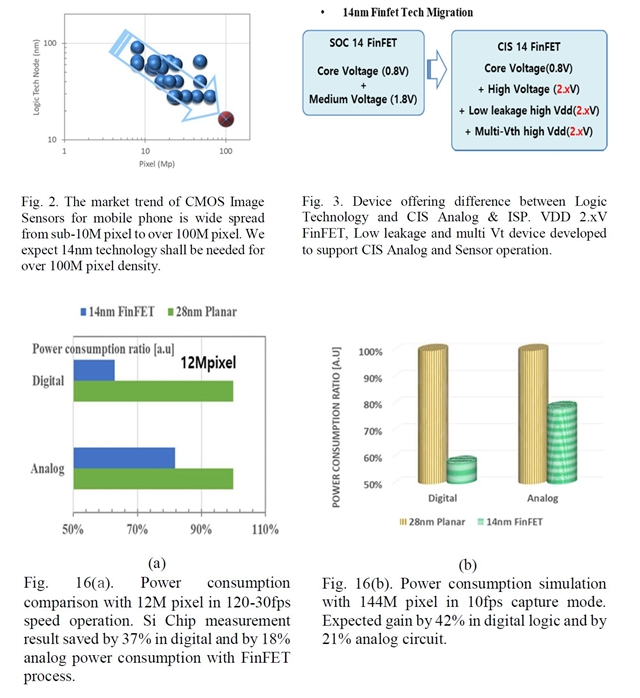

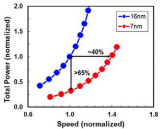

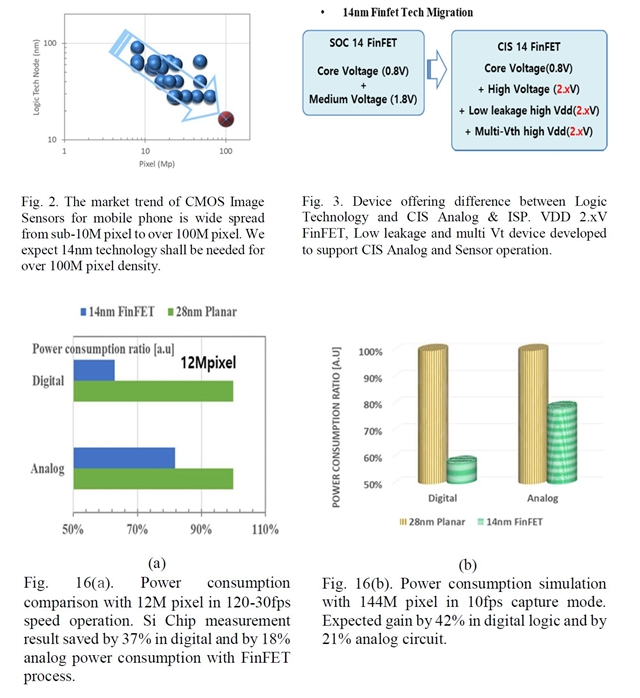

5 据介绍,14nm FinFET工艺使得界面态密度(Nit)提升40%以上,闪烁噪声提高64%,数字逻辑功能芯片功耗降低34%。凭借14nm FinFET先进工艺优势,144MP功耗有望降低42%。

2020-01-25 15:40:00 1317

1317

(功耗、性能和面积)优势,同时加快产品上市时间 ● 新思科技进一步强化关键产品,以支持TSMC N3制造的进阶要求 新思科技(Synopsys)近日宣布,其数字和定制设计平台已获得TSMC 3nm制造技术验证。此次验证基于TSMC的最新设计参考手册(DRM)和工艺设计工具包(

2020-10-14 10:47:57 1764

1764 重点 ● TSMC认证基于新思科技3DIC Compiler统一平台的CoWoS和InFO设计流程 ● 3DIC Compiler可提高先进封装设计生产率 ● 集成Ansys芯片封装协同分析解决方案

2020-10-14 11:11:21 2099

2099 重点 ● 双方在技术赋能方面的紧密合作使GLOBALFOUNDRIES 12LP、12LP+ (12nm FinFET) 以及22FDX (22nm FD-SOI) 平台释放最佳PPA潜能

2020-10-23 16:17:09 2050

2050 的,目的在于加速为GAA 构的生产流程提供高度优化的参考方法。而因为三星的3 nm制程采用不同于台积电或英特尔所采用的 FinFET 的架构,而是采用 GAA 的结构。在此情况下,三星需要

2021-07-01 15:27:44 4315

4315 最小 Lg 是沟道栅极控制的函数,例如从具有不受约束的沟道厚度的单栅极平面器件转移到具有 3 个栅极围绕薄沟道的 FinFET,从而实现更短的 Lg。FinFET 的栅极控制在鳍底部最弱,优化至关重要。

2023-01-04 15:54:51 1488

1488 IP_数据表(I-10):USB2.0 Transceiver for TSMC 28nm HPC+

2023-03-16 19:34:54 0

0 推出一项将加速计算引入计算光刻技术领域的突破性成果。 在当前生产工艺接近物理极限的情况下,这项突破使 ASML、TSMC 和 Synopsys 等半导体行业领导者能够加快新一代芯片的设计和制造。 全球

2023-03-23 06:45:02 310

310 IP_数据表(I-10):USB2.0 Transceiver for TSMC 28nm HPC+

2023-07-06 20:21:03 0

0 Compiler是统一的多裸晶芯片封装探索、协同设计和分析的平台,已经获得三星多裸晶芯集成工艺流程的认证。 全面和可扩展的新思科技多裸晶芯片系统能够实现从早期设计探索到芯片生命周期管理全流程的快速异构集成。 新思科技(Synopsys)近日宣布,与三星晶圆厂(以下简称为“三星”)深化合作,助

2023-09-14 09:38:28 839

839 台积电推出了世界上第一个3nm智能手机芯片apple a17 pro,该芯片也用于新款iphone 15 pro。据悉,tsmc到2023年为止,将只批量生产苹果的3nm工艺。

2023-09-25 14:25:28 616

616 NVIDIA 于今日宣布,为加快下一代先进半导体芯片的制造速度并克服物理限制,TSMC 和 Synopsys 将在生产中使用 NVIDIA 计算光刻平台。

2024-03-20 09:52:00 100

100

电子发烧友App

电子发烧友App

评论