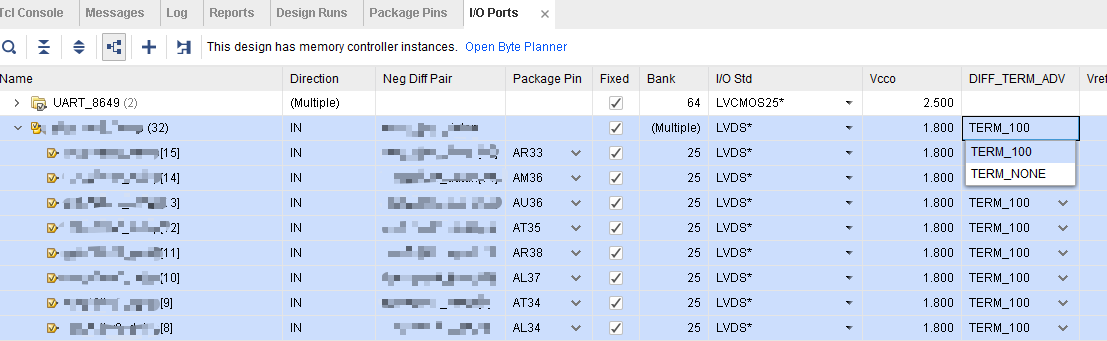

I/O约束 I/O约束是必须要用的约束,又包括管脚约束和延迟约束。 管脚约束 管脚约束就是指管脚分配,我们要指定管脚的PACKAGE_PIN和IOSTANDARD两个属性的值,前者指定了管脚的位置

2020-10-30 16:08:13 17476

17476

对话框的约束部分下,选择默认约束设置作为活动约束设置;包含在Xilinx设计约束(XDC)文件中捕获的设计约束的一组文件,可以将其应用于设计中。两种类型的设计约束是: 1) 物理约束:这些约束定义引脚

2020-11-23 14:16:36 6670

6670

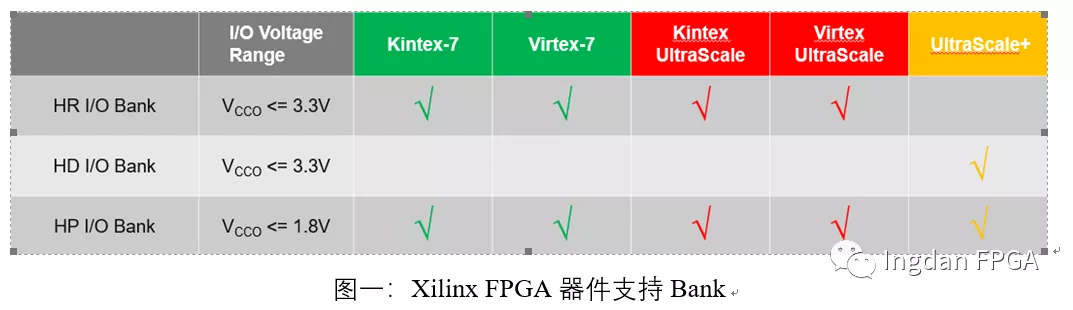

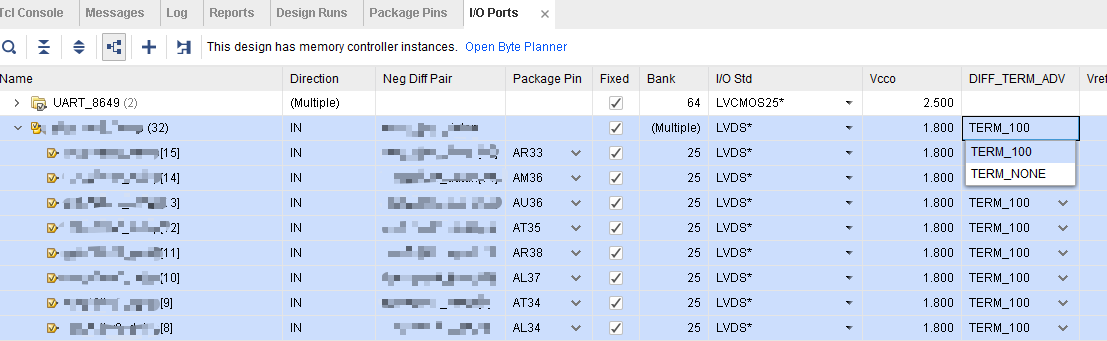

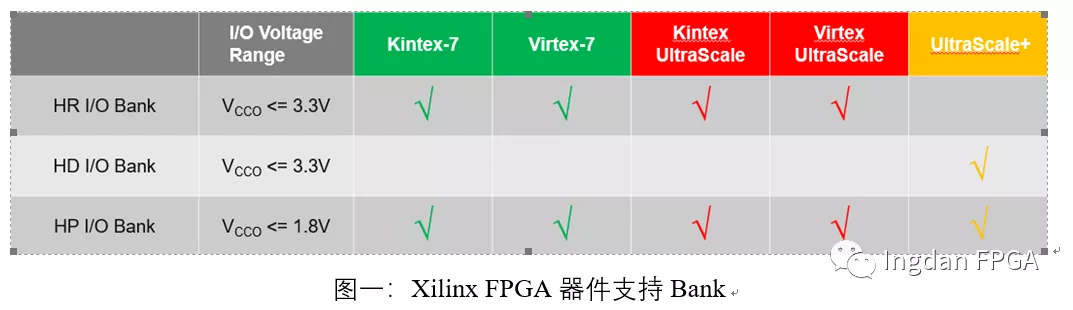

FPGA是电子器件中的万能芯片,Xilinx FPGA处于行业龙头地位更是非常灵活。FPGA管脚兼容性强,能跟绝大部分电子元器件直接对接。Xilinx SelectIO支持电平标准多,除MIPI

2022-08-02 09:31:28 7896

7896

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束和时序例外约束才能实现PCB板级的时序收敛。因此,FPGA时序约束中IO口时序约束也是一个重点。只有约束正确才能在高速情况下保证FPGA和外部器件通信正确。

2022-09-27 09:56:09 2392

2392 在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

2023-06-06 18:27:13 12757

12757

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

2023-06-12 17:29:21 4234

4234 前面几篇FPGA时序约束进阶篇,介绍了常用主时钟约束、衍生时钟约束、时钟分组约束的设置,接下来介绍一下常用的另外两个时序约束语法“伪路径”和“多周期路径”。

2023-06-12 17:33:53 3055

3055 前面讲解了时序约束的理论知识FPGA时序约束理论篇,本章讲解时序约束实际使用。

2023-08-14 18:22:14 3030

3030

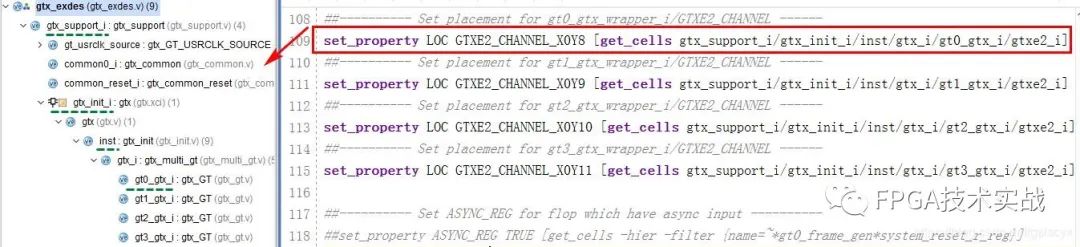

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 5117

5117

I/O约束(I/O Constraints)包括I/O标准(I/OStandard)约束和I/O位置(I/O location)约束。

2023-11-18 16:42:28 2442

2442

IS_ROUTE_FIXED命令用于指定网络的所有布线进行固定约束。进入Implemented页面后,Netlist窗口如图1所示,其中Nets文件展开后可以看到工程中所有的布线网络。

2023-12-16 14:04:31 2165

2165

在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果

2024-01-02 14:13:53 2363

2363

FPGA 管脚分配需要考虑的因素FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 10:27:54

今天给大侠带来 Xilinx ISE14.7 LVDS应用,话不多说,上货。

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用。Xilinx FPGA中,主要通过原语实现差分信

2024-06-13 16:28:52

FPGA管脚分配需要考虑的因素 FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 11:34:24

找到问题根源,后来在做另一个项目里,需要写MAC的时序约束,发现Xilinx提供的MAC硬对‘RX_CLK’的时序约束要求很高,建立时间只有2.5ns,保持时间0.5ns,无论怎么反复修改这个约束值都无法

2019-07-09 08:00:00

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

钟偏差。

Tlogic与我们写的HDL代码有直接关系,Trouting是FPGA开发软件综合布线根据FPGA内部资源情况进行布线产生的延时。

四、总结

本文介绍了FPGA时序约束的基础理论

2023-11-15 17:41:10

不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 2. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时

2017-12-27 09:15:17

你好: 现在我使用xilinx FPGA进行设计。遇到问题。我不知道FPGA设计是否符合时序要求。我在设计中添加了“时钟”时序约束。我不知道如何添加其他约束。一句话,我不知道哪条路径应该被禁止。我

2019-03-18 13:37:27

FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-09-21 07:45:57

本本将从常见的XILINX FPGA和Altera 两家FPGA的电源供电作如下介绍:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

本帖最后由 china198 于 2013-8-30 12:28 编辑

XILINX的作品---时序约束,写的非常棒

2013-08-30 12:26:47

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-07-08 08:00:00

各位大神,请问Xilinx FPGA中的DCI是如何使用的?我知道是把每个Bank的VRP、VRN管脚分别下拉、上拉,除此之外,在HDL代码和约束中应该如何写呢?查了半天资料没有查到,所以来论坛问问。@LQVSHQ

2017-08-20 20:51:57

本帖最后由 eehome 于 2013-1-5 09:52 编辑

不可多得的Xilinx FPGA中文培训材料教程,涉及到virtel的基本架构、赛灵思设计流程、如何阅读报告、时序约束等经典

2012-03-02 09:51:53

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-04-12 17:39:04

今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为

2024-05-06 15:51:23

在给 FPGA 做逻辑综合和布局布线时,需要在工具中设定时序的约束。通常,在 FPGA 中都包含有4 种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入 到输出的纯组合逻辑

2012-03-05 15:02:22

Xilinx_fpga_设计:全局时序约束及试验总结

2012-08-05 21:17:05

我用xilinx spartan-6fpga 它硬核的管脚是固定的还是可配置的我在xilinx提供的文档里找不到关于硬核管脚的分配求指导

2012-08-11 09:28:44

网线的驱动源为同步点;附加在同步元件的输出管脚上,则同步元件中驱动该管脚的源为同步点;附加在同步元件上,则输出管脚为同步点;附加在同步元件的输入管脚上,则该引脚被定义成同步点。(4)局部约束1多周期约束

2017-03-09 14:43:24

xilinx_fpga结构及工作原理介绍

2012-08-02 22:59:43

引言:本文我们介绍Xilinx 7系列FPGA收发器硬件设计主要注意的一些问题,指导硬件设计人员进行原理图及PCB设计。本文介绍以下内容:GTX/GTH收发器管脚概述GTX/GTH收发器时钟

2021-11-11 07:42:37

完成顶层模块的实现并且仿真正确后,还需要编写用户约束文件,其中引脚约束文件是必不可少的,它将模块的端口和 FPGA 的管脚对应起来。具体步骤如下。(1)创建约束文件。新建一个源文件,在代码类型中选

2018-09-29 09:18:05

感谢电子发烧友论坛给予这次试用机会,一直想试用一下Xilinx FPGA,苦于没有太多机会。这次就让我好好领略一下Xilinx最新7系列FPGA的高大上。首先介绍一下安装板卡文件的优势:1、板载资源

2016-11-28 15:15:16

本视频是MiniStar FPGA开发板的配套视频课程,主要通过工程实例介绍Gowin的物理约束和时序约束,课程内容包括gowin的管脚约束及其他物理约束和时序优化,以及常用的几种时序约束。 本

2021-05-06 15:40:44

流程1.3.1 FPGA设计方法概论1.3.2 典型FPGA开发流程1.3.3 基于FPGA的SOC设计方法1.4 Xilinx公司主流可编程逻辑器件简介1.4.1 Xilinx FPGA芯片介绍

2012-04-24 09:23:33

右键然后点击 show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO口代表一组bank。你在吧管脚的locaTIon约束完成以后。IO Bank会自动填充完毕

2019-04-03 07:00:00

在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是

2015-01-06 17:38:22

大家好, 谁能告诉我如何在RTL或xilinx spartan fpga的约束文件中插入1.56ns延迟缓冲区?这是为了避免xilinx工具在进行合成后报告的保持时间违规。问候马赫什以上来自于谷歌

2019-06-18 07:18:04

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP产品介绍使用Xilinx的FPGA、SoC和ACAP进行设计和开发

2021-01-22 06:38:47

大家好我正在使用Virtex5 FPGA,我在设计中添加了一个OFFSET IN约束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

物理约束文件ADC可做哪些约束?

2023-08-11 08:37:29

十分钟学会Xilinx FPGA 设计

Xilinx FPGA设计基础系统地介绍了Xilinx公司FPGA的结构特点和相关开发软件的使用方法,详细描述了VHDL语言的语法和设计方法,并深入讨

2010-03-15 15:09:08 179

179 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证

2011-01-25 18:19:39 163

163 电子发烧友网:针对目前 电子发烧友网 举办的 玩转FPGA:iPad2,赛灵思开发板等你拿 ,小编在电话回访过程中留意到有很多参赛选手对 Xilinx 公司的 FPGA 及其设计流程不是很熟悉,所以

2012-06-27 13:39:47 339

339 本文是关于 xilinx公司的7系列FPGA应用指南。xilinx公司的7系列FPGA包括3个子系列,Artix-7、 Kintex-7和Virtex-7。本资料就是对这3各系列芯片的介绍。 下表是xilinx公司的7系列FPGA芯片容量对比表

2012-08-07 17:22:55 201

201 FPGA时序约束方法很好地资料,两大主流的时序约束都讲了!

2015-12-14 14:21:25 19

19 Xilinx FPGA设计进阶(提高篇)

有需要的下来看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入门教程(一)——如何搭建Xilinx FPGA开发环境

2016-01-18 15:30:32 52

52 Xilinx时序约束设计,有需要的下来看看

2016-05-10 11:24:33 18

18 FPGA学习资料教程之Xilinx时序约束培训教材

2016-09-01 15:27:27 0

0 FPGA学习资料教程之Xilinx-FPGA-引脚功能详细介绍

2016-09-01 15:27:27 0

0 研究了相关的时序约束后,在设计中我们也不能忽视所能运用到的物理约束。一个工程师最常用的物理约束是I/O管脚的放置和与每个I/O脚相关的参数定义(标准、驱动能力等)。然而,还有其它类型的物理约束

2017-02-08 02:20:11 477

477

引脚和区域约束也就是LOC约束(location)。定义了模块端口和FPGA上的引脚的对应关系。 那么我们应该怎么写呢?

2018-07-14 02:49:00 11898

11898 Xilinx FPGA编程技巧常用时序约束介绍,具体的跟随小编一起来了解一下。

2018-07-14 07:18:00 5223

5223

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

2017-02-11 06:33:11 2023

2023 xilinx 约束实现

2017-03-01 13:12:47 15

15 Xilinx FPGA的Maxim参考设计

2017-10-31 09:59:24 23

23 一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,时序约束的最终目的是实现时序收敛。时序收敛作为

2017-11-17 07:54:36 2967

2967

针对八通道采样器AD9252的高速串行数据接口的特点,提出了一种基于FPGA时序约束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行数据,利用FPGA内部的时钟管理模块DCM、位置约束

2017-11-17 12:27:01 7352

7352

本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-24 19:59:29 4435

4435

摘要:本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。 Xilinx定义了如下几种约束类型

2017-11-25 01:27:02 7029

7029

详细讲解了xilinx的时序约束实现方法和意义。包括:初级时钟,衍生时钟,异步时终域,多时终周期的讲解

2018-01-25 09:53:12 6

6 介绍FPGA约束原理,理解约束的目的为设计服务,是为了保证设计满足时序要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查

2018-06-25 09:14:00 7199

7199 观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

2019-01-07 07:10:00 7145

7145

了解如何将Altera的SDC约束转换为Xilinx XDC约束,以及需要更改或修改哪些约束以使Altera的约束适用于Vivado设计软件。

2018-11-27 07:17:00 5883

5883 本文档的主要内容详细介绍的是xilinx的FPGA芯片选型手册免费下载

2019-02-13 17:16:34 52

52 本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。

2019-02-17 11:03:52 11926

11926

本文主要介绍Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 6756

6756 1 I/O延迟约束介绍 要在设计中精确建模外部时序,必须为输入和输出端口提供时序信息。Xilinx Vivado集成设计环境(IDE)仅在FPGA边界内识别时序,因此必须使用以下命令指定超出这些边界

2020-11-29 10:01:16 6236

6236 Xilinx 7系列FPGA概览 文章目录 Xilinx 7系列FPGA概览 1.Xilinx的四个工艺级别 2.Virtex、Kintex、Artix和Spartan 3.7系列特点 4.7系列

2020-11-13 18:03:30 16550

16550 本文档的主要内容详细介绍的是Xilinx 7 系列FPGA中的Serdes总结。

2020-12-31 17:30:58 26

26 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 26

26 本文档的主要内容详细介绍的是Xilinx的时序设计与约束资料详细说明。

2021-01-14 16:26:51 34

34 引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到:

2021-05-01 09:47:00 11807

11807

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

2021-04-27 10:36:59 6127

6127

我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。

2021-04-27 10:45:29 9045

9045

AD7991 pmod Xilinx FPGA参考设计

2021-05-20 12:37:26 12

12 上一篇《FPGA时序约束分享01_约束四大步骤》一文中,介绍了时序约束的四大步骤。

2022-03-18 10:29:28 2166

2166

Xilinx FPGA开发实用教程资料包免费下载。

2022-04-18 09:43:46 29

29 本文章探讨一下FPGA的时序input delay约束,本文章内容,来源于明德扬时序约束专题课视频。

2022-07-25 15:37:07 3757

3757

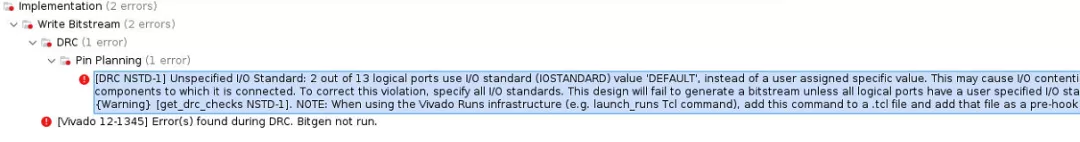

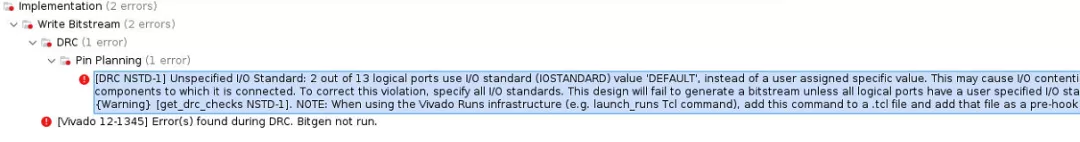

在FPGA开发中,我们经常遇到因为管脚忘记约束,导致最后生成bit的时候报错。

2022-08-02 09:02:22 1838

1838

电子发烧友网站提供《Gowin设计物理约束用户指南 .pdf》资料免费下载

2022-09-15 16:07:35 0

0 本篇主要介绍Xilinx FPGA的电源设计,主要包括电源种类、电压要求、功耗需求,上下电时序要求,常见的电源实现方案等。

2022-10-17 17:43:39 8052

8052 约束文件是FPGA设计中不可或缺的源文件。那么如何管理好约束文件呢? 到底设置几个约束文件? 通常情况下,设计中的约束包括时序约束和物理约束。前者包括时钟周期约束、输入/输出延迟约束、多周期路径约束

2022-12-08 13:48:39 2150

2150 FPGA/CPLD的综合、实现过程中指导逻辑的映射和布局布线。下面主要总结一下Xilinx FPGA时序约束设计和分析。

2023-04-27 10:08:22 2404

2404 Xilinx FPGA pcb设计

2023-05-29 09:11:36 0

0 FPGA开发过程中,离不开时序约束,那么时序约束是什么?简单点说,FPGA芯片中的逻辑电路,从输入到输出所需要的时间,这个时间必须在设定的时钟周期内完成,更详细一点,即需要满足建立和保持时间。

2023-06-26 14:42:10 1252

1252

FPGA设计中,时序约束对于电路性能和可靠性非常重要。

2023-06-26 14:53:53 6881

6881

上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

2023-09-13 12:29:37 2690

2690

Xilinx FPGA芯片拥有多个系列和型号,以满足不同应用领域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特点。

2024-03-14 16:24:41 5686

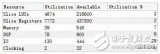

5686 LOC约束是FPGA设计中最基本的布局约束和综合约束,能够定义基本设计单元在FPGA芯片中的位置,可实现绝对定位、范围定位以及区域定位。

2024-04-26 17:05:05 2426

2426

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

2025-01-16 11:02:01 1657

1657

Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx系统设计中关键的串行通信协议。介绍了它们的特性、优势和应用场景,以及如何在不同需求下选择合适的协议。

2025-11-14 15:02:11 2357

2357

电子发烧友App

电子发烧友App

评论