XDC 是 Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC(最早由 Synopsys 公司提出,故名 Synopsys Design Constraints)。XDC 在本质上就是 Tcl 语言,但其仅支持基本的 Tcl 语法如变量、列表和运算符等等,对其它复杂的循环以及文件 I/O 等语法可以通过在 Vivado 中 source 一个 Tcl 文件的方式来补充。观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1798浏览量

133658 -

语言

+关注

关注

1文章

97浏览量

24870 -

时序

+关注

关注

5文章

411浏览量

39004

发布评论请先 登录

相关推荐

热点推荐

EHB系统MOSFET选型指南:基于热响应滞后与高频控制约束的决策清单

基于 EHB 系统的极端工况,梳理 MOSFET 选型中的物理风险,并提供结构化的条件决策清单。 一、 EHB 制动控制的核心选型约束 在为 EHB 系统的电机驱动单元进行 MOSFET 选型时,系统工程师必须框定以下前置约束条

电压放大器在主动约束层阻尼板研究测试中的应用

主动约束层阻尼结构采用压电或其他智能材料取代经典约束层阻尼结构中的约束层,并通过引入主动控制系统,进一步增强约束阻尼层对振动能量的耗散能力。即使在主动控制系统关闭或失效的情况下,仍能保

Vivado时序约束中invert参数的作用和应用场景

在Vivado的时序约束中,-invert是用于控制信号极性的特殊参数,应用于时钟约束(Clock Constraints)和延迟约束(Delay Constraints)中,用于指定信号的有效边沿或逻辑极性。

尺寸约束下商业卫星编码器系统的抗辐照MCU性能边界研究

地研究在LQFP144塑封封装所施加的物理尺寸约束条件下,商业航天级MCU的抗辐照性能边界及其在卫星编码器应用中的适配特性。 1. 引言 当前全球商业航天产业正经历由低轨宽带通信星座、地球观测星座及物联网星座驱动的爆发式增长。据

输入引脚时钟约束_Xilinx FPGA编程技巧-常用时序约束详解

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:

输入路径(Input Path),使用输入约束

寄存器到寄存器路径

发表于 01-16 08:19

声智科技提出物理信息约束的声学世界模型

scene denoising and dynamic prediction)入选,是计算声学(Computational Acoustics)领域唯一入选的中国团队。声智联合创始人常乐代表团队做了学术报告,首次介绍物理信息约束

时序约束问题的解决办法

Time 是否满足约束。

我们要留意的是 WNS 和 WHS 两个数值,如果这两个数值为红色,就说明时序不满足约束。下面将解释怎么解决这个问题。

1. Setup Time 违例

Setup

发表于 10-24 09:55

关于综合保持时间约束不满足的问题

1、将 nuclei-config.xdc 和 nuclei-master.xdc 加入到项目工程中,综合得到时序约束报告如下:

保持时间约束不满足,分析原因,发现所有不满足均出现在

发表于 10-24 07:42

技术资讯 I Allegro 设计中的走线约束设计

,能够在走线的时候清楚的知道目标在哪里,允许的误差是多少、最小间距等。上期我们介绍了如何使用cadenceAllegro的规则“约束”孔,实现一键式快速生成孔;本期我

技术资讯 I 图文详解约束管理器-差分对规则约束

!Allegro约束管理器搞差分对,简直是把高速设计的「地狱模式」切换成「新手村」!上期我们介绍了盲/埋孔的使用,本期我们将教会大家如何使用Cadence的约束管

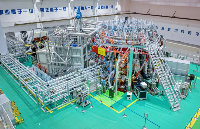

再创新高,“中国环流三号”实现百万安培亿度高约束模

近日,由核工业西南物理研究院(简称“西物院”)研制的新一代人造太阳“中国环流三号”再次创下我国聚变装置运行新纪录——实现百万安培亿度高约束模(H模),即装置同时实现等离子体电流100万安培、离子温度

西门子再收购EDA公司 西门子宣布收购Excellicon公司 时序约束工具开发商

精彩看点 此次收购将帮助系统级芯片 (SoC) 设计人员通过经市场检验的时序约束管理能力来加速设计,并提高功能约束和结构约束的正确性 西门子宣布 收购 Excellicon 公司 ,将该公司用于

PCB Layout 约束管理,助力优化设计

本文重点PCBlayout约束管理在设计中的重要性Layout约束有助避免一些设计问题设计中可以使用的不同约束在PCB设计规则和约束管理方面,许多设计师试图采用“一刀切”的方法,认为同

PanDao:实际约束条件下成像系统的初始结构的生成

摘要 :初始点的选择对后续设计过程具有重大影响。除透镜规格外,其它必要的实际约束条件也可能起到非常关键的作用。本研究采用“First Time Right”方法生成受约束的初始系统,并运用

发表于 05-07 08:57

XDC约束及物理约束的介绍

XDC约束及物理约束的介绍

评论