对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 9365

9365 线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束可能造成的时序问题,因为全

2019-02-20 10:40:44 1569

1569

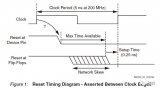

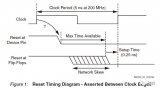

异步复位信号a是异步复位信号源,异步复位信号b、c、d是到达触发器的异步信号。我们可以看到,b信号是在本周期就撤离了复位;c信号则由于复位恢复时间不满足,则可能导致触发器输出亚稳态;而d信号则由于延时太长(但是满足了复位去除时间),在下一个周期才撤离复位。

2020-06-26 05:36:00 24583

24583

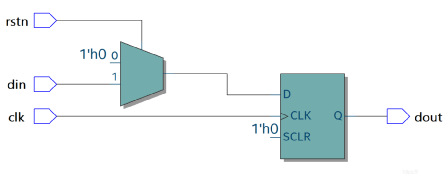

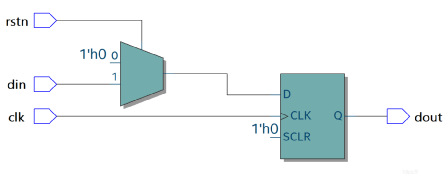

在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

2020-06-26 16:37:00 1776

1776

根据代码,容易推断得出这是一个高电平触发、异步复位的触发器(或者叫异步置位),这也与前面的内容相符合(高电平触发复位,所以不用加反相器)。

2020-11-14 11:32:00 11643

11643

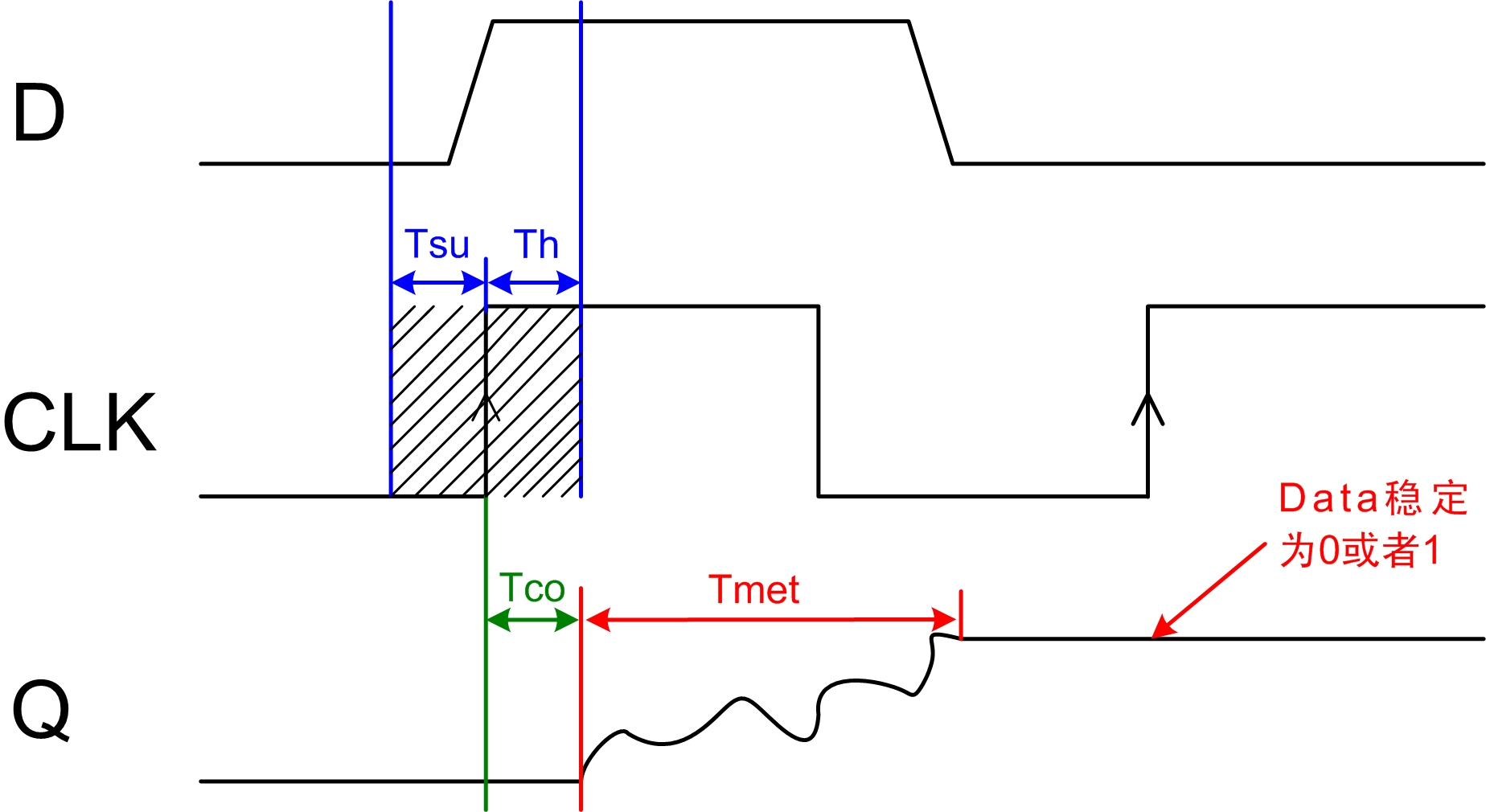

只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

2020-09-30 17:08:43 4345

4345

内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。后来也看了一些书籍,采用异步复位同步释放,对自己设计的改进。 不过自从我研读了Xilinx的White Paper后,让我对复位有了更新的认识

2020-12-25 12:08:10 3230

3230

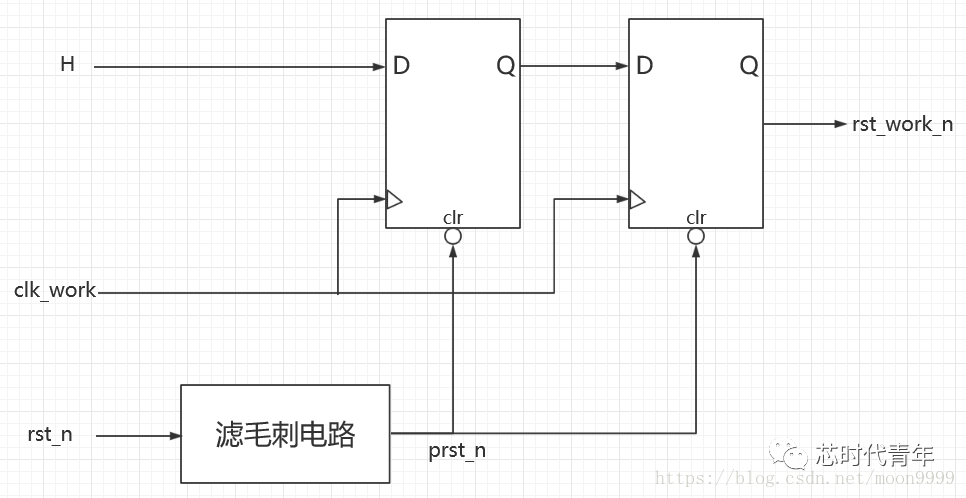

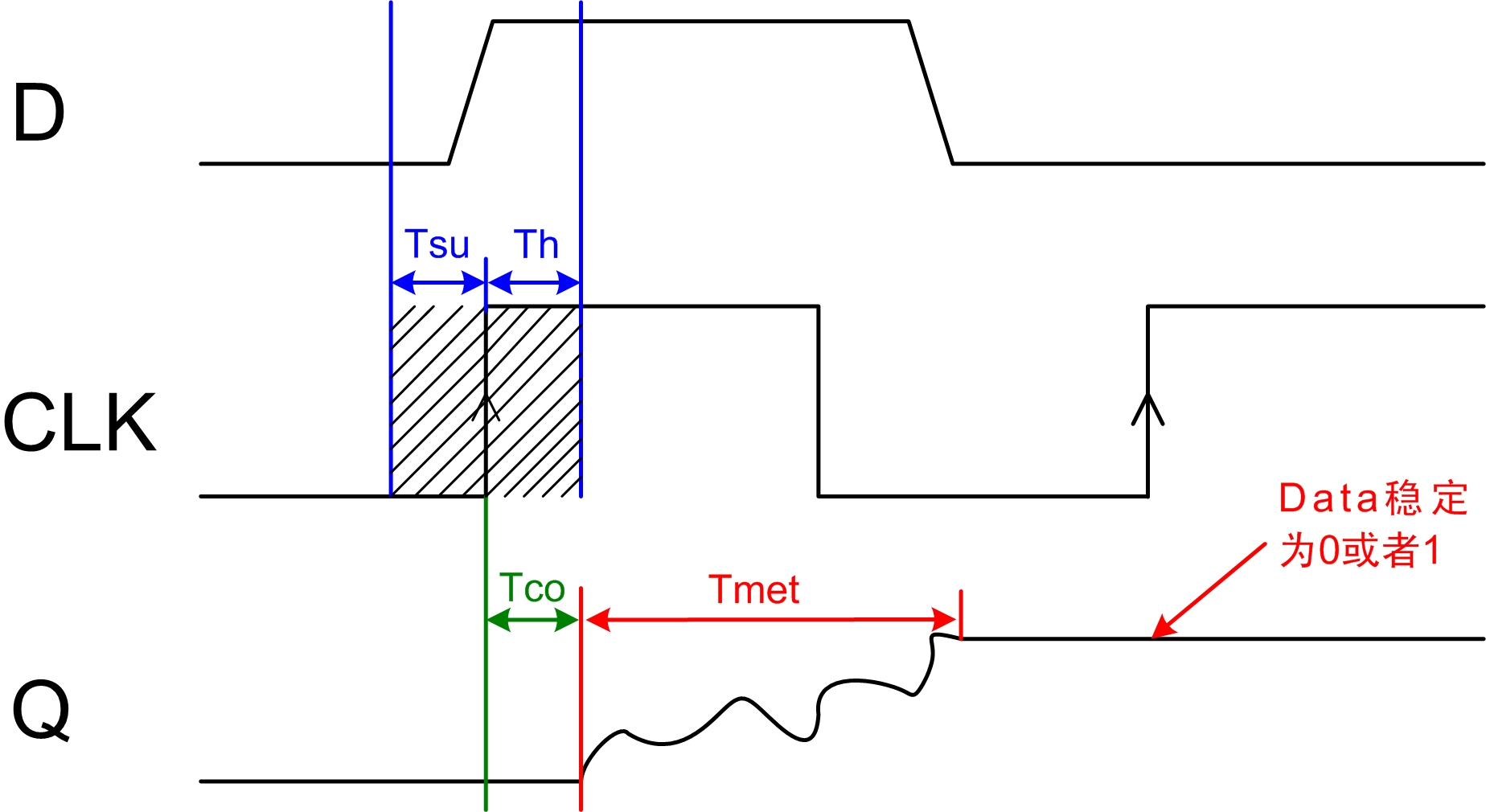

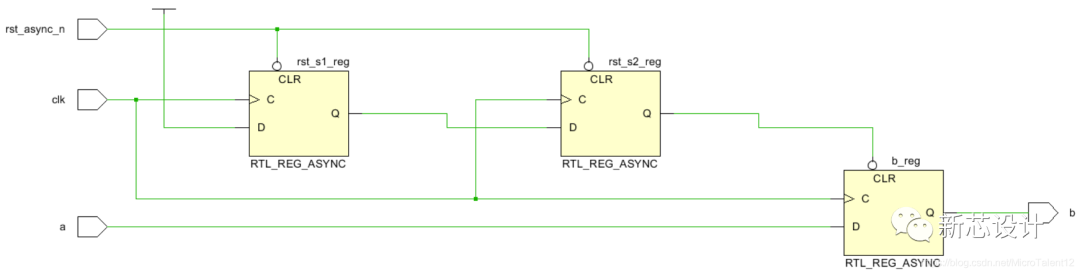

二级触发器同步后,第二季触发器的输出基本上是稳定值。后续逻辑根据稳定值,会有稳定的行为。这就是追求的系统稳定性。

2021-08-11 09:14:30 6795

6795

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 3405

3405

在FPGA设计中,当复位整个系统或功能模块时,需要将先关寄存器被清零或者赋初值,以保证整个系统或功能运行正常。在大部分的设计中,我们经常用“同步复位”或“异步复位”直接将所有的寄存器全部复位,这部分可能大家都习以为常。但实际上,是否需要每个寄存器都进行复位呢?这是一个值得探讨的问题。

2023-05-14 14:49:19 3131

3131

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2023-06-21 09:59:15 2281

2281

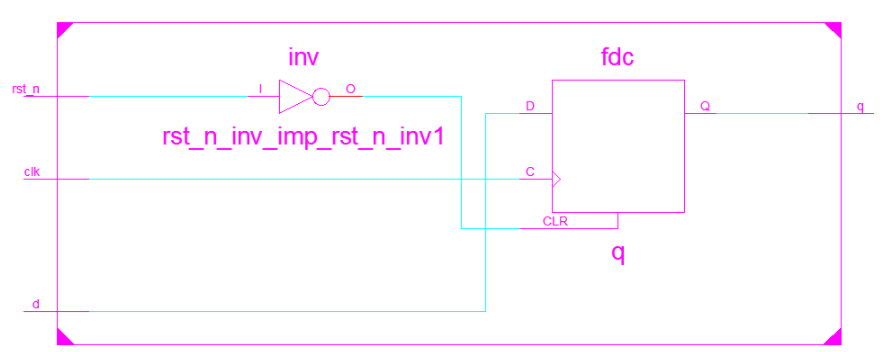

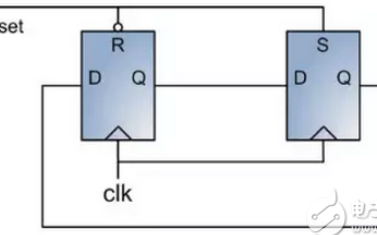

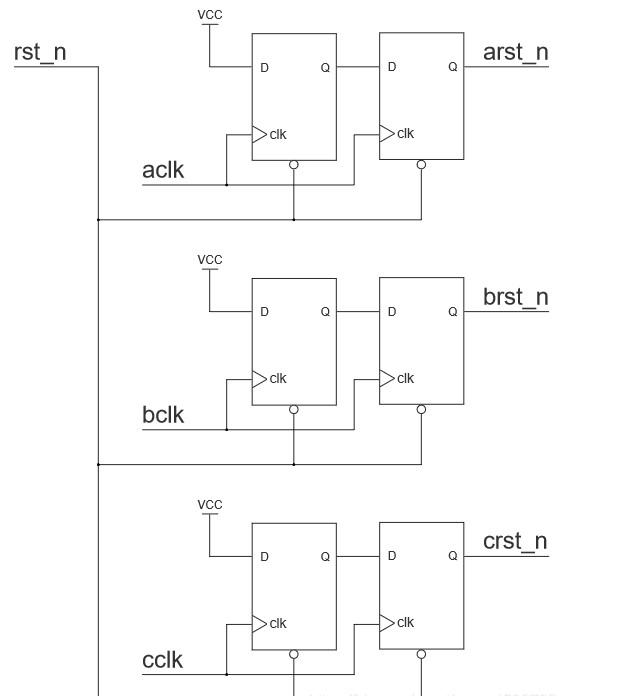

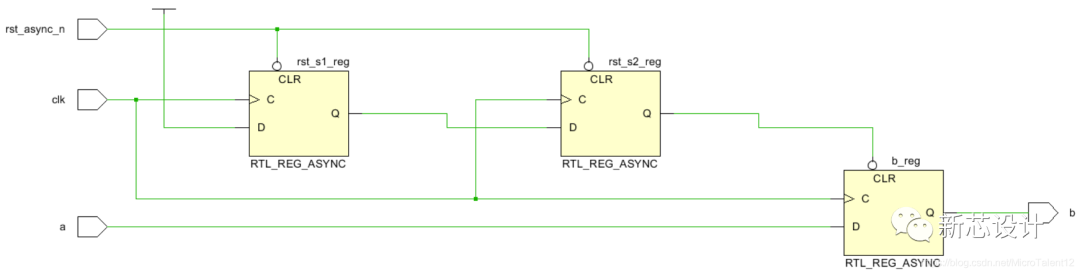

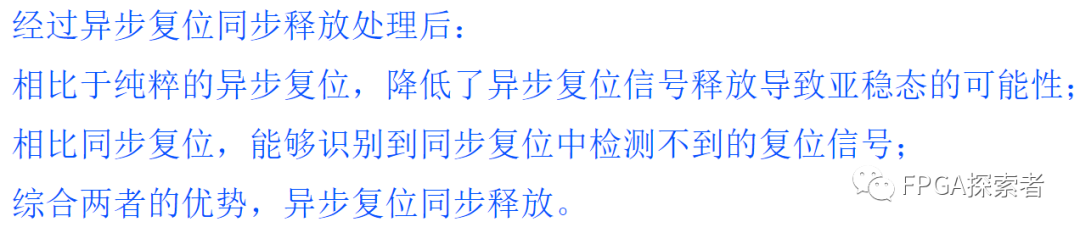

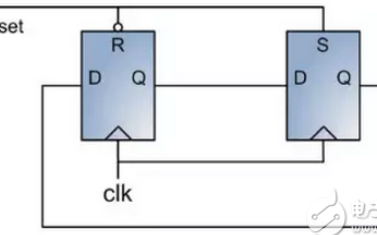

对于从FPGA外部进来的信号,我们通常采用“异步复位同步释放的策略”,具体电路如下图所示。

2023-07-20 09:04:21 2786

2786

在SOC设计中,复位电路是一个关键部分,它确保了芯片中各个模块在初始化和运行时能够处于一致的状态。

2023-08-27 14:47:16 4213

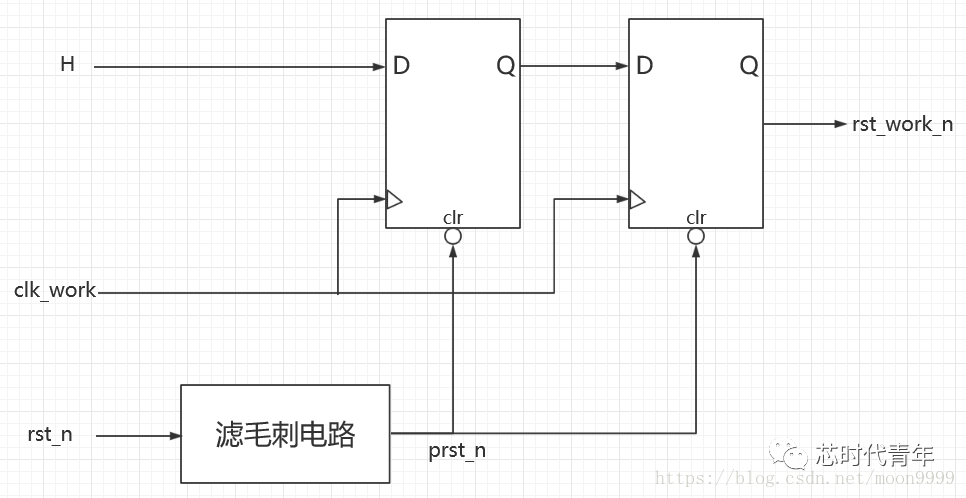

4213 复位消抖之后的下一件事,[异步复位]()同步撤离。这句话什么意思呢?

2023-12-04 13:57:39 6629

6629

一般来说,复位信号有效后会保持比较长一段时间,确保 register 被复位完成。但是复位信号释放时,因为其和时钟是异步的关系,我们不知道它会在什么时刻被释放。

2024-01-24 09:32:15 2670

2670

复位电路也是数字逻辑设计中常用的电路,不管是 FPGA 还是 ASIC 设计,都会涉及到复位,一般 FPGA或者 ASIC 的复位需要我们自己设计复位方案。复位指的是将寄存器恢复到默认值。一般复位功能包括同步复位和异步复位。复位一般由硬件开关触发引起,也可以由复位逻辑控制引起。

2025-03-12 13:54:13 3711

3711

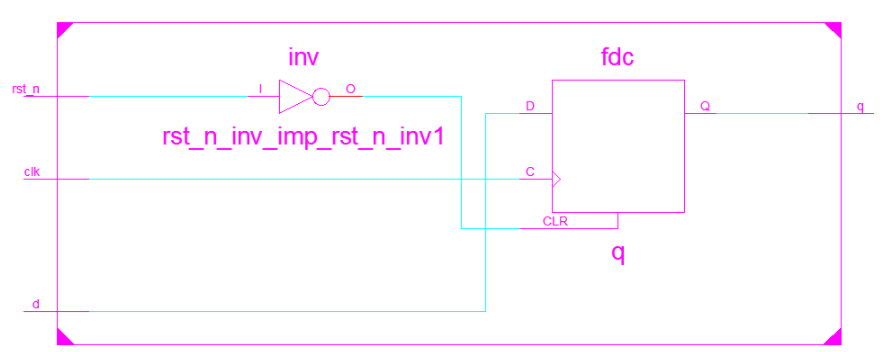

在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器

2020-10-22 11:42:16

和removal时序检查;异步复位同步撤离(推荐使用) 优点:能避免纯异步或纯同步复位的潜在问题。它是FPGA设计中最受欢迎的复位,Altera建议使用这种复位方法。这种复位在使用前需要同步到各个使用时

2014-03-20 21:57:25

,而是在复位信号释放的时候受到时钟信号的同步。通过一个复位信号综合器就可以实现异步复位,同步释放。 使用复位信号综合器可以很好地将同步和异步复位的优点结合起来,而消除他们缺点。因此在FPGA/CPLD

2011-11-04 14:26:17

摘要:FPGA异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的几种同步策略。关键词

2009-04-21 16:52:37

线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束

2019-05-17 08:00:00

下面对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用

2021-06-30 07:00:00

%的同步时序电路,有利于时序分析。1)设计相对简单。2)因为大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以节省资源。3)异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口

2011-11-14 16:03:09

在网上了解到fpga的同步复位和异步复位都会存在不足,因此有人提出异步复位,同步释放的方法来消除两者的不足。对此也提出一些疑问,还请大家能指导一下:1、同步复位,同步复位的缺点包括需要复位信号的宽度

2014-04-16 22:17:53

异步复位,同步释放的理解目录目录同步复位和异步复位异步复位 同步复位 那么同步复位和异步复位到底孰优孰劣呢?异步复位、同步释放问题1 问题2 问题3 问题4 问题5参考资料同步复位和异步复位异步复位

2022-01-17 07:01:53

简单。 c、异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR。 缺点:a、在复位信号释放(release)的时候容易出现问题。具体就是说:倘若复位释放时恰恰在时钟有效沿附近,就很

2018-07-03 02:49:26

的影响。三、总结:所以说,一般都推荐使用异步复位,同步释放的方式,而且复位信号低电平有效。四、推荐复位方式推荐的复位方式上面提到的“异步复位,同步释放”。这就结合了上方面的优点,很好的克服了异步复位的缺点

2016-05-05 23:11:23

复位中的同步复位和异步复位问题:恢复时间是指异步复位信号释放和时钟上升沿的最小距离,在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步控制

2022-01-17 06:08:11

。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-11 06:06:08

fpga 的 异步复位同步释放代码如下module asy_rst(clk,rst_n,asy_rst);input clk;input rst_n;output asy_rst;reg

2013-05-28 13:02:44

没有被时钟采到,则可能会导致不能有效复位。那么有没有什么好办法呢?当然有啦,下面就要介绍在实际设计中常用的复位方案,即同步确立,异步释放方案:这种方案确立时是瞬间同时对所有寄存器复位的,而释放时则要

2012-12-05 17:09:26

FPGA 异步reset 问题:⑴ 阅读下面文章,写出关键点,并给出自己的理解;⑵ 查看下面代码,结合文章,指出代码所表达的涵义。文章: 代码:1. 文章主要讲复位信号最好用同步复位,否则

2012-03-14 15:10:21

本帖最后由 何立立 于 2015-6-7 20:59 编辑

最近遇到FPGA复位信号的问题困扰很久,查了相关资料:FPGA设计是基于大量flip-flop或者寄存器的同步系统设计,所以所有这些

2015-06-07 20:39:43

复位还是应该使用异步复位。实际上,无论是同步复位还是异步复位都有各自的优缺点。在这里梦翼师兄和大家一起学习另外一种复位信号的处理方式-异步复位同步释放。 基本概念FPGA设计中常见的复位方式有同步复位

2019-12-04 10:18:49

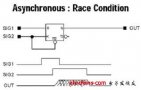

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?时序设计的实质是什么?

2021-09-29 07:33:38

什么是同步逻辑和异步逻辑,同步电路和异步电路的区别是什么?

2021-06-18 08:52:44

) 对复位电路采用异步复位、同步释放方式处理。[tr][tr]

[tr][tr]1、对异步信号进行同步提取边沿[tr][tr]在异步通信或者跨时钟域通信过程中,最常用的就是对异步信号进行同步提取边沿处理

2023-04-27 17:31:36

常用的异步复位,会由于复位组合逻辑电路的的毛刺影响较大,导致设计的不稳定性,而同步复位,又会增加额外的逻辑资源,这都是我们不想见到的,由此引入了异步复位同步释放电路(参考特权的设计)整体来看,在

2016-09-28 11:00:59

性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。在FPGA中,同步信号、异步信号和亚稳态的理解PGA(Field-Programmable Gate Array),即现场

2023-02-28 16:38:14

亚稳态概述01 亚稳态发生原因在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足

2020-10-19 10:03:17

同步复位,何时采用异步复位;2. 复位电路是用来干嘛的;3. 激励和响应的分析(单拍潜伏期)是否适用与复位逻辑。1. 电路中,何时采用同步或异步,取决与设计者,取决于当前设计电路的需要。一般而言:高速

2018-04-24 13:23:59

、电路中,何时采用同步或异步,取决于设计者,取决于当前设计电路的需要。一般而言:高速逻辑应该采用同步复位,低速逻辑可以采用异步复位;涉及人机交互的复位,适合异步复位;涉及机器之间的握手交互,应该采用

2023-05-22 17:33:12

我一直在试验如何在Vivado中“解释”简单计数器上的异步与同步复位。这是我的(10位)计数器模板:图书馆IEEE;使用IEEE.STD_LOGIC_1164.ALL

2019-04-25 07:57:01

` 大家好,谈到同步复位和异步复位,那咱们就不得不来聊一聊复位这个词了。在数字逻辑电路设计中,电路通过复位来启动,复位犹如数字电路的“起搏器”。那在设计中,主要会出现以下三种类型的,一是无复位

2018-01-30 11:01:58

请问异步复位和同步复位是否可以共存?有什么影响?

2014-10-08 17:50:43

FPGA 异步时钟设计中如何避免亚稳态的产生是一个必须考虑的问题。本文介绍了FPGA 异步时钟设计中容易产生的亚稳态现象及其可能造成的危害,同时根据实践经验给出了解决这些问题的

2011-12-20 17:08:35 63

63 异步复位相比同步复位: 1. 通常情况下(已知复位信号与时钟的关系),最大的缺点在于异步复位导致设计变成了异步时序电路,如果复位信号出现毛刺,将会导致触发器的误动作,影响

2012-04-20 14:41:48 4874

4874

同步异步通信转换的CPLD_FPGA设计,有需要的下来看看

2016-12-16 22:13:20 8

8 前两天和师兄讨论了一下design rule其中提到了同步异步复位的比较这个常见问题,据说也是IC公司经常问到的一面试题。

2017-02-11 05:56:11 2560

2560 顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。

2017-02-11 12:40:11 8741

8741

在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 6340

6340

异步复位原理:异步复位只要有复位信号系统马上复位,因此异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放。

2017-11-30 08:45:46 99838

99838

是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

2017-11-30 08:58:14 25411

25411

大家好,谈到同步复位和异步复位,那咱们就不得不来聊一聊复位这个词了。在数字逻辑电路设计中,电路通过复位来启动,复位犹如数字电路的起搏器。那在设计中,主要会出现以下三种类型的,一是无复位:天生就强壮

2018-05-17 09:30:28 13591

13591

同步复位,何时采用异步复位;2. 复位电路是用来干嘛的;3. 激励和响应的分析(单拍潜伏期)是否适用与复位逻辑。 1. 电路中,何时采用同步或异步,取决与设计者,取决于当前设计电路的需要。一般而言:高速逻辑应该采用同步复位,

2018-06-11 15:15:11 7350

7350 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 7577

7577 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 12709

12709 通常情况下,复位信号的异步释放,没有办法保证所有的触发器都能在同一时间内释放。触发器在A时刻接收到复位信号释放是最稳定的,在下一个时钟沿来临被激活,但是如果在C时刻接收到复位信号释放无法被激活,在B时刻收到复位信号释放,则会引起亚稳态。

2018-11-19 10:34:01 10313

10313

异步复位是不受时钟影响的,在一个芯片系统初始化(或者说上电)的时候需要这么一个全局的信号来对整个芯片进行整体的复位,到一个初始的确定状态。

2019-01-04 08:59:20 7194

7194 异步复位同步释放是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

2019-11-20 07:06:00 4715

4715 首选我们来聊聊时序逻辑中最基础的部分D触发器的同步异步,同步复位即复位信号随系统时钟的边沿触发起作用,异步复位即复位信号不随系统时钟的边沿触发起作用,置数同理,rst_n表示低电平复位,我们都知道D

2019-07-26 10:17:16 27982

27982

同步复位和异步复位都是状态机的常用复位机制,图1中的复位电路结合了各自的优点。同步复位具有时钟和复位信号之间同步的优点,这可以防止时钟和复位信号之间发生竞争条件。但是,同步复位不允许状态机工作在直流时钟,因为在发生时钟事件之前不会发生复位。与此同时,未初始化的I/O端口可能会遇到严重的信号争用。

2019-08-12 15:20:41 8229

8229

复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑,诸如:clk skew,组合 逻辑路径延时,复位延时等因素。

2019-08-21 17:51:49 2198

2198 先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 3320

3320

FPGA开发中,一种最常用的复位技术就是“异步复位同步释放”,这个技术比较难以理解,很多资料对其说得并不透彻,没有讲到本质,但是它又很重要,所以对它必须理解,这里给出我的看法。

2020-08-18 13:56:00 1741

1741

同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。用Verilog描述如下:异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。用Verilog描述如下:

2020-09-14 08:00:00 0

0 1、什么是同步逻辑和异步逻辑,同步电路和异步电路的区别是什么? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 电路设计可分类为同步电路和异步电路设计。同步电路利用

2020-11-09 14:58:34 10830

10830 DFF 都有异步复位端口,因此采用异步复位可以节约资源。 ⑵设计相对简单。 ⑶异步复位信号识别方便,而且可以很方便地使用 fpga 的全局复位端口。 缺点:⑴在复位信号释放时容易出现问题,亚稳态。 ⑵复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原

2020-10-30 12:17:55 951

951 在FPGA设计中,我们遵循的原则之一是同步电路,即所有电路是在同一时钟下同步地处理数据。这个概念可进一步展开,即不局限于同一时钟,只要时钟之间是同步关系,这是因为目前的芯片规模越来越大,设计越来越复杂,往往需要多个时钟同时运算。

2021-04-09 11:29:55 3781

3781

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2021-04-27 18:12:10 5626

5626

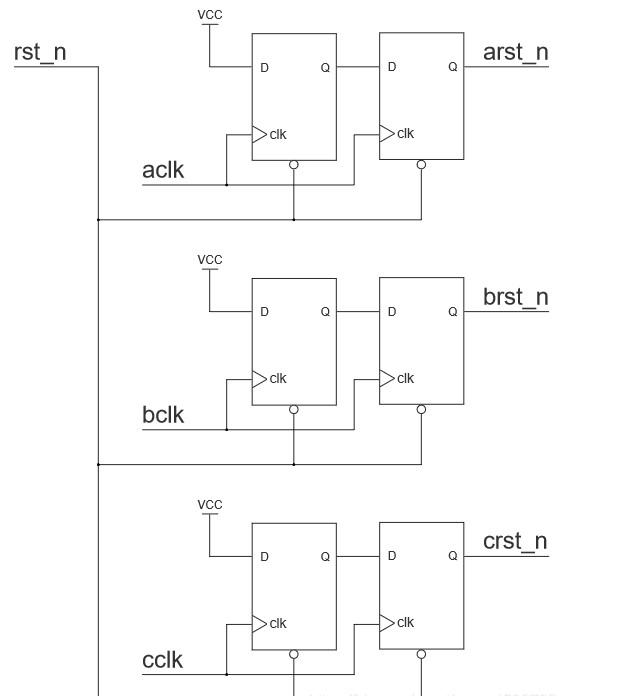

1 多时钟域的异步复位同步释放 当外部输入的复位信号只有一个,但是时钟域有多个时,使用每个时钟搭建自己的复位同步器即可,如下所示。 verilog代码如下: module CLOCK_RESET

2021-05-08 09:59:07 3063

3063

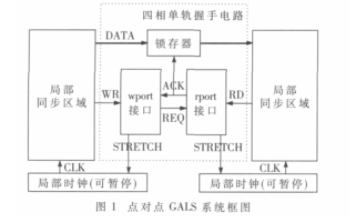

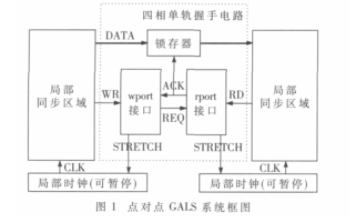

在常规FPGA中设计了基于LUT的异步状态保持单元,实现了全局异步局部同步系统的接口电路、时钟暂停电路,进一步完

2021-05-26 18:12:38 4816

4816

。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。常见的复位方式有三种1、硬件开关:复位信号接一个拨码开关或按键,.

2021-11-06 09:20:57 20

20 在DCDC降压电路中存在同步整流和异步整流两种工作方式,这两种方式的工作原理图如下从上图可以看出,异步整流和同步整流的区别,就在于同步整流采用了通态电阻极低的MOSFET管代替了二极管。相比于异步

2021-11-07 12:21:00 7

7 复位中的同步复位和异步复位问题:恢复时间是指异步复位信号释放和时钟上升沿的最小距离,在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步控制

2022-01-17 12:25:49 0

0 异步复位,同步释放的理解目录目录 同步复位和异步复位 异步复位 同步复位 那么同步复位和异步复位到底孰优孰劣呢? 异步复位、同步释放 问题1 问题2 问题3 问题4 问题5 参考资料同步

2022-01-17 12:53:57 4

4 首先回想一下,在平常的设计中我们是不是经常采用同步复位或者异步复位的写法,这一写法似乎都已经形成了肌肉记忆----每次我们写always块的时候总是会对所有的寄存器写一个复位赋初值的语句。

2022-02-19 19:10:32 2936

2936 可预置同步4位二进制计数器;异步复位-74LVC161

2023-02-15 19:23:09 0

0 可预置同步4位二进制计数器;异步复位-74HC161_Q100

2023-02-16 21:10:00 1

1 可预置同步4位二进制计数器;异步复位-74HC161

2023-02-16 21:10:17 4

4 可预置同步BCD十进制计数器;异步复位-74HC160

2023-02-20 20:05:50 11

11 为确保系统上电后有一个明确、稳定的初始状态,或系统运行状态紊乱时可以恢复到正常的初始状态,数字系统设计中一定要有复位电路的设计。复位电路异常可能会导致整个系统的功能异常,所以在一定程度上来讲,复位电路的重要性也不亚于时钟电路。

2023-03-28 13:54:33 8204

8204

FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 1882

1882 。 下面将讨论FPGA/CPLD的复位电路设计。 2、分类及不同复位设计的影响 根据电路设计,复位可分为异步复位和同步复位。 对于异步复位,电路对复位信号是电平敏感的,如果复位信号受到干扰,如出现短暂的脉冲跳变,电路就会部分或全部被

2023-04-06 16:45:02 2170

2170 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 6199

6199

SoC设计中通常会有“全局”同步复位,这将影响到整个设计中的大多数的时序设计模块,并在同一时钟沿同步释放复位。

2023-05-18 09:55:33 524

524

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。

2023-05-22 14:21:08 1907

1907

本文主要是提供了 ASIC 设计中关于复位技术相关的概念和设计。

2023-06-21 11:55:15 13439

13439

使用 2 个带异步复位的寄存器,D端输入逻辑 1(VCC)。

2023-06-26 16:39:17 2273

2273

请简述同步复位与异步复位的区别,说明两种复位方式的优缺点,并解释“异步复位,同步释放”。

2023-08-14 11:49:35 8575

8575 异步复位同步释放:rst_synchronizer.v

2023-08-21 09:27:51 1792

1792

点击上方 蓝字 关注我们 系统的复位对于系统稳定工作至关重要,最佳的复位方式为:异步复位,同步释放。以下是转载博客,原文标题及链接如下: 复位最佳方式:异步复位,同步释放 异步复位; 异步

2023-09-09 14:15:01 2217

2217

RC复位电路中R如何影响芯片复位? RC复位电路是常见的一种复位电路,它通过串联一个电阻和一个电容元件来实现对芯片的复位功能。在RC电路中,电容元件起到存储电荷、延迟释放电荷的作用,而电阻元件起到

2023-10-25 11:07:51 2247

2247 同步复位和异步复位到底孰优孰劣呢? 同步复位和异步复位是两种不同的复位方式,它们各自有优势和劣势,下面将详细介绍这两种复位方式。 同步复位是指在时钟的边沿(上升沿或下降沿)发生时对系统进行复位。这种

2024-01-16 16:25:52 2718

2718 FPGA(现场可编程门阵列)在处理异步信号时,需要特别关注信号的同步化、稳定性以及潜在的亚稳态问题。由于异步信号可能来自不同的时钟域或外部设备,其到达时间和频率可能不受FPGA内部时钟控制,因此处理起来相对复杂。以下是对FPGA异步信号处理方法的详细探讨。

2024-07-17 11:10:40 2415

2415 FPGA(Field-Programmable Gate Array,现场可编程门阵列)中的复位操作是设计过程中不可或缺的一环,它负责将电路恢复到初始状态,以确保系统的正确启动和稳定运行。在FPGA设计中,复位方式主要分为同步复位和异步复位两种。以下是对这两种复位方式的详细探讨。

2024-07-17 11:12:21 3320

3320 都有异步复位端口,因此采用异步复位可以节约资源。 ⑵设计相对简单。 ⑶异步复位信号识别方便,而且可以很方便地使用fpga的全局复位端口。 缺点:⑴在复位信号释放时容易出现问题,亚稳态。 ⑵复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原

2024-11-15 11:13:55 911

911

其它输入引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。 不过在一些提示和技巧的帮助下,设计人员可以找到更加合适的复位结构。理想的复位结构可以改善 FPGA 中器件的利用率、

2024-11-16 10:18:13 1804

1804

本文讲述了AMD UltraScale /UltraScale+ FPGA 原生模式下,异步模式与同步模式的对比及其对时钟设置的影响。

2025-07-07 13:47:34 1494

1494

电子发烧友App

电子发烧友App

评论