随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在FPGA中的动态调频与展频功能应用。

2025-06-20 11:51:12 2360

2360

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 9365

9365 本文描述了复位的定义,分类及不同复位设计的影响,并讨论了针对FPGA和CPLD的内部自复位方案。

2016-07-11 14:33:49 7289

7289

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 2079

2079

: ① 首先,上电后肯定是要复位一下,不然仿真时会出现没有初值的情况; ② 最好有个复位的按键,在调试时按一下复位键就可以全局复位了; ③ 也许是同步复位,也许是异步复位,不同的工程师可能有不同的方案。 但

2020-11-18 17:32:38 6564

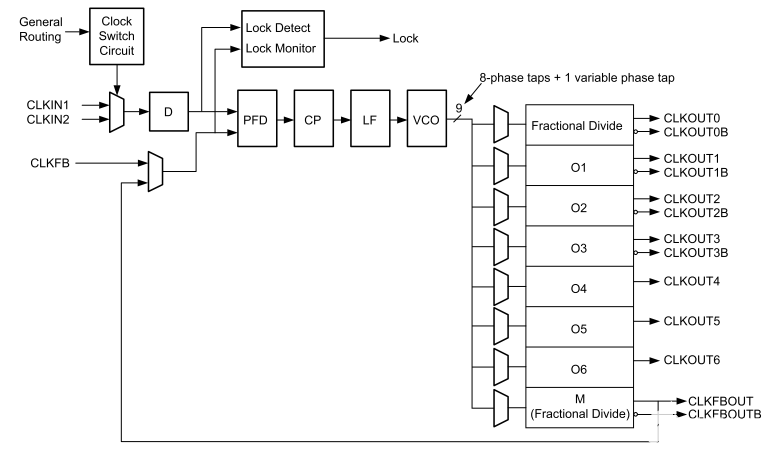

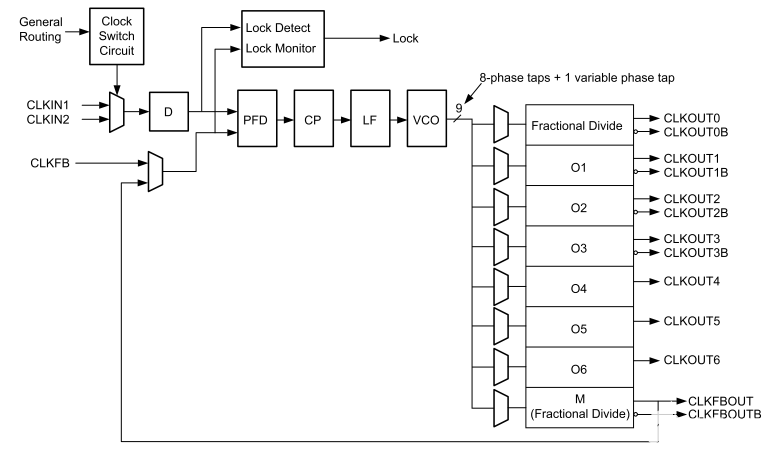

6564 PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPGA系统往往需要多个不同频率,相位的时钟信号。所以,一个FPGA芯片中PLL的数量是衡量FPGA芯片

2021-01-22 09:41:11 5920

5920

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 3405

3405

在FPGA设计中,当复位整个系统或功能模块时,需要将先关寄存器被清零或者赋初值,以保证整个系统或功能运行正常。在大部分的设计中,我们经常用“同步复位”或“异步复位”直接将所有的寄存器全部复位,这部分可能大家都习以为常。但实际上,是否需要每个寄存器都进行复位呢?这是一个值得探讨的问题。

2023-05-14 14:49:19 3131

3131

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24:03 16812

16812

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2023-06-21 09:59:15 2281

2281

TJ375已经支持PLL的动态配置。打开PLL在Advance Settings中的Dynamic Reconfiguration中勾选Enable就可以了。最大可以支持85组配置参数。动态配置框图

2025-07-14 18:14:01 3113

3113

。输入 PLL1 参考时钟设置为 100MHz。 问题是由于更改DLYDIV_SEL 是重新配置PLL,是否必须遵循19.6.4.3 中定义的PLL 复位和重新配置流程?在更改 PLL

2023-04-18 08:25:33

Flash进行上电加载,在系统上电稳定后,FPGA器件首先需要足够的时间用于配置加载操作,只有在这个过程结束之后,FPGA器件才能够进入正常的用户运行模式。而上电复位延时过短,等同于FPGA器件根本

2019-04-12 06:35:31

在配置PLL过程中,打开了megawizard plug-in manager后,下拉菜单中没有IO这个选项,更别说选ATLPLL了,求问这是什么情况!PLL配置教程原帖http

2017-03-22 09:58:41

或Flash进行上电加载,在系统上电稳定后,FPGA器件首先需要足够的时间用于配置加载操作,只有在这个过程结束之后,FPGA器件才能够进入正常的用户运行模式。而上电复位延时过短,等同于FPGA器件根本

2015-04-10 13:59:23

FPGA器件启动后的配置加载时间,这样才能够确保FPGA运行后的复位初始化过程有效。因此,我们也可以来看看这个电路的设计是否满足实际要求。(特权同学,版权所有)如图3.19所示,这是器件手册中关于上电配置

2015-04-24 08:17:00

系统误复位。内部复位,FPGA上电配置完成后,由FPGA内部电路产生复位信号,复位信号与时钟同步。通常内部复位的设计方法是:设计一个初始值为0X0000的SRL16,将其输人接高电平,输出作为复位信号

2021-06-30 07:00:00

PLL后复位问题怎么解决?

2021-05-08 08:48:55

如何用PLL对时钟进行配置呢?PLL配置时钟唤醒后还需要重新配置RCC吗?

2021-11-22 06:30:33

你好,我想使用特定的FPGA(V5或V6)。在特殊条件下,FPGA应在复位或丢失与电源的连接后重新编程。这应该通过使用PROM自动完成。该舞会将在董事会中进行整合。现在我正在使用ML507 EV板

2020-06-10 10:24:51

;2.2)初始化配置中ENSM为TDD模式,初始化后查询发现BBPLL和 RF Rx PLL都是Locked,但是Tx PLL不是Locked,配置状态机进入 TDD Tx,频谱出来的信号频点不对

2018-08-22 09:19:41

。通过写寄存器将AD9364状态置为FDD状态时(reg[0x017]=0x1A),发现FPGA内部PLL不能保持锁定状态了。 请教大家哪个寄存器的配置有问题会造成上述现象?附件1.png17.2 KB

2018-08-20 07:20:29

Altera可重配置PLL使用手册在实际应用中,FPGA的工作时钟频率可能在几个时间段内变动,对于与之相关的锁相环(PLL),若PLL的输入时钟在初始设定的时钟频率的基础上变化不太大时,PLL一般

2009-12-22 11:27:13

1. DSP上电复位配置什么? DSP的大、小端,自启动(boot)模式,PCIe模式,网络协处理器时钟选择需要在上电复位的时候选择,怎么选择? 依靠上电时候锁定DSP Device

2020-12-14 16:01:54

输出时钟占空比不同的功能。保持默认:50。点击Next。选择输入输出端口,这里RESET为复位端口,高电平有效。LOCKED为输出有效端口,此端口可以看到PLL输出稳定的时间段。此界面配置输入输出抽头

2023-04-06 16:04:21

,ADC值相差不大,但是采用PLL异步时钟,复位后有概率ADC采样值发生偏差(所以我怀疑复位后ADC时钟出现了问题)。

补充:问题芯片具体是L431RCT6,我还有一块L431CCT6的芯片,同样的配置,同样的代码逻辑,ADC采样值就很准确且稳定。

以下是时钟树与ADC配置(PLL时钟)

2024-03-08 07:32:15

、5dBm正弦波,从CLKin1输入。通过FPGA抓取芯片IO输出的PLL_DLD信号。发现PLL1偶尔会失锁,失锁后大约0.16ms再锁定;PLL2始终锁定。请问PLL1失锁的原因可能是什么,是否是配置不对。

2024-11-11 06:54:20

在使用中我发现在Autostart启用时,将LMK61E07由100M配置为125M后实际输出频率为130M+。

在未启用Autostart时复位PLL并重新置位Autostart或置位

2024-11-11 06:44:29

最近在使用STM32F407系列,当使用HSI时钟后,PLL最高只能配置到42MHz,找了很多文档也没有介绍这方面的资料。如果超过42Mhz,就会发生跑飞的情况。我也试过配置到48MHz,也是会跑飞

2024-04-26 07:49:34

方法:1.生成hex文件,方法如下图:2.生成的hex文件后缀为.hexout,改为.hex,然后把BOOT0插针短路,按键复位单片机,单片机串口连接电脑;3.使用STM32CubeProgrammer软件固化FPGA程序,方法如图:4.下载成功后,去掉BOOT0跳线帽,按键复位单片机

2021-11-26 07:32:14

进了STOP模式后,PLL停掉了,所以,如果开始的时钟配置,用的是PLL,那么唤醒后,需要重新配置RCC。如果使用的是PLL,及时是用MSI作为时钟源,放大出来的,比如4M的MSI,PLL放大到

2021-08-18 08:17:53

Xilinx FPGA入门连载24:PLL实例之基本配置 1 工程移植可以复制上一个实例sp6ex7的整个工程文件夹,更名为sp6ex8。然后在ISE中打开这个新的工程。 2 新建IP核文件

2019-01-21 21:33:40

`Xilinx FPGA入门连载17:PWM蜂鸣器驱动之复位与FPGA重配置功能特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm1 复位

2015-10-26 12:05:15

内部的各个功能模块使用。 2 功能简介如图所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz

2015-11-10 08:44:06

`Xilinx FPGA入门连载24:PLL实例之基本配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 工程移植可以复制上一个实例

2015-11-16 12:09:56

如题,ad9689的型号是2.6G,按照文档81页的配置方式将AD9689配置完成,读取0x056f检测AD的PLL锁定,

工作的采样率为2.2G,给AD的输入时钟是2.2G,给FPGA

2023-12-06 06:52:08

quartus中PLL的复位是高电平复位还是低电平复位,可不可以修改

2014-03-21 11:10:25

`PLL锁相环介绍与简单应用实验目的:1.学会配置Altera提供的PLL IP核并进行仿真了解其接口时序2.利用参数化设计一个简易的系统进行验证已配置好的PLL实验平台:芯航线FPGA学习套件主板

2017-01-05 00:00:52

稳定后,FPGA器件首先需要足够的时间用于配置加载操作,只有在这个过程结束之后,FPGA器件才能够进入正常的用户运行模式。而上电复位延时过短,等同于FPGA器件根本就没有复位过程;当然了,如果上电复位

2016-07-25 15:19:04

的RC电路,也是连接到FPGA的专用输入时钟引脚,走内部全局时钟网络。 图2.16 FPGA时钟和复位电路FPGA上电复位时间需要大于FPGA器件启动后的配置加载时间,这样才能够确保FPGA运行后的复位

2016-08-08 17:31:40

的效果。该实例的功能框图如图3.1所示。FPGA外部引脚的复位信号进入FPGA后,首先做了一次“异步复位,同步释放”的处理,然后这个复位信号输入到PLL模块,在PLL模块输出时钟有效后,它的锁定信号

2016-09-09 18:29:24

`例说FPGA连载31:PLL例化配置与LED之PLL的IP核配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1c0nf6Qc 本实例使用了一个

2016-09-12 17:31:43

8.17所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100MHz的时钟信号,这4路时钟信号又分

2018-04-19 19:00:56

`勇敢的芯伴你玩转Altera FPGA连载63:PLL IP核创建于配置特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1i5LMUUD 可以复制上一个

2018-04-20 21:45:06

PLL 配置后是否按预期工作,我该怎么做。 EVAL 板上是否有任何测试点,我可以用它来进行测距和测试,或者我是否需要配置 ECO_OUT 以测量 160Mhz 频率。 在 ECO_OUT 测试时,我只能看到 16Mhz 的脉冲。

您能提出测试方法吗?

2024-05-20 07:07:59

_clk,把FPGA的系统时钟50Mhz连接到pll_clk的inclk0,系统复位信号连接到pll_clk的areset,因为锁相环是高电平复位,而输入的系统复位信号sys_rst_n是低电平复位,所以在

2020-07-30 14:58:52

本人做课设,想用FPGA输出一个方波作为时钟信号,使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下载了程序之后,发现只有上电和手动复位后

2016-12-08 16:20:03

的IP核,通过这个IP核,我们可以配置一个PLL用于对FPGA外部输入时钟做各种分频或倍频处理。点击Clocking Wizard后将弹出相应的配置页面。图 Clocking Wizard IP核

2019-09-06 08:13:18

C6713 PLL1、硬件外部有个复位键,RESET,PLL配置时有个和PLL_reset,这两个是什么关系呢?没什么联系吧?2、PLL配置时,比如lock过程,需要有计时,等待PLL稳定,这个计时

2018-07-25 06:18:41

请问,想通过FPGA的PLL倍频产生个500MHz的时钟来使用,以此时钟来做定时精密延迟,不知道PLL倍频倍数有什么要求,比如好像有的器件支持不到500MHz,有没有可推荐的器件呢

补充内容 (2017-1-4 09:26):

或者有大神用过类似能到500MHz的FPGA推荐么

2017-01-03 17:04:23

本文档主要是以Altera公司的Stratix II系列的FPGA器件为例,介绍了其内嵌的增强型可重配置PLL在不同的输入时钟频率之间的动态适应,其目的是通过提供PLL的重配置功能,使得不需要对

2010-11-02 15:17:24 27

27 在开始查找PLL的最佳配置之前,需要考虑的是如何才能为PLL找到配置。具体而言,我们应找到PLL针对给定参考振荡器和所需输出频率所使用的所有可行配置。只有在确保获得能够满足需

2012-11-22 10:34:32 7871

7871 FPGA Cyclone器件中PLL的配置方法

2016-02-23 11:04:13 5

5 在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 1232

1232

在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 6340

6340

外电路编程FPGA或是编程Flash器件(包括EPCS和Flash),然后控制FPGA的配置复位引脚来复位整个FPGA,最后FPGA采用主串方式进行自我配置。另一种是,通过FPGA中的Nios CPU或是

2017-12-13 13:58:10 26639

26639

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 2563

2563 下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30:02 7797

7797

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 7577

7577 在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

2018-08-07 09:17:18 12506

12506 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 12709

12709 主设备可以为控制器,CPLD等等。当然FPGA也支持通过JTAG的方式进行程序下载,同时也可以通过JTAG进行FPGA时序抓取。 FPGA的配置过程包括以下几方面:复位,程序加载,初始化,最后进入用户

2018-11-18 18:05:01 831

831 一开始接触到FPGA,肯定都知道”复位“,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。

2019-02-17 10:49:53 8909

8909

FPGA设计中,层次结构设计和复位策略影响着FPGA的时序。在高速设计时,合理的层次结构设计与正确的复位策略可以优化时序,提高运行频率。

2019-02-15 15:15:53 1270

1270 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 951

951 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 本文档的主要内容详细介绍的是在FPGA上编写通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序免费下载。

2021-03-10 15:50:00 61

61 FPGA 主动方式:由 FPGA来主动输出控制和同步信号给 FPGA的串行配置芯片(EPCS系列) ,配置芯片收到命令后,把配置数据发给 FPGA,完成配 置过程;在 AS模式下,FPGA必须

2021-04-06 15:33:02 8

8 针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2021-04-27 18:12:10 5626

5626

在FPGA中配置PLL的步骤及使用方法

2021-05-28 10:01:17 21

21 基于FPGA的小波滤波抑制复位噪声方法

2021-07-01 14:42:09 24

24 。 FPGA器件配置方式分三大类:主动配置、被动配置和JTAG配置。 主动配置:由FPGA器件引导配置操作过程。 被动配置:由计算机或控制器控制配置过程。上电后,控制器件或主控器把存储在外部存储器中的数据送入FPGA器件内,配置完成之后将对器件I/O和寄存器进行初始化。初始化完成后,进入用户

2021-09-06 09:41:56 7483

7483 在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序(开关电源技术与设计潘永雄.pdf)-在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序,适合感兴趣的人学习参考

2021-09-16 11:37:05 66

66 方法:1.生成hex文件,方法如下图:2.生成的hex文件后缀为.hexout,改为.hex,然后把BOOT0插针短路,按键复位单片机,单片机串口连接电脑;3.使用STM32CubeProgrammer软件固化FPGA程序,方法如图:4.下载成功后,去掉BOOT0跳线帽,按键复位单片机

2021-11-18 20:06:02 18

18 项目场景:STM32下载后无法自动复位,需手动复位下载程序时,勾选reset and run后仍不可自动复位问题描述:STM32下载后无法自动复位,需手动复位下载程序时,勾选reset and run后仍不可自动复位原因分析:未知解决方案:取消勾选Enable即解决问题。...

2022-01-17 12:36:51 11

11 AGM FPGA 在配置成功时,PLL 已经完成锁定,lock 信号已经变高;如果原设计中用 lock 信

号输出实现系统 reset 的复位功能,就不能正确完成上电复位;同时,为了保证 PLL

2022-08-23 14:21:47 0

0 电子发烧友网站提供《EF3 PLL动态配置.pdf》资料免费下载

2022-09-27 10:26:04 1

1 电子发烧友网站提供《ELF2 FPGA PLL动态配置.pdf》资料免费下载

2022-09-26 15:13:06 1

1 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 4846

4846 FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 1882

1882 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 6199

6199

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。

2023-05-22 14:21:08 1907

1907

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 4510

4510

应用中得到广泛采用。汽车场景中摄像头系统的快速启动时间要求就是很好的一个例子——车辆启动后后视图像在仪表板显示屏上的显示速度是最为突出的设计挑战。 上电后,FPGA立即加载存储于NOR器件中的配置比特流。传输完成后,FPGA转换为活动(已配置)状态。FP

2023-08-15 13:55:02 1338

1338

电子发烧友网站提供《使用STARTUPE3对并行NOR闪存进行配置后访问的UltraScale FPGA应用说明.pdf》资料免费下载

2023-09-14 15:18:20 8

8 pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子技术中广泛应用的一种电路,它的作用是将一个特定频率的输入信号转换为固定频率的输出信号。PLL锁相环的三种配置模式分别为

2023-10-13 17:39:48 5281

5281 FPGA(Field-Programmable Gate Array,现场可编程门阵列)中的复位操作是设计过程中不可或缺的一环,它负责将电路恢复到初始状态,以确保系统的正确启动和稳定运行。在FPGA设计中,复位方式主要分为同步复位和异步复位两种。以下是对这两种复位方式的详细探讨。

2024-07-17 11:12:21 3320

3320 电子发烧友网站提供《使用离散逻辑的可配置定时复位.pdf》资料免费下载

2024-09-03 10:16:26 1

1 电子发烧友网站提供《音频设备的PLL和时钟配置应用说明.pdf》资料免费下载

2024-09-14 10:38:29 0

0 每次在系统掉电之后,之前载入的程序将会丢失,系统上电后需要重新配置。设计者为了弥补这项缺陷,在FPGA芯片的旁边都会设置一个flash(掉电不丢失)。

2024-10-24 18:13:41 1988

1988

在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何

2024-11-16 10:18:13 1804

1804

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS和DDR相对于core部分都是

2025-06-07 16:18:40 1205

1205

电子发烧友App

电子发烧友App

评论