同步复位和异步复位到底孰优孰劣呢?

同步复位和异步复位是两种不同的复位方式,它们各自有优势和劣势,下面将详细介绍这两种复位方式。

同步复位是指在时钟的边沿(上升沿或下降沿)发生时对系统进行复位。这种复位方式具有精确控制的特点,因为复位信号与时钟信号同步工作,所以可以保证复位信号与时钟信号的相位精确匹配。同步复位的优势主要有以下几点:

1. 精确控制:同步复位可以确保复位信号和时钟信号的相位一致,避免由于信号传输延迟而导致的问题。这对于一些需要精确同步的应用场景非常重要。

2. 减少冲突:同步复位可以以同步的方式与其他信号进行控制,减少信号冲突的可能性。这有助于提高系统的可靠性和稳定性。

3. 避免时序问题:同步复位可以避免由于时序问题(如时钟闪烁、时钟脉冲不稳定等)而导致系统的复位不准确或延迟。

但是同步复位也存在一些劣势:

1. 依赖于时钟:同步复位需要依赖于时钟信号的存在,如果时钟信号不稳定或中断,可能导致复位信号无法正常工作。

2. 增加设计复杂性:同步复位需要对时钟边沿进行检测和触发复位操作,这增加了设计的复杂性和工作量。

异步复位是指复位信号与时钟信号无关,可以独立触发。由于异步复位不依赖于时钟信号,所以其触发时间和时钟信号无关,可以在任意时刻触发复位。异步复位的优势包括:

1. 独立触发:异步复位可以在不依赖时钟信号的情况下触发,可以在任意时刻进行复位操作。

2. 灵活性:异步复位对时钟的要求较低,可以适用于不同的时钟频率和时钟类型。

3. 可靠性:由于不依赖于时钟信号,异步复位可以在时钟信号中断或不稳定的情况下正常工作,提高了系统的可靠性。

但是异步复位也存在一些劣势:

1. 引发时序问题:由于异步复位与时钟信号无关,可能引发时序问题。比如在异步复位信号发生时,可能会导致时序逻辑的不稳定或错误操作。

2. 信号冲突:由于异步复位可以在任意时刻触发,可能会与其他信号产生冲突,导致系统功能异常。

基于以上分析,同步复位和异步复位各有优势和劣势,具体使用哪种复位方式取决于具体的应用场景和设计需求。在一些对精确同步要求高、不依赖时钟的应用场景中,同步复位是更好的选择;而在一些对时钟要求较低、需要独立触发的应用场景中,异步复位更适合使用。因此,设计者需要根据具体要求和设计限制选择适合的复位方式。

-

同步复位

+关注

关注

0文章

28浏览量

10988 -

异步复位

+关注

关注

0文章

48浏览量

13704

发布评论请先 登录

SGM823A:集复位、看门狗和手动复位功能于一体的微处理器监控电路

SGM823:集成复位、看门狗和手动复位功能的微处理器监控电路

深入剖析SGM800:低功耗微处理器复位电路的卓越之选

SGM802:低功耗微处理器复位电路的理想之选

SGM804:低功耗微处理器复位电路的理想之选

探索DS1811:经济高效的电源监控复位芯片

MAX6443–MAX6452:具备长手动复位设置周期的微处理器复位电路

CW32在不同复位方式对应的复位范围

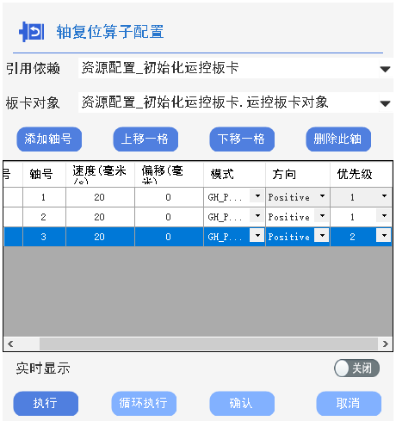

GraniStudio:轴复位例程

GraniStudio零代码平台轴复位算子支持多少个轴同时复位,有哪些回零模式?

服务与数据的双螺旋:从SOME/IP到DDS看汽车电子架构的进化之路

自研vs供应商,智能驾驶双模式孰优孰劣?

同步复位和异步复位到底孰优孰劣呢?

同步复位和异步复位到底孰优孰劣呢?

评论