对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 9365

9365 大家好,博主最近有事忙了几天,没有更新,今天正式回来了。那么又到了每日学习的时间了,今天咱们来聊一聊 简谈FPGA的上电复位,欢迎大家一起交流学习。 在基于verilog的FPGA设计中,我们常常

2018-06-18 19:24:11 21146

21146

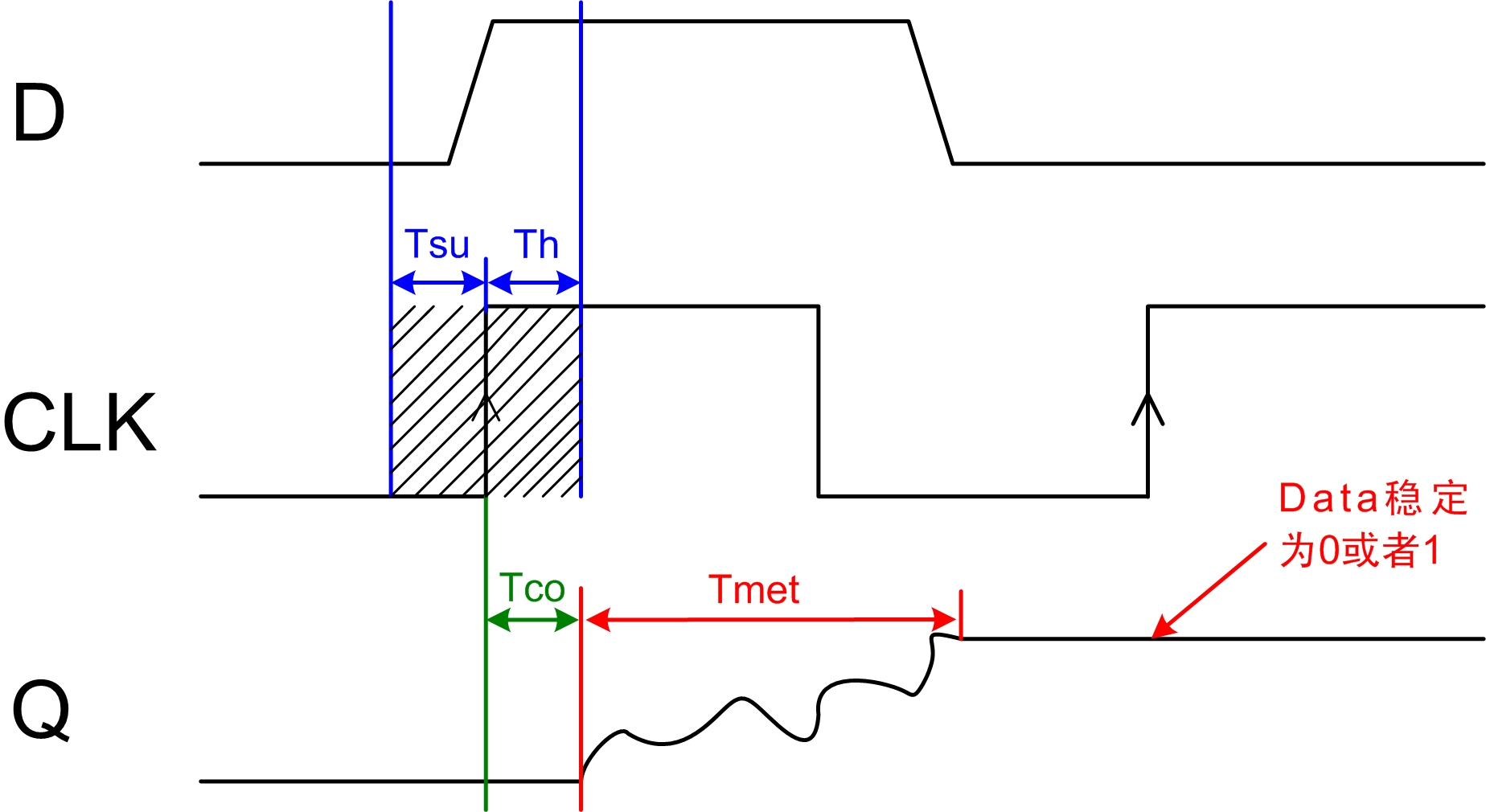

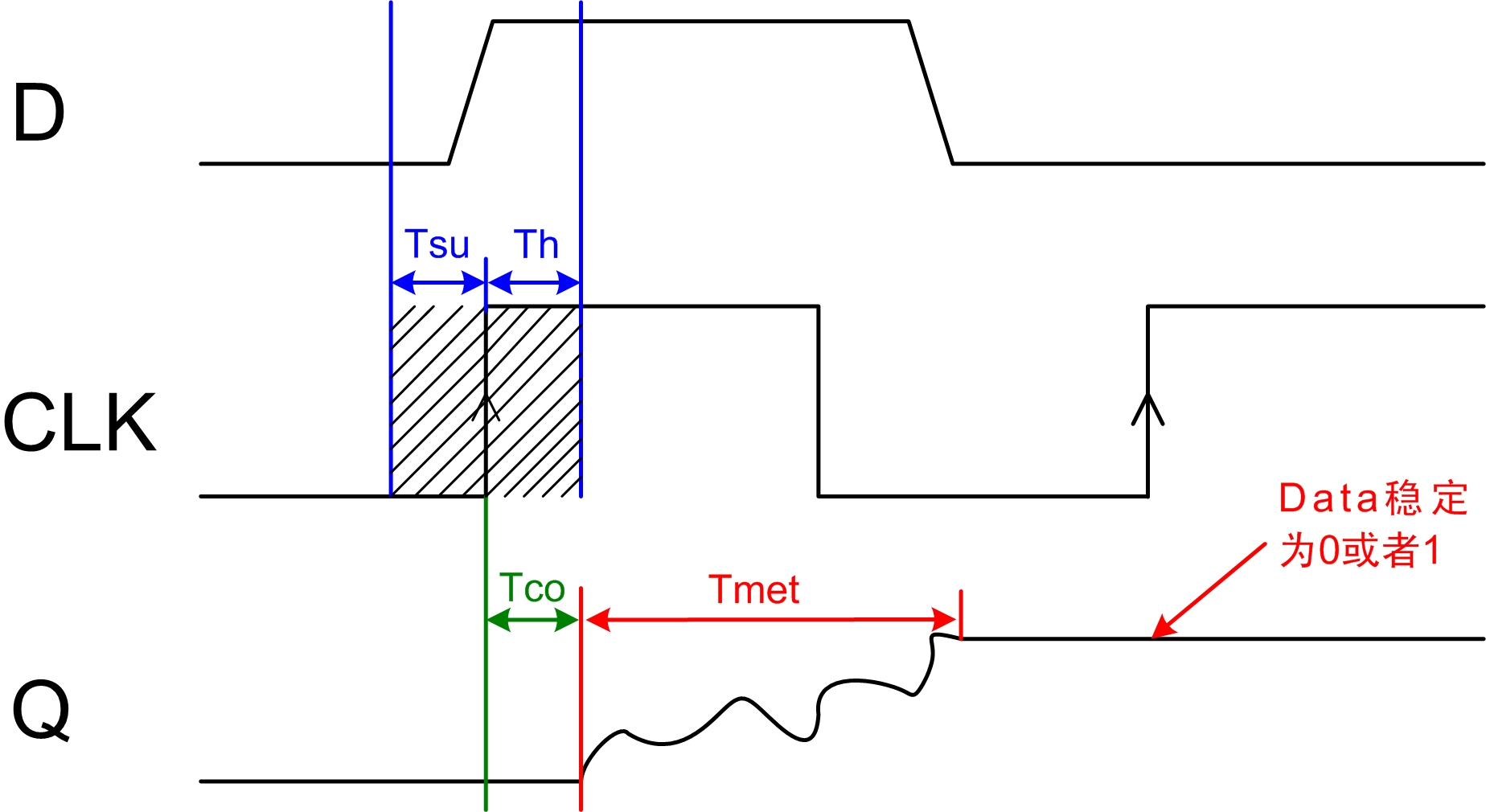

在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

2020-06-26 16:37:00 1776

1776

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 2079

2079

只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

2020-09-30 17:08:43 4345

4345

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。 在本篇文章中,主要

2020-11-21 11:13:01 4997

4997

作者:NingHeChuan Get Smart About Reset: Think Local, Not Global。 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间

2020-12-25 12:08:10 3230

3230

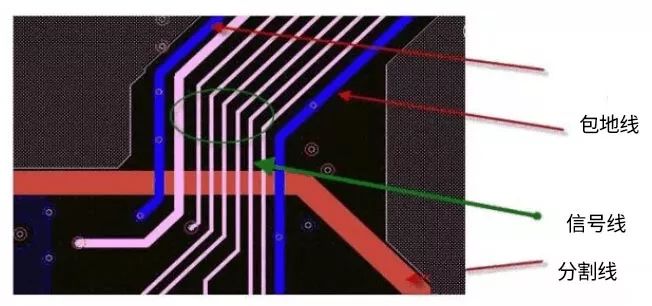

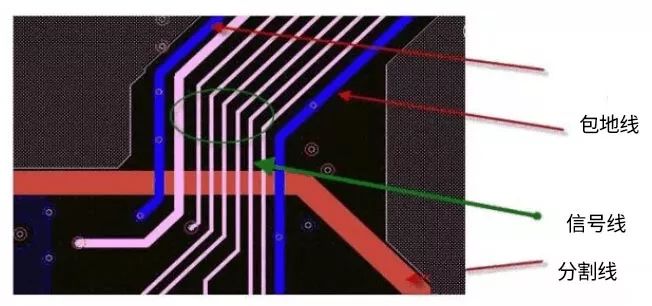

当高速信号发生跨沟现象时,整个电流的环路面积将增加,通常系统的EMC辐射也将增加。同时传输线的特征阻抗也将发生变化(如下图2所示为信号线阻抗变化曲线),信号遇到传输线特征阻抗突变点时将发生发射、振铃等信号完整性问题。

2022-09-15 11:05:12 1527

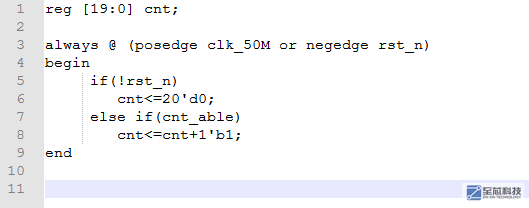

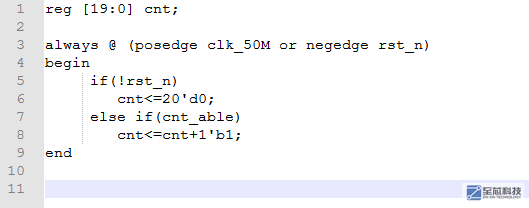

1527 在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 3405

3405

在FPGA设计中,当复位整个系统或功能模块时,需要将先关寄存器被清零或者赋初值,以保证整个系统或功能运行正常。在大部分的设计中,我们经常用“同步复位”或“异步复位”直接将所有的寄存器全部复位,这部分可能大家都习以为常。但实际上,是否需要每个寄存器都进行复位呢?这是一个值得探讨的问题。

2023-05-14 14:49:19 3131

3131

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2023-06-21 09:59:15 2281

2281

对于从FPGA外部进来的信号,我们通常采用“异步复位同步释放的策略”,具体电路如下图所示。

2023-07-20 09:04:21 2786

2786

复位信号几乎是除了时钟信号外最常用的信号了,几乎所有数字系统在上电的时候都会进行复位,这样才能保持设计者确定该系统的系统模式的状态,以便于更好的进行电子设计,并且在任意时刻,确保使用者总能对电路系统进行复位,使电路从初始的状态开始工作。

2023-07-27 09:48:30 12093

12093

假设现在FPGA内部有两个高速信号完全相同,有一个很小的相位差,该如何获得一个如c信号(拓宽也行)的输出信号?直接相与或者其他逻辑操作是不是lut无法满足这么高的精度,如果不行,有其他什么办法吗?

2019-10-15 11:12:31

时获取可重复结果。在模块级应用实现属性,可令代码简单并具可扩展性,该属性可传播该模块中声明的所有信号。良好的时钟管理和时钟分配方法至关重要。尽可能减少独立主时钟数量。将时钟元件放在设计层次结构的顶层

2017-02-10 17:10:32

布线带来很大的困难,甚至走不通,或者是即便是布线走通了,也有可能由于外部的延时过大而不满足时序方面的要求。所以在管脚分配前对FPGA 工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚

2012-08-11 10:27:54

在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器

2020-10-22 11:42:16

就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们也

2019-04-12 06:35:31

线将会是一个和时钟一样多扇出的网络,如此多的扇出,时钟信号是采用全局时钟网络的,那么复位如何处理?有人提出用全局时钟网络来传递复位信号,但是在FPGA设计中,这种方法还是有其弊端。一是无法解决复位结束

2019-05-17 08:00:00

就没有复位过程;当然了,如果上电复位延时过长,那么对系统性能甚至用户体验都会有不通程度的影响,因此,设计者在实际电路中必须对此做好考量,保证复位延时时间的长短恰到好处。关于FPGA器件的复位电路,我们

2015-04-10 13:59:23

FPGA的高速接口应用注意事项主要包括以下几个方面:

信号完整性与电磁兼容性(EMC) :

在设计FPGA高速接口时,必须充分考虑信号完整性和电磁兼容性。这要求合理的PCB布局、走线策略和屏蔽技术

2024-05-27 16:02:50

方面的要求。所以在管脚分配前对 FPGA工作的环境要相当的熟悉,要对其中的信号来自哪里去向何方非常的清楚,这就按照连线最短的原则将对应的信号分配到与外部器件连线最近的 BANK 中。2、 掌握

2024-01-10 22:40:14

。 FPGA 内部 BANK 的分配情况和每个 BANK 中所支持的 I/O标准。根据 FPGA中内部 BANK 的分配的情况,同时结合图 1 中信号的流向也就可以大体固定FPGA在单板中的方向,同时按照

2017-03-25 18:46:25

下面对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用

2021-06-30 07:00:00

FPGA设计中有多个时钟域时如何处理?跨时钟域的基本设计方法是:(1)对于单个信号,使用双D触发器在不同时钟域间同步。来源于时钟域1的信号对于时钟域2来说是一个异步信号。异步信号进入时钟域2后,首先

2012-02-24 15:47:57

分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,quartus2中引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard( 3.3-V

2019-04-03 07:00:00

亚稳态概述01 亚稳态发生原因在 FPGA 系统中,如果数据传输中不满足触发器的 Tsu 和 Th 不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足

2020-10-19 10:03:17

在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应如何分配?

2009-09-06 08:39:35

`高速PCB中的信号回流及跨分割这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便作图,把层间距放大。 IC1为信号输出端,IC2为信号输入端(为简化PCB模型

2013-10-24 11:12:40

变化速率)、dV(干扰源的摆幅)和R(干扰源负载)都是指干扰源的参数(如果是容性负载的话,dI/dt是与T10%-90%的平方成反比的。)。从式中可以看出,低速的信号未必比高速信号的串扰小。也就是我们说

2018-11-22 15:58:42

高速PCB中的地回流和电源回流以及跨分割问题分析

2021-04-25 07:47:31

在 PCB 设计过程中,由于平面的分割,可能会导致信号参考平面不连续,对于低低频信号,可能没什么关系,而在高频数字系统中,高频信号以参考平面作返回路径,即回流路径,如果参考ᒣ面不连续,信号跨分割

2016-10-09 13:10:37

PCB设计中跨分割的处理高速信号布线技巧

2021-02-19 06:27:15

同步单元的起始状态或者将要返回的状态是一个已知状态(罗辑‘1’或者‘0’)就显得非常重要。在程序中,往往都在端口定义中使用同一个rst_n信号,通常的同步电路通常是由两种复位方式来进行电路的复位,即

2015-06-07 20:39:43

引脚输入的时钟信号,在FPGA内部可以很容易的连接到全局时钟网络上。所谓的全局时钟网络,是FPGA内部专门用于走一些有高扇出、低时延要求的信号,这样的资源相对有限,但是非常实用。FPGA的时钟和复位

2016-08-08 17:31:40

PlanAead引脚分配这个例程的顶层源码里有3个接口,即:input ext_clk_25m, //外部输入25MHz时钟信号input ext_rst_n,//外部输入复位信号,低电平有效output reg

2018-02-27 21:50:07

本期讲解的是PCB设计中处理关键信号的注意事项。一、关键信号的识别关键信号通常包括以下信号:时钟信号(*CLK*),复位信号(*rest*,*rst*), JTAG信号(*TCK*)二、处理关键信号

2017-11-01 17:06:26

FPGA 在单板中的方向,同时按照就近的原则将相关的信号分配到相关的 BANK 中,这样的方法可以完成一般信号的分配。3、 掌握所选 FPGA 每个 BANK 所支持的 I/O 标准。从图 2 中可以看出

2015-01-06 17:38:22

芯片输出的数据在 60MHz 的时钟上升沿变化,而 FPGA 内部需要使用 100MHz 的时钟来处理 ADC 采集到的数据(多 bit)。在这种类似的场景中,我们便可以使用异步双口 RAM 来做跨

2020-09-22 10:24:55

跨时钟域处理是FPGA设计中经常遇到的问题,而如何处理好跨时钟域间的数据,可以说是每个FPGA初学者的必修课。如果是还是在校的学生,跨时钟域处理也是面试中经常常被问到的一个问题。在本篇文章中,主要

2021-07-29 06:19:11

同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移和抖动)方面,还有那些组成时钟分配网络的组件。

2019-10-16 07:11:33

这三类约束文件分开写在三个xdc/sdc文件中。 第一类是物理约束,它主要对设计顶层的输入输出引脚的分配约束、电平标准的约束,如下图所示:在quartus环境下,对pcie_rstn

2022-11-15 14:47:59

本文阐述了用于FPGA的可优化时钟分配网络功耗与面积的时钟布线结构模型。并在时钟分配网络中引入数字延迟锁相环减少时钟偏差,探讨了FPGA时钟网络中锁相环的实现方案。

2010-08-06 16:08:45 12

12 发射应用中多个高速、复用DAC的同步

摘要:该篇应用笔记给出了多个具有多路输入或集成内插滤波器的高速复用数模转换器(DAC)

2008-09-11 21:02:16 1292

1292

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-04-24 16:05:19 2001

2001

摘要:ANSI EIA/TIA-644标准定义的低电压差分信号(LVDS)非常适合包括时钟分配、点对点以及多点之间的信号传输。本文描述了使用LVDS将高速通讯信号分配到多个目的端的方法。

2009-05-01 11:14:27 1918

1918

高速PCB中的信号回流及跨分割

这里简单构造了一个“场景”,结合下图介绍一下地回流和电源回流以及一些跨分割问题。为方便

2009-11-17 08:56:03 1188

1188 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证

2011-01-25 18:19:39 163

163 VGA分配器将来自一个信号源的视频信号分配成两个或多个信号。高分辨率视频分配放大器的一个常见应用就是,在接收来自一个计算机视频端口的信号后将其放大,并在保持原有信号质量的情况下将其分配到两个或多个高分辨率数据显示设备

2011-02-21 10:55:32 12631

12631

TCAM在高速路由查找中的应用及其FPGA实现,TCAM在高速路由查找中的应用及其FPGA实现

2015-11-04 16:32:39 15

15 跨阻放大器在微弱光电信号检测中的应用,设计过程非常具体,值得参考

2016-03-24 16:12:26 0

0 现在的FPGA向引脚分配信号的任务曾经很简单,现在也变得相当繁复。

2016-07-27 20:24:00 7371

7371 好消息是,在绝大多数设计中(白皮书说是超过99.99%?应该是老外写文档的习惯吧),复位信号的时序是无关紧要的——通常情况下,大部分电路都能够正常工作。

2017-02-11 11:07:33 575

575

在FPGA设计中,我们往往习惯在HDL文件的端口声明中加入一个reset信号,却忽略了它所带来的资源消耗。仔细分析一下,竟会有如此之多的影响:

2017-02-11 11:09:11 1263

1263 在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 1232

1232

现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2017-05-18 10:51:54 31049

31049

在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 6340

6340

在高速电路中经常会遇到跨分割设计,在2017年的时候也写过一篇跨分割设计的文章。

今天给大家分享一篇跨分割设计对信号的影响。

2018-01-23 15:49:53 8663

8663

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 2563

2563 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 7577

7577 在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

2018-08-07 09:17:18 12506

12506 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 12709

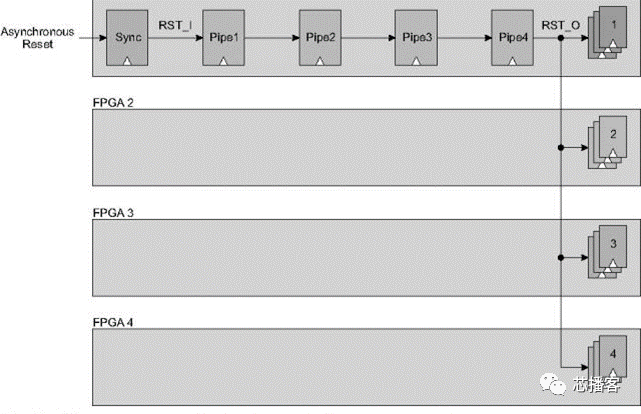

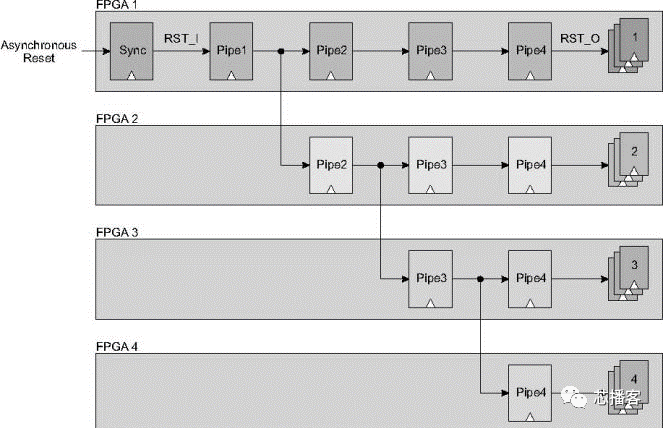

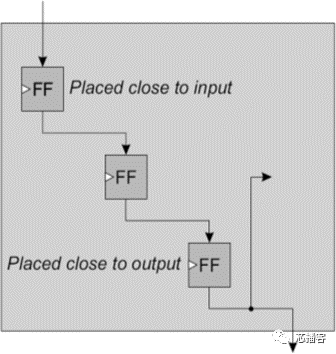

12709 FPGA设计中,层次结构设计和复位策略影响着FPGA的时序。在高速设计时,合理的层次结构设计与正确的复位策略可以优化时序,提高运行频率。

2019-02-15 15:15:53 1270

1270 在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

2019-03-07 14:52:24 7372

7372 在遵循管脚特定的规则和约束的同时,可以在 PCB 上的多个 FPGA 之间自动优化信号管脚分配。减少布线层数,最大限度地减少 PCB 上的交叉数量并缩短总体走线长度,以及减少信号完整性问题,从而提高完成率并缩短 FPGA 的布线时间。

2019-05-14 06:23:00 4137

4137

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟域的数量急剧增加。通常不止数百个,而是超过一千个时钟域。

2019-08-19 14:52:58 3895

3895 信号销任务之间可以自动优化PCB上的多个fpga同时尊重pin-specific规则和约束。减少路由层,减少跨界车和整体跟踪PCB上的长度,并减少信号完整性问题较高的毕业率和更短的FPGA路线时间。

2019-10-14 07:06:00 3662

3662 复位信号设计的原则是尽量不包含不需要的复位信号,如果需要,考虑使用局部复位和同步复位。

2019-10-27 10:09:53 2273

2273

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 3320

3320

DFF 都有异步复位端口,因此采用异步复位可以节约资源。 ⑵设计相对简单。 ⑶异步复位信号识别方便,而且可以很方便地使用 fpga 的全局复位端口。 缺点:⑴在复位信号释放时容易出现问题,亚稳态。 ⑵复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原

2020-10-30 12:17:55 951

951 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 26

26 高速计数器复位标志为ON的状态下,Z相信号及复位输入由OFF→ON时,将高速计数器当前值复位。此外,由于复位标志为ON,1周期1次,仅可在共通处理中判别,因此在梯形图程序内发生OFF→ON的情况下,从下一周期开始Z相信号转为有效。

2021-03-23 14:43:42 9105

9105 说到异步时钟域的信号处理,想必是一个FPGA设计中很关键的技术,也是令很多工程师对FPGA望 而却步的原因。但是异步信号的处理真的有那么神秘吗?那么就让特权同学和你一起慢慢解开这些所谓的难点

2021-11-01 16:24:39 11

11 对于硬件设计来说,复位电路是必不可少的一部分,为了确保微机系统中电路稳定可靠工作,复位电路的第一功能是上电复位。在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态

2021-11-06 09:20:57 20

20 在这些情况下,复位信号的变化与FGPA芯片内部信号相比看起来是及其缓慢的,例如,复位按钮产生的复位信号的周期至少是在毫秒级别的,而我们FPGA内部信号往往是纳米或者微秒级别的。

2022-05-06 10:48:45 3256

3256 一般在空白区域的敷铜绝大部分情况是接地。只是在高速信号线旁敷铜时要注意敷铜与信号线的距离,因为所敷的铜会降低一点走线的特性阻抗。也要注意不要影响到它层的特性阻抗,例如在dual strip line的结构时。

2022-09-16 09:05:11 2751

2751 跨分割,对于低速信号可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。

2023-02-21 13:44:36 2084

2084 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 4846

4846 本应用笔记讨论了EIA/TIA-644低压差分信号(LVDS)标准在3G移动通信中的应用。LVDS具有低功耗和低辐射特性,非常适合WCDMA、EDGE和cdma2000®基站中的高速时钟和信号分配。提供MAX9205串行器、MAX9206解串器、MAX9150多端口中继器和MAX9152交叉点开关。

2023-03-29 11:14:33 1872

1872

FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 1882

1882 。 下面将讨论FPGA/CPLD的复位电路设计。 2、分类及不同复位设计的影响 根据电路设计,复位可分为异步复位和同步复位。 对于异步复位,电路对复位信号是电平敏感的,如果复位信号受到干扰,如出现短暂的脉冲跳变,电路就会部分或全部被

2023-04-06 16:45:02 2170

2170 现在的FPGA正变得越来越复杂,向引脚分配信号的任务曾经很简单,现在也变得相当繁复。下面这些用于向多用途引脚指配信号的指导方针有助于设计师根据最多到最少的约束信号指配原则提前考虑信号指配,并减少反复的次数。

2023-05-04 17:38:53 1487

1487 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 6199

6199

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。

2023-05-22 14:21:08 1907

1907

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 4510

4510

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 3484

3484

在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应如何分配? 在高速PCB设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应该经过合理分配。接地

2023-11-24 14:38:21 1850

1850 的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。 跨分割现象示意图 跨分割,对于低速信号可能没有什么关系,但是在高速数字信号系统中,高速信号是以参考平面作为返回路径,就是回流路径。当参考平面不完整的时

2023-12-04 10:26:34 1525

1525

FPGA(Field-Programmable Gate Array,现场可编程门阵列)中的复位操作是设计过程中不可或缺的一环,它负责将电路恢复到初始状态,以确保系统的正确启动和稳定运行。在FPGA设计中,复位方式主要分为同步复位和异步复位两种。以下是对这两种复位方式的详细探讨。

2024-07-17 11:12:21 3320

3320 都有异步复位端口,因此采用异步复位可以节约资源。 ⑵设计相对简单。 ⑶异步复位信号识别方便,而且可以很方便地使用fpga的全局复位端口。 缺点:⑴在复位信号释放时容易出现问题,亚稳态。 ⑵复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原

2024-11-15 11:13:55 911

911

在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何

2024-11-16 10:18:13 1804

1804

优势之一是其并行处理能力。与传统的CPU或GPU相比,FPGA可以同时执行多个操作,这在图像处理中尤为重要,因为图像处理通常涉及大量的并行数据流和复杂的算法。例如,在进行图像滤波或边缘检测时,FPGA可以同时处理多个像素,从而显著提高处理速度。 2

2024-12-02 10:01:34 2508

2508 今天讲一下高速信号线跨沟对眼图抖动的影响。Chrent高速信号跨沟及信号回流的基本概念下图所示为一个信号流向及其回流示意图。基于基尔霍夫定律,电流是闭环的,也就是说任意一个电路的节点只要有电流

2025-06-04 17:32:44 721

721

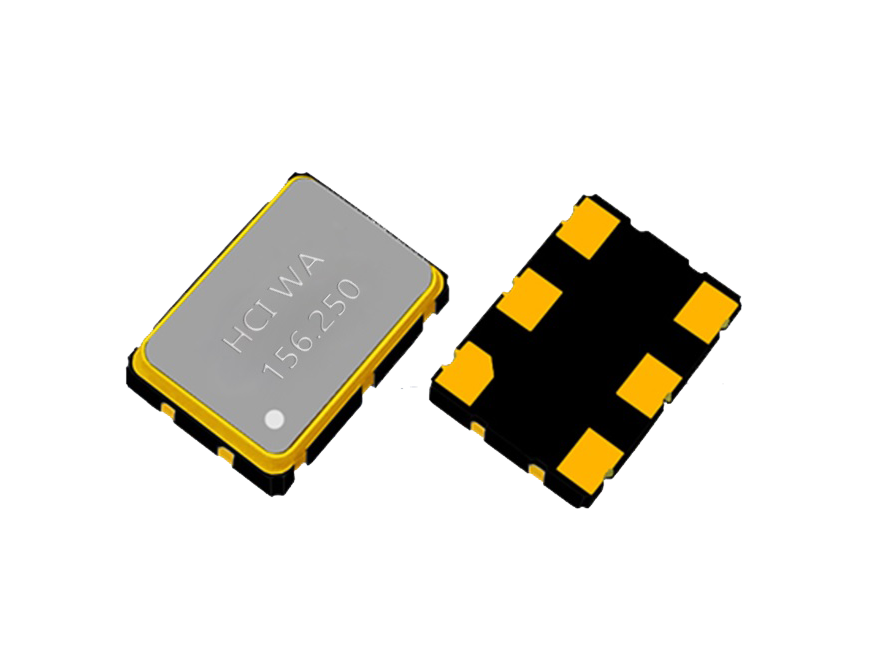

差分晶振在高速 FPGA 设计中具有非常重要的应用,尤其是在对时钟精度、抗干扰能力、信号完整性要求高的系统中

2025-07-11 14:24:48 689

689

电子发烧友App

电子发烧友App

评论