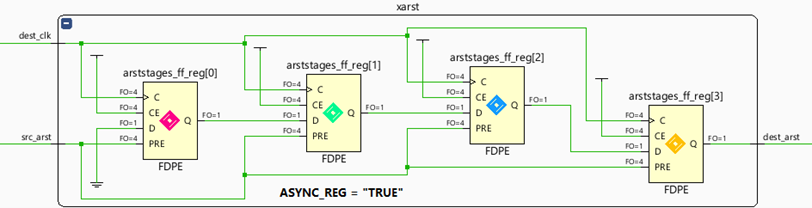

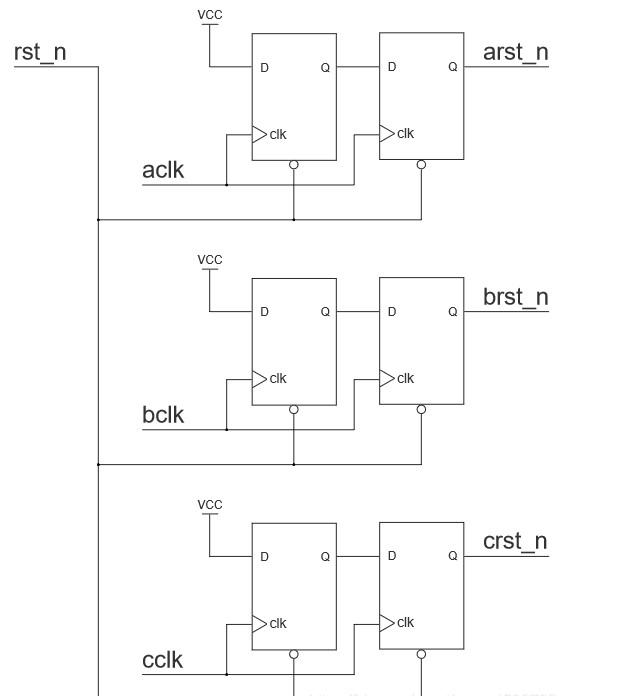

对于从FPGA外部进来的信号,我们通常采用“异步复位同步释放的策略”,具体电路如下图所示。图中src_arst是输入异步复位信号,dest_arst是同步释放的异步复位信号,其后负载为需要异步复位的触发器。

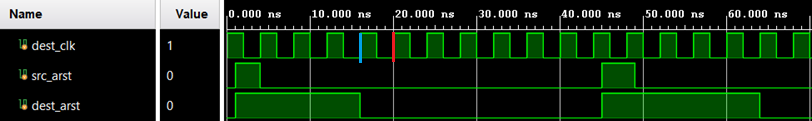

从时序关系的角度来看,结合如下仿真波形,异步复位信号在蓝色标记的时钟上升沿被释放,所有触发器将在红色边沿开始输出D端口数据。

问题是如果后续触发器公众在不同的时钟频率下,这种方式是否仍能确保所有触发器的异步复位信号在同一个时钟上升沿被释放?为便于说明,我们假定设计中有两个时钟,分别为100MHz和200MHz,均有同一个MMCM/PLL生成,即二者是同步时钟(同相不同频)。

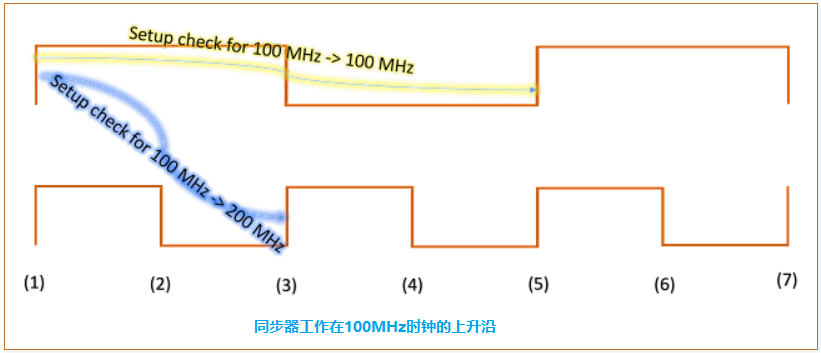

第一种情况:同步器工作在100MHz时钟的上升沿

在这种情况下,假定异步复位在标记(1)被释放,那么200M时钟域下的触发器将在标记(3)开始输出D端数据,而100M时钟域下的触发器则要在标记(5)开始输出D端数据,显然,两者并没有在同一个时钟沿下开始工作。

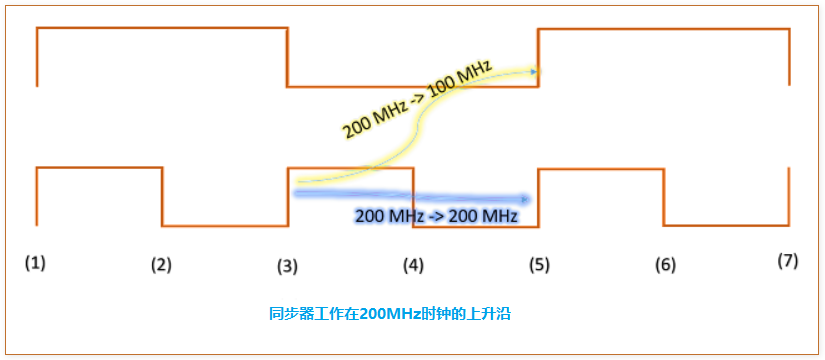

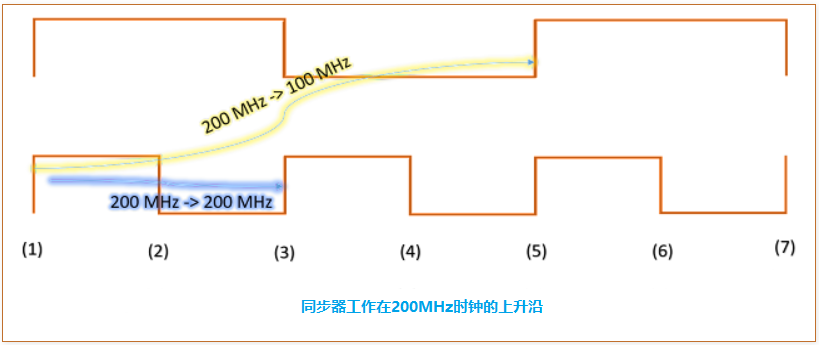

第二种情况:同步器工作在200MHz时钟的上升沿

在这种情况下,如果异步复位是在标记(3)释放,那么100M时钟域下的触发器和200M时钟域下的触发器都将在标记(5)结束复位,开始输出D端口数据。

但是,如果复位是在标记(1)释放,如下图所示,100M时钟域下的触发器将在标记(5)输出D端口数据,而200M时钟域下的触发器将在标记(3)输出D端口数据。

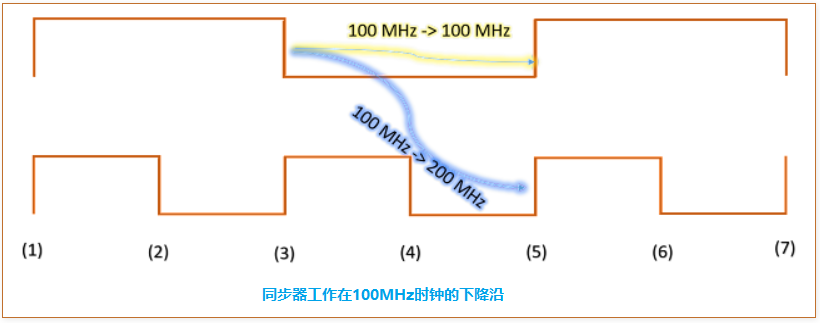

第三种情况:同步器工作在100MHz时钟的下降沿

在这种情况下,同步器工作在100MHz时钟的下降沿,但后续触发器仍工作在时钟的上升沿。如下图所示。异步复位在标记(3)释放,那么100M时钟域下的触发器将在标记(5)开始输出D端口数据,200M时钟域下的触发器也在此刻输出D端口数据,故两者可以在同一个时刻开始释放复位正常工作。

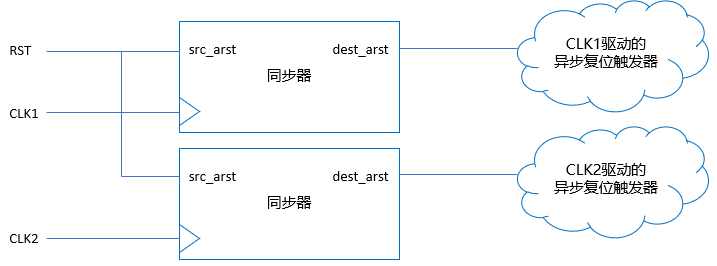

如果两个时钟是异步时钟,都要使用外部提供的同一个复位信号,这时无法做到这两个时钟域下的触发器实现复位信号同步释放。这是因为这两个时钟之间没有明确的相位关系,这就造成同步器引发的延迟差是不确定的。这种情况下,我们需要对每个时钟域添加同步器,生成各自时钟域下的复位信号,如下图所示。

审核编辑:刘清

-

FPGA

+关注

关注

1664文章

22519浏览量

639775 -

pll

+关注

关注

6文章

991浏览量

138426 -

时钟

+关注

关注

11文章

2000浏览量

135320 -

触发器

+关注

关注

14文章

2065浏览量

63585 -

同步器

+关注

关注

1文章

117浏览量

15712 -

异步复位

+关注

关注

0文章

48浏览量

13711 -

PLL电路

+关注

关注

0文章

94浏览量

7148

原文标题:异步复位同步释放有多个时钟域时如何处理

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略

评论