点击上方蓝字关注我们

系统的复位对于系统稳定工作至关重要,最佳的复位方式为:异步复位,同步释放。以下是转载博客,原文标题及链接如下:复位最佳方式:异步复位,同步释放

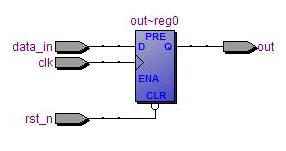

异步复位;

异步:

always@(posedgeclkornegedgerst_n)

if(!rst_n)

(优点:占用较少逻辑单元

缺点:可能会产生竞争冒险)

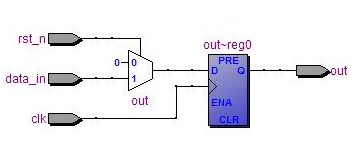

同步:always @(posege clk or posedge rst_n)

If(!rst_n)

(优点:可以尽量点少竞争冒险的可能

缺点:会占用更多的逻辑单元)

Altera 最佳解决办法:异步复位,同步释放

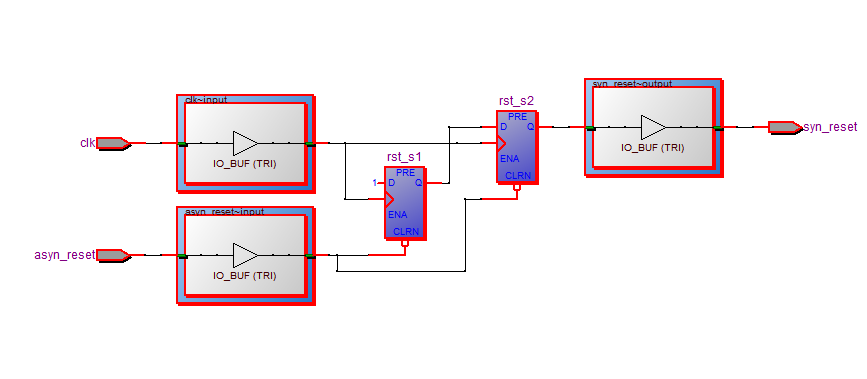

//异步复位 同步释放rtl视图

原理:

所谓异步复位和同步释放,是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除(释放)则与clk相关,即同步的。

下面说明一下如何实现异步复位和同步释放的。

异步复位:显而易见,rst_async_n异步复位后,rst_sync_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号rst_async_n撤除时,由于双缓冲电路的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除。

假设rst_async_n撤除时发生在clk上升沿,如果不加此电路则可能发生亚稳态事件(在始终上升沿附近rst置1,这时候建立时间还不够长,数据可能还未打入寄存器,导致输出不确定)。但是加上此电路以后,假设第一级D触发器clk上升沿时rst_async_n正好撤除,则D触发器1输出高电平“1”,此时第二级触发器也会更新输出,但是输出值为前一级触发器次clk来之前时的Q1输出状态。显然Q1之前为低电平,顾第二级触发器输出保持复位低电平,直到下一个clk来之后,才随着变为高电平。即同步释放。

代码实现:(Altera 官方资料)

module reset_best(clk,asyn_reset,syn_reset);

input clk;

input asyn_reset;

output syn_reset;

reg rst_s1;

reg rst_s2;

always @( posedge clk ,posedge asyn_reset)

begin

if(asyn_reset)

begin

rst_s1<=1'b0;

rst_s2<=1'b0;

end

else

begin

rst_s1<=1'b1;

rst_s2<=rst_s1;

end

end

assign syn_reset=rst_s2;

endmodule

有你想看的精彩 至芯科技FPGA就业培训班——助你步入成功之路、9月23号北京中心开课、欢迎咨询! FPGA学习:精简指令集RISC_CPU 至芯FPGA初级课程之 FIFO

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-异步复位,同步释放

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22508浏览量

639504

原文标题:FPGA学习-异步复位,同步释放

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

低功耗片外扩展芯片Netsol异步sram

LX2080释放复位瞬间启动电流过大,有什么办法让CPU核缓启动或者8个核分时依次启动吗?

单片机中的串口通讯串行同步通信与串行异步通信

高速数据存取同步SRAM与异步SRAM的区别

基于FPGA的高效内存到串行数据传输模块设计

为什么同步电机多做发电机而异步电机多做电动机?

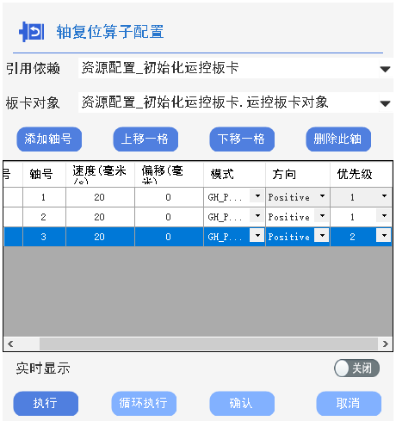

GraniStudio:轴复位例程

从底层解读labview的TDMS高级异步写入的工作原理

FPGA在机器学习中的具体应用

GraniStudio零代码平台轴复位算子支持多少个轴同时复位,有哪些回零模式?

AMD FPGA异步模式与同步模式的对比

第二十四章 通用同步异步收发器(USART)

FPGA学习-异步复位,同步释放

FPGA学习-异步复位,同步释放

评论