复位消抖之后的下一件事,异步复位同步撤离。这句话什么意思呢?

对于使用异步复位的系统,低电平复位系统时复位信号是允许不与工作时钟对齐的即纯纯异步复位;

但是在复位撤离时,需要与工作时钟对齐,即满足removal time要求(在时钟有效沿来临之后,异步复位信号需要继续保持有效的最短时间),或者说复位的撤离行为是受到时钟控制的。

既然都已经是异步复位了,为何还要多此一举呢?

1.对于复位这个操作行为而言,纯异步处理是完全可以的,因为所有的元器件都会最终回到初始值。当然了,这里指的是整体复位或者说带保护的局部复位。你别管这些寄存器谁先复位谁后复位谁出现亚稳态了,只要不是着火了最后都会回到复位值。就像电视剧里说的“反正早晚都是没,早没晚没又有什么区别呢”。所以异步复位出电路是没有任何问题的。

2.但是对于复位撤销这个行为就不一样了。一旦复位撤销了各个元器件就会开始工作了,但是复位信号如果是纯异步的打到某个寄存器接口上的时候可能就撞到亚稳态窗口上了(不满足removal time),亚稳态就会在电路里开始蔓延捣乱,出现什么情况可就难说了。所以复位撤离这个事必须得是受到时钟控制的,不能是纯异步电路。

这里有一点要注意哈,同步撤离这个操作解决的是异步复位可能的亚稳态问题,并不是说能够保证所有的寄存器在同一时间收到复位撤离的操作。

这个事就类似与信号打3拍同步一样,咱们先解决亚稳态问题,再处理信号传的对不对的问题。通过异步复位同步撤离先确保没有亚稳态,再处理寄存器不能在同一拍接收到复位撤销导致错误的问题。

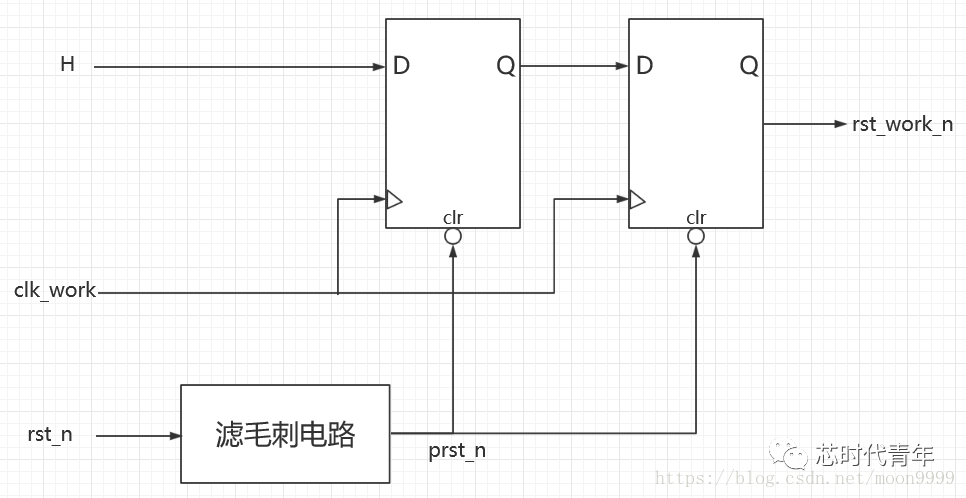

如何做到异步复位同步撤离呢?请看下面这个电路:

rst_n经过滤波后得到prst_n,因此我们只需要分析prst_n的行为影响即可。

1.正常工作状态下,prst_n==1;

1.

2.异步复位时prst_n由1跳转为0,两个D触发器立刻被复位。也就是说rst_work_n会立即下拉至低电平复位系统,这个下拉显然时候不受时钟控制的,因此实现了异步复位;

3.复位撤离时prst_n由0跳转为1,两个D触发器的复位被撤销了开始正常工作。但是高电平需要两个周期才会到达rst_work_n端,这两个周期足以消除复位带来的亚稳态并且保证系统感知的复位rst_work_n在时钟沿上,因此实现了同步撤销;

借助于这个电路设计,系统的异步复位同步撤离功能就实现了。不过当年我还问了大佬一个问题:这样的话系统就延时了2个周期才复位的啊,会不会有bug?

大佬的回答是这样的:你这啥系统啊真的在乎这一两个周期的事么?早跑几周期晚跑几周期有啥关系,只要别跑错了就行!

-

寄存器

+关注

关注

31文章

5620浏览量

130423 -

D触发器

+关注

关注

3文章

181浏览量

49899 -

异步复位

+关注

关注

0文章

48浏览量

13704 -

时钟控制

+关注

关注

0文章

19浏览量

7209

发布评论请先 登录

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

异步复位同步撤离是什么意思?如何做到异步复位同步撤离呢?

异步复位同步撤离是什么意思?如何做到异步复位同步撤离呢?

评论