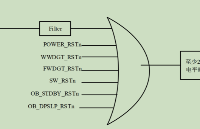

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局

2014-08-28 17:10:03 8153

8153 本文描述了复位的定义,分类及不同复位设计的影响,并讨论了针对FPGA和CPLD的内部自复位方案。

2016-07-11 14:33:49 6228

6228

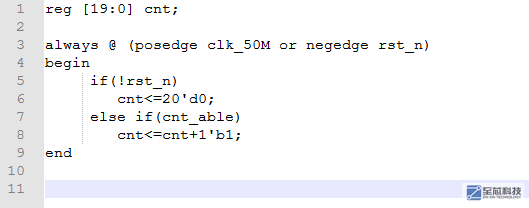

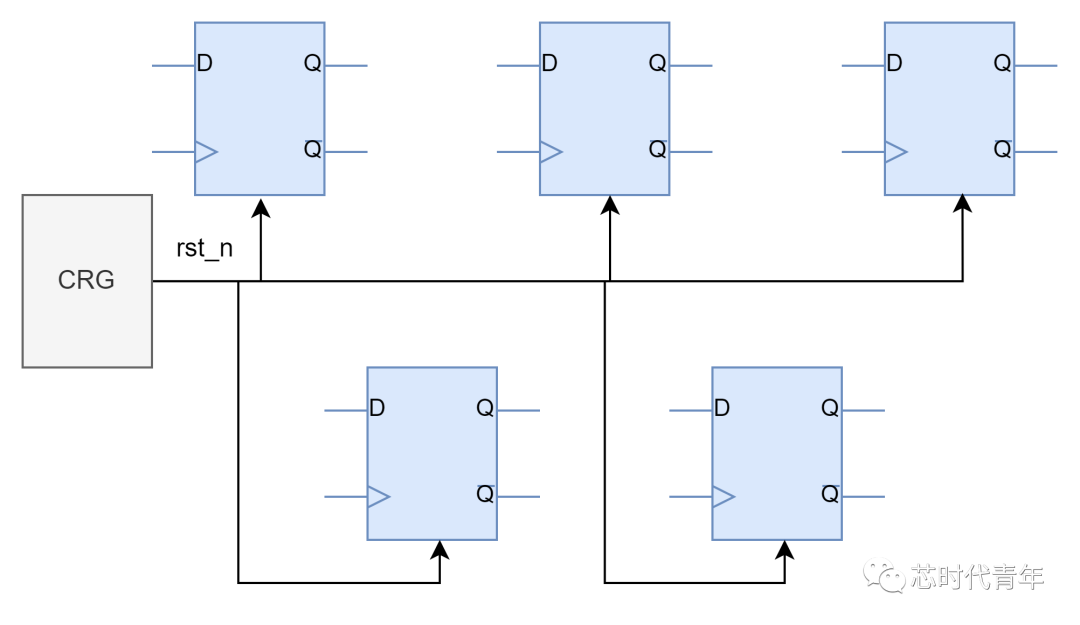

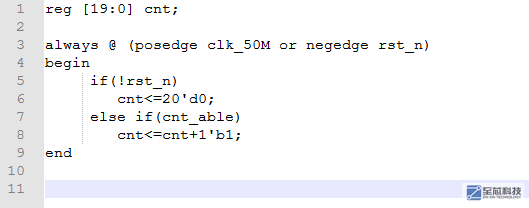

可以看到以下形式的进程: 信号rst_n用来对进程中所用变量的初始化,这个复位信号是十分重要的,如果没有复位,会导致一些寄存器的初始值变得未知,如果此时FPGA就开始工作的话,极易导致错误。 那么,这个复位信号来自何处?难道我们做好的系统,每次

2018-06-18 19:24:11 19894

19894

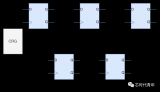

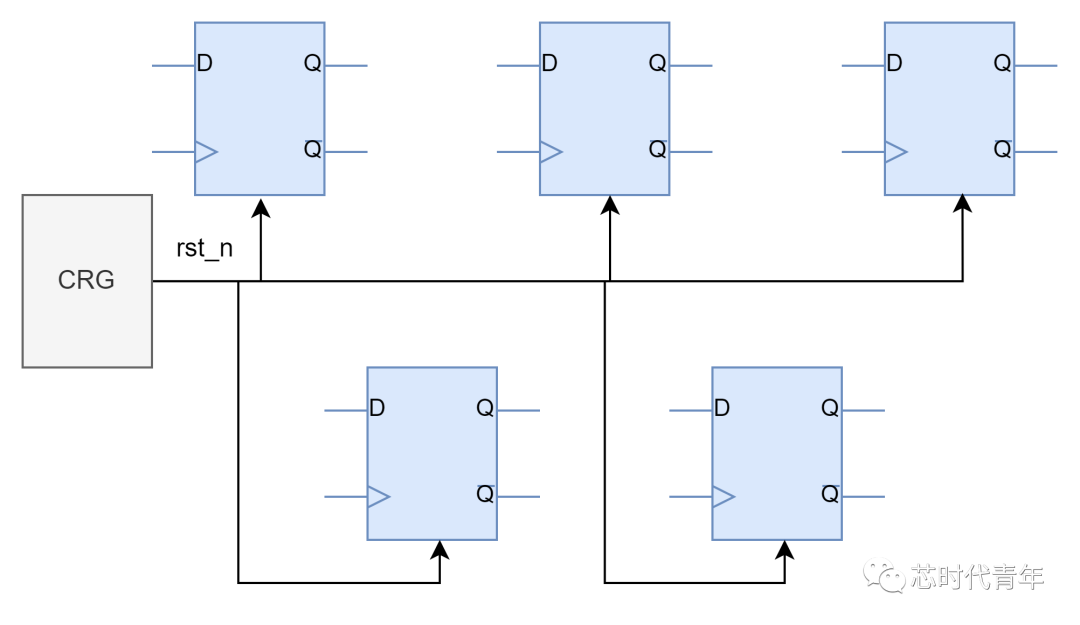

随着FPGA设计越来越复杂,芯片内部的时钟域也越来越多,使全局复位已不能够适应FPGA设计的需求,更多的设计趋向于使用局部的复位。本节将会从FPGA内部复位“树”的结构来分析复位的结构。 我们的复位

2019-02-20 10:40:44 1068

1068

在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

2020-06-26 16:37:00 1232

1232

最近看advanced fpga 以及fpga设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-09-01 15:37:07 1461

1461

本篇文章参考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global 在没看这篇文章前,回想一下平时我们常用的复位方式

2020-11-18 17:32:38 3110

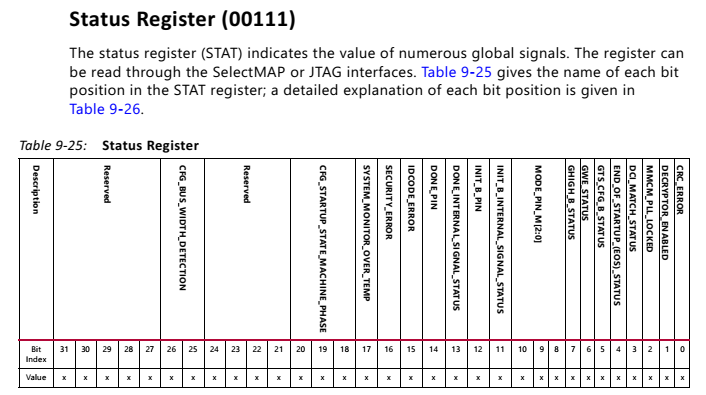

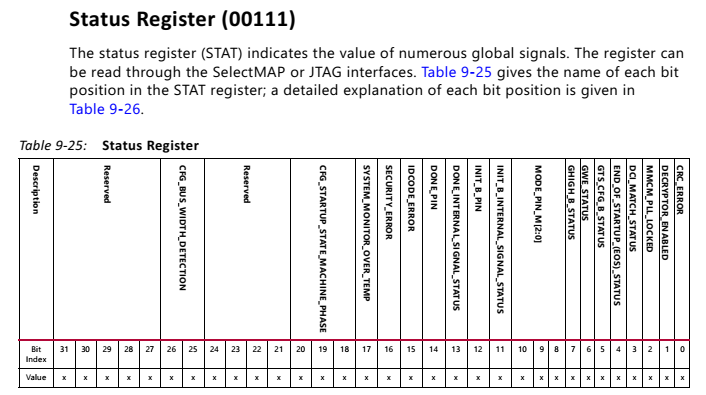

3110 第一步要做的,永远都是拉出FPGA的状态字寄存器Status Register看,它能直接告诉你或者极大地辅助判断失败的原因!

2020-12-01 12:20:16 8121

8121

作者:NingHeChuan Get Smart About Reset: Think Local, Not Global。 对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间

2020-12-25 12:08:10 2303

2303

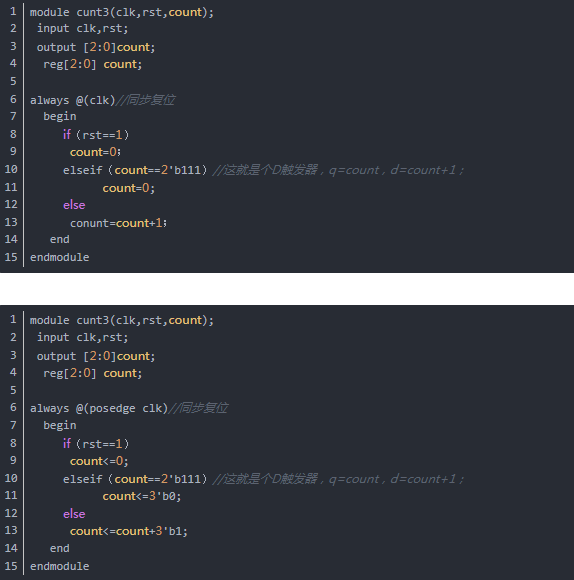

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 1679

1679

在FPGA设计中,当复位整个系统或功能模块时,需要将先关寄存器被清零或者赋初值,以保证整个系统或功能运行正常。在大部分的设计中,我们经常用“同步复位”或“异步复位”直接将所有的寄存器全部复位,这部分可能大家都习以为常。但实际上,是否需要每个寄存器都进行复位呢?这是一个值得探讨的问题。

2023-05-14 14:49:19 1701

1701

针对异步复位、同步释放,一直没搞明白在使用同步化以后的复位信号时,到底是使用同步复位还是异步复位?

2023-06-21 09:59:15 647

647

复位信号几乎是除了时钟信号外最常用的信号了,几乎所有数字系统在上电的时候都会进行复位,这样才能保持设计者确定该系统的系统模式的状态,以便于更好的进行电子设计,并且在任意时刻,确保使用者总能对电路系统进行复位,使电路从初始的状态开始工作。

2023-07-27 09:48:30 4638

4638

Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

2023-11-14 17:49:43 736

736

解复位就是复位撤离,系统解复位就是复位结束了系统准备开始工作。

2023-11-28 12:20:38 382

382

解复位就是复位撤离,系统解复位就是复位结束了系统准备开始工作。

2023-12-04 15:25:24 387

387

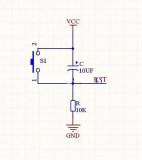

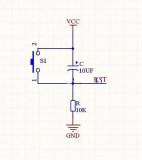

从Cyclone III handbook 上看,FPGA内部是包含POR, 即上电复位的,但是我习惯自己加一个reset。如果用电阻和电容搭建的reset电路,功能上是可以满足要求,但是这种电路

2014-06-26 22:38:52

保证器件内部逻辑快速进入正常的工作状态。因此,FPGA器件外部通常会引入一个用于内部复位的输入信号,这个信号称之为复位信号。对于低电平有效的复位信号,当它的电平为低电平时,系统处于复位状态;当它从

2019-04-12 06:35:31

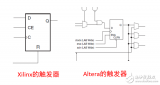

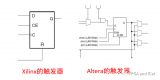

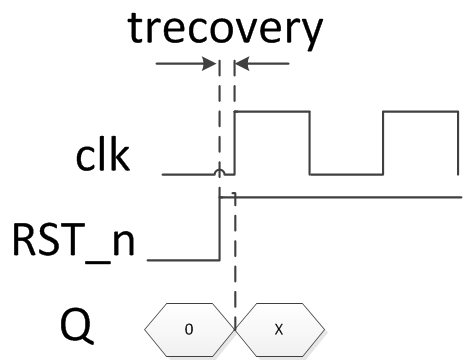

和removal时序检查;异步复位同步撤离(推荐使用) 优点:能避免纯异步或纯同步复位的潜在问题。它是FPGA设计中最受欢迎的复位,Altera建议使用这种复位方法。这种复位在使用前需要同步到各个使用时

2014-03-20 21:57:25

随着FPGA设计越来越复杂,芯片内部的时钟域也越来越多,使全局复位已不能够适应FPGA设计的需求,更多的设计趋向于使用局部的复位。本节将会从FPGA内部复位“树”的结构来分析复位的结构。我们的复位

2019-05-17 08:00:00

以前从来没有对FPGA的复位可靠性关注过,想当然的认为应该不会有什么问题。当问题真正出在复位上的时候,才又仔细地对FPGA的复位深入的了解了一下。首先我们用的复位管脚不是FPGA的全局管脚,并且复位

2011-11-04 14:26:17

保证器件内部逻辑快速进入正常的工作状态。因此,FPGA器件外部通常会引入一个用于内部复位的输入信号,这个信号称之为复位信号。对于低电平有效的复位信号,当它的电平为低电平时,系统处于复位状态;当它从

2015-04-10 13:59:23

FPGA的最小系统:1、芯片2、有源晶振电路3、复位电路4、下载调试电路5、电源电路6、存储器

2022-10-04 12:11:07

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2019-09-24 11:54:53

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-07-16 15:32:39

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-08-23 10:33:54

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-09-18 11:15:11

的大小等。 2.基本可编程逻辑单元 FPGA的基本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完成纯组合逻辑功能。FPGA内部寄存器可配置为带同步/异步复位和置位、时钟

2016-10-08 14:43:50

在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输出关联的系统产生不良影响,FPGA上电后要进行复位,且为了消除电源开关过程中引起的抖动影响,复位

2021-06-30 07:00:00

请问各位一下,这个电路图中的按键使怎么是复位系统复位的

2019-05-26 11:30:05

对于硬件设计来说,复位电路是必不可少的一部分,为了确保微机系统中电路稳定可靠工作,复位电路的第一功能是上电复位。在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态

2021-11-11 06:06:08

系统复位是什么意思?系统复位的条件有哪些?在哪几种情况下会产生内核复位呢?

2021-09-26 08:21:32

`1、引言在系统上电时,需要从外部载入所要运行的程序,此过程被称为程序加载。多数情况下,从外部专用的 读入程序。这种方式速度慢,而且只能加载固定的程序。显然,当系统需要容量大而且 FPGA要加载

2019-12-10 17:42:18

register LPSC MMRs(memory-mapped registers) 一般我们不使用局部复位,如果上电复位后,发现某些核处于复位状态,而其他核可以连接使用,多半是局部复位造成的,应该把LRESETNMIEN 设置为1,则可以避免这个问题。

2020-12-14 16:01:54

各位好,有个小问题请教一下。最近在做一个FPGA与DSP组成的电路板,想确定一下DSP的复位信号是从FPGA来比较好,还是由专门的复位电路控制比较好?你们是怎么做的?或者你们用的开发板是采用什么方案??望各位不吝赐教,谢谢。

2016-05-22 20:33:48

C5000的I/O空间和程序/数据空间是分开的,只能用来访问DSP的片上外设的寄存器。我有一个问题,I/O空间的寄存器和memory mapped register有何区别。呵呵,最近在学,想知道。。。。

2019-01-28 06:17:05

本帖最后由 何立立 于 2015-6-7 20:59 编辑

最近遇到FPGA复位信号的问题困扰很久,查了相关资料:FPGA设计是基于大量flip-flop或者寄存器的同步系统设计,所以所有这些

2015-06-07 20:39:43

状态,以保证器件内部逻辑快速进入正常的工作状态。因此,FPGA器件外部通常会引入一个用于内部复位的输入信号,这个信号称之为复位信号。对于低电平有效的复位信号,当它的电平为低电平时,系统处于复位状态;当

2016-07-25 15:19:04

memory region,使用Memory Region R Base Address Register

2018-06-19 07:21:06

大于1个时钟周期,并且会占用更多的逻辑资源。如果要实现稳定的系统,是否就可以考虑率除掉小于1个时钟周期的复位信号(有可能是外部的干扰或其他因素导致复位信号的异常),而现在的fpga芯片的逻辑资源也已经

2014-04-16 22:17:53

=11.818181991577148px]2、对于有些系列的FPGA的LE 有 同步复位,同步置位端,这种情况使用同步复/置位,比较省资源,但是对于没有同步复位端的FPGA,在程序中使用同步复/置位

2014-08-13 16:07:34

什么是Register Renaming(寄存器重命名)/Resource contention(资源冲突)

Register Renaming: (寄存器重命名)把一个指令的输出

2010-02-04 10:35:34 2243

2243 什么是Register Pressure(寄存器不足) / Register Renaming(寄存器重命名)?

Register Pressure(寄存器不足) 软件算法执行时所需

2010-02-04 11:02:20 1215

1215 什么是Remark/Register Contention/Register Pressure

Remark: (芯片频率重标识)芯片制造商为了方便自己的产品定级,把大部分CPU都设

2010-02-04 11:32:51 446

446 什么是Flash Memory Flash Memory即快擦型存储器,在

2010-01-07 10:00:21 1433

1433 介绍了一种基于SRAM技术的FPGA可编程逻辑器件的编程方法,能在系统复位或上电时自动对器件编程。有效地解决了基于SRAM的FPGA器件掉电易失性问题,针对当前系统规模的日益增大,本文提出了一种用单片机对多片FPGA自动加载配置的解决方案.

2011-03-15 16:41:22 21

21 电源、时钟和复位电路图(Altera FPGA开发板)如图所示:

2012-08-15 14:42:33 9398

9398

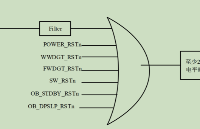

设计了一种片上系统(SoC)复位电路。该电路能对外部输入信号进行同步化处理以抑制亚稳态,采用多级D触发器进行滤波提升抗干扰能力,并且控制产生系统所需的复位时序以满足软硬

2013-09-25 14:58:17 45

45 在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对可靠的,因为它是芯片内部的信号。

2017-02-11 11:46:19 876

876

系统的复位系统由POR和PUC信号驱动,各种不同的事件能触发产生这些复位信号,而根据不同的复位信号会产生不同的初始化状态。

2017-09-21 15:59:59 1

1 一、register变量 关键字regiter请求编译器尽可能的将变量存在CPU的寄存器中。有以下几点注意的地方。 register变量必须是能被CPU寄存器所接受的类型,这通常意味着

2017-11-21 10:20:09 5

5 在FPGA设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何其它输入

2017-11-22 17:03:45 5125

5125

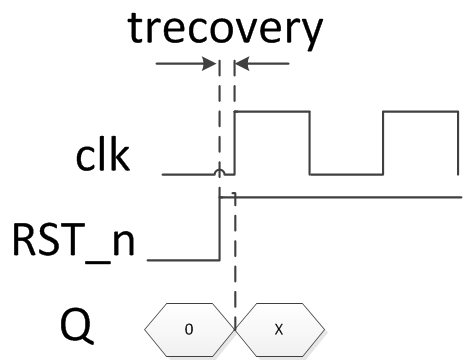

异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。

2018-06-07 02:46:00 1989

1989 对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 51单片机要复位只需要在第9引脚接个高电平持续2us就可以实现,那这个过程是如何实现的呢?在单片机系统中,系统上电启动的时候复位一次,当按键按下的时候系统再次复位,如果释放后再按下,系统还会复位。所以可以通过按键的断开和闭合在运行的系统中控制其复位。

2018-07-29 11:08:38 71185

71185

在实际设计中,由于外部阻容复位时间短,可能无法使FPGA内部复位到理想的状态,所以今天介绍一下网上流行的复位逻辑。

2018-08-07 09:17:18 10969

10969 FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。

2018-08-08 15:14:23 10154

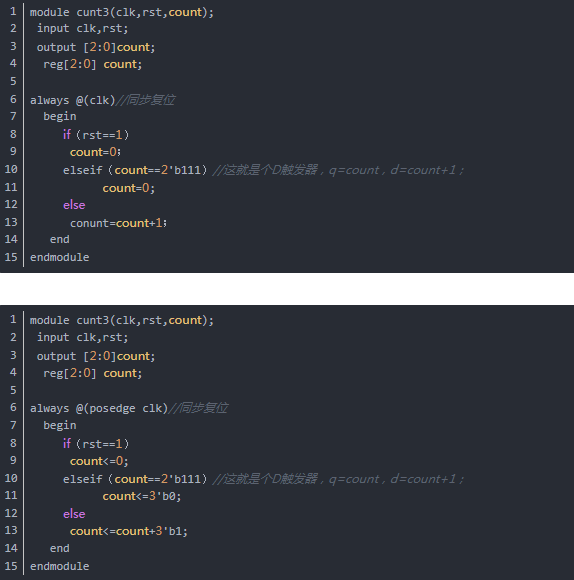

10154 分析:首先,我们可以看到有哪些信号。复位rst 、计数器3位的、时钟信号。(用到2路选择器。复位和不复位)

其次,怎样实现,一个时钟过来,记一次数就是加一次,保存(用到D触发器),满之后为0;

2019-02-01 07:08:00 2354

2354

一开始接触到FPGA,肯定都知道”复位“,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。

2019-02-17 10:49:53 7670

7670

FPGA设计中,层次结构设计和复位策略影响着FPGA的时序。在高速设计时,合理的层次结构设计与正确的复位策略可以优化时序,提高运行频率。

2019-02-15 15:15:53 849

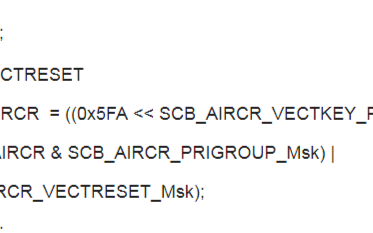

849 系统复位是置位同一个寄存器中的 SYSRESETREQ 位。

2019-07-31 16:12:10 39293

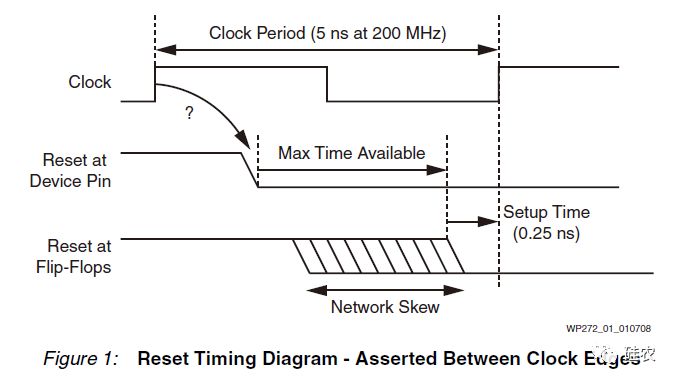

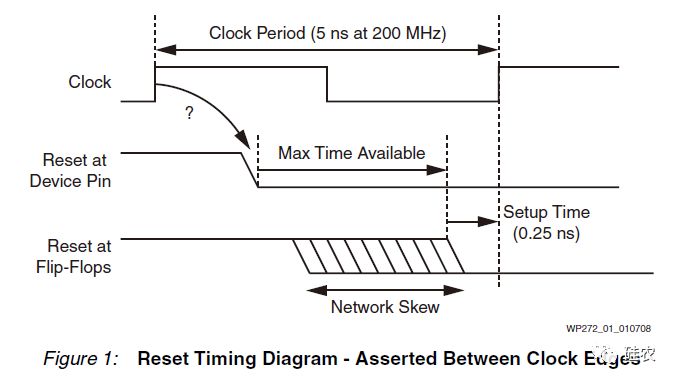

39293 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑,诸如:clk skew,组合 逻辑路径延时,复位延时等因素。

2019-08-21 17:51:49 1745

1745 STM32复位来源、以及系统和内核复位区别

2020-02-28 17:13:28 7102

7102 CM3(STM32)内核复位与系统复位区别及应用

2020-03-20 09:43:18 4274

4274

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19:00 2456

2456

FPGA开发中,一种最常用的复位技术就是“异步复位同步释放”,这个技术比较难以理解,很多资料对其说得并不透彻,没有讲到本质,但是它又很重要,所以对它必须理解,这里给出我的看法。

2020-08-18 13:56:00 1114

1114

最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。 流程: 1. 异步复位: 优点:⑴大多数

2020-10-30 12:17:55 323

323 最近看 advanced fpga 以及 fpga 设计实战演练中有讲到复位电路的设计,才知道复位电路有这么多的门道,而不是简单的外界信号输入系统复位。

2020-12-22 12:54:00 13

13 接触FPGA的朋友们都知道“复位”,即简单又复杂。简单是因为初学时,只需要按照固定的套路——按键开关复位,见寄存器就先低电平复位一次,这样一般情况可以解决99%的问题,甚至简单的设计,就不可能有问题。复杂是因为复位本身是对大规模的硬件单元进行一种操作,必须要结核底层的设计来考虑问题。

2021-04-03 09:34:00 7995

7995 电子发烧友网为你提供FPGA设计中常用的复位设计资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-10 08:40:04 40

40 基于FPGA的小波滤波抑制复位噪声方法

2021-07-01 14:42:09 24

24 对于硬件设计来说,复位电路是必不可少的一部分,为了确保微机系统中电路稳定可靠工作,复位电路的第一功能是上电复位。在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态

2021-11-06 09:20:57 20

20 复位介绍STM32F10xxx支持三种复位形式,分别为系统复位、上电复位、备份区域复位1.系统复位除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器以外,系统复位将复位所有寄存器

2021-12-24 19:32:52 4

4 1、复位 共有三种类型的复位,分别为系统复位、电源复位和备份域复位。1.1、系统复位 除了时钟控制寄存器 CSR 中的复位标志和备份域中的寄存器外,系统复位会将其它全部寄 存器都复位

2021-12-27 18:24:24 9

9 复位的作用: 复位指将STM32系统各功能寄存器及I/O口设为最初状态(备份区域不被复位)。复位形式 共有三种复位形式:1.电源复位 2.系统复位 3.备份区域复位电源复位

2021-12-27 18:57:40 16

16 一、设置内核控制寄存器 core control register __set_CONTROL(0);二、关闭所有中断__disable_interrupt();三、复位 在应用中断和复位控制

2022-01-17 12:43:54 0

0 复位和异步复位异步复位异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。RTL代码如下:always @ (posedge clk or negedge rst_n) if(!rst_n) b..

2022-01-17 12:53:57 4

4 每一块STM32中都有这么一个RCC复位和时钟控制模块。STM32的复位为三类:系统复位、电源复位和后备域复位。

2022-02-10 10:30:52 6

6 首先回想一下,在平常的设计中我们是不是经常采用同步复位或者异步复位的写法,这一写法似乎都已经形成了肌肉记忆----每次我们写always块的时候总是会对所有的寄存器写一个复位赋初值的语句。

2022-02-19 19:10:32 2092

2092 在这些情况下,复位信号的变化与FGPA芯片内部信号相比看起来是及其缓慢的,例如,复位按钮产生的复位信号的周期至少是在毫秒级别的,而我们FPGA内部信号往往是纳米或者微秒级别的。

2022-05-06 10:48:45 2462

2462 在进行design partition时,相比register in更推荐register out,请问为什么呢?如果前后两个模块时钟域不同,register in会有什么问题?

2022-08-18 11:54:20 861

861 我们知道,STM32芯片里有很多系统级的复位,比方上电复位、欠压复位、看门狗复位、软件复位、复位脚电平触发复位等等。这些系统级的复位往往都是针对整个芯片或芯片的绝大部分区域。

2022-10-19 09:06:43 4058

4058 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-03-13 10:29:49 1585

1585 Memory Compiler由供应商提供,往往是不通用的,界面也不尽相同。同一个厂商的不同工艺下,Memory Compiler不同。相同工艺,不同厂商,Memory Compiler也不同。内存编译器通常是供应商的知识产权,其功能是根据客户的需求生成各种类型的memory。

2023-03-28 11:41:48 2356

2356 FPGA设计中几乎不可避免地会用到复位信号,无论是同步复位还是异步复位。我们需要清楚的是复位信号对时序收敛、资源利用率以及布线拥塞都有很大的影响。

2023-03-30 09:55:34 806

806 前两期,我们分别对OTP和MTP,RAM和ROM进行了比较。这一次,我们来谈谈Memory Compiler,以及通过它生成的Register file和SRAM。

2023-03-31 10:56:37 8521

8521 。 下面将讨论FPGA/CPLD的复位电路设计。 2、分类及不同复位设计的影响 根据电路设计,复位可分为异步复位和同步复位。 对于异步复位,电路对复位信号是电平敏感的,如果复位信号受到干扰,如出现短暂的脉冲跳变,电路就会部分或全部被

2023-04-06 16:45:02 782

782 本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,对于复位这个问题可以算是老生常谈了,但是也是最容易忽略的点。本文结合FPGA的相关示例,再谈一谈复位。

2023-05-12 16:37:18 3347

3347

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。

2023-05-22 14:21:08 577

577

本文将探讨在 FPGA 设计中添加复位输入的一些后果。 本文将回顾使用复位输入对给定功能进行编码的一些基本注意事项。设计人员可能会忽略使用复位输入的后果,但不正确的复位策略很容易造成重罚。复位

2023-05-25 00:30:01 483

483 有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

2023-05-25 15:50:45 2110

2110

对于复位信号的处理,为了方便我们习惯上采用全局复位,博主在很长一段时间内都是将复位信号作为一个I/O口,通过拨码开关硬件复位。

2023-06-21 10:39:25 651

651

能不复位尽量不用复位,如何判断呢?如果某个模块只需要上电的时候复位一次,工作中不需要再有复位操作,那么这个模块可以不用复位,用上电初始化所有寄存器默认值

2023-06-28 14:44:46 526

526

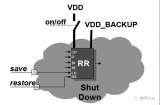

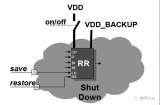

在电源关断模块有可能要求register对关断前的数据进行锁存或者在电源打开后要求对锁存的数据进行恢复,这就需要特殊的单元Retention Register。

2023-06-29 12:46:23 190

190

内核复位:它会使STM32内核(Cortex-M)进行复位,而不会影响其外设,如GPIO、TIM、USART、SPI等这些寄存器的复位。

2023-08-01 17:21:40 3103

3103 点击上方 蓝字 关注我们 系统的复位对于系统稳定工作至关重要,最佳的复位方式为:异步复位,同步释放。以下是转载博客,原文标题及链接如下: 复位最佳方式:异步复位,同步释放 异步复位; 异步

2023-09-09 14:15:01 282

282

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

GD32 MCU的复位分为电源复位和系统复位,电源复位又称为冷复位,相较于系统复位,上电复位更彻底,下面为大家详细介绍上电复位和系统复位的实现以及区别。

2024-02-02 09:37:44 363

363

电子发烧友App

电子发烧友App

评论