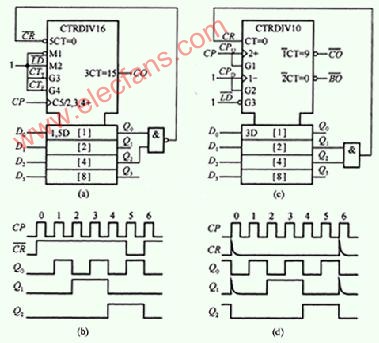

计数器应用实例

除了计数功能外,计数器产品还有一些附加功能,如异步复位、预置数(注意,有同步预置数和异步预置数两种。前者受时钟脉冲控制,后者不受时钟

2010-05-27 09:37:55 6778

6778

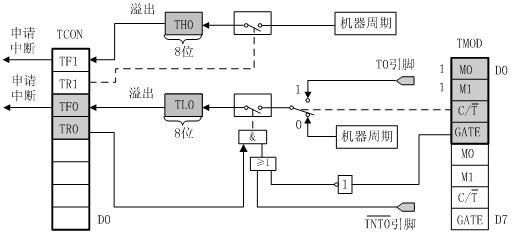

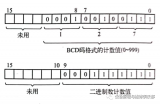

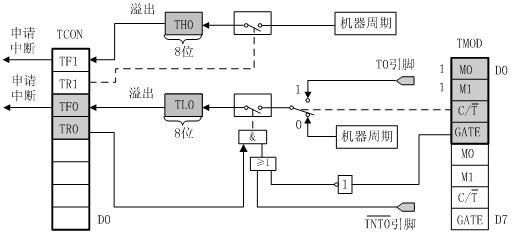

定时器/计数器的结构定时器/计数器的实质是加1计数器(16位),由高8位和低8位两个寄存器组成。TMOD是定

2018-01-22 11:17:10 19789

19789

构建一个4位二进制计数器,计数范围从0到15(包括0和15),计数周期为16。同步复位输入时,将计数器重置为0。

2022-12-02 09:20:28 6560

6560 功能中,对我们组成任意进制计数器最有用的功能有复位功能、置位功能、预置数功能。复位功能:是在复位端有效时,将本计数器复位,使其状态为“0”,即输出端完全置“0”。但复位功能有同步复位和异步复位之别

2008-07-05 13:41:26

定时器与外部触发的同步1.复位模式:计数器使用内部时钟计数,然后正常运转,直到出现TI1上升沿,当TI1出现上升沿时,计数器清零然后重新从零开始计数。TI1上升沿与实际计数器复位之间的延迟是由于

2021-08-18 06:59:12

STM8触发同步计数器允许四种触发输入ETRTI1TI2来自TIM5/TIM6的TRGOTIM1的计数器使用三种模式与外部的触发信号同步:标准触发模式,复位触发模式和门控触发模式。

2020-11-09 07:06:59

一个计数器写入,一个计数器读取,这怎么同步

2014-11-19 21:27:52

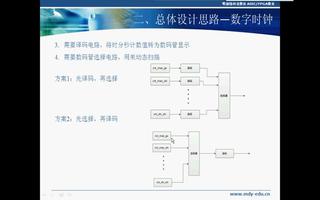

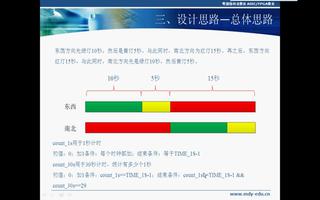

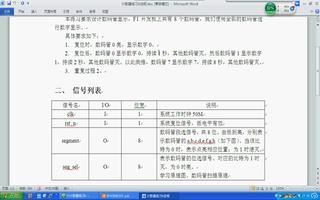

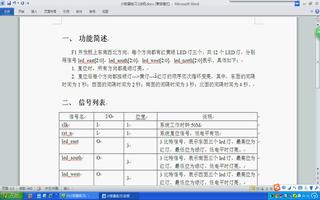

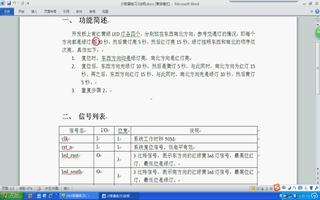

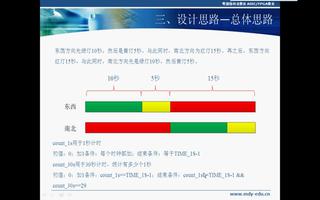

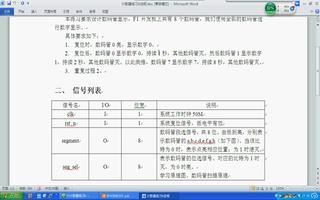

的十位,Result[3:0]代表个位,RSTn为复位输入信号。将计数器的结果Result输出给数码管显示。功能模块图与输入输出引脚说明该工程包含顶层模块counter24与底层模块

2022-07-05 15:14:27

如何构建一个具有同步复位端的CMOS四进制计数器?输入端 复位控制信号RESET 时钟信号clk输出端 Q3 Q2 Q1 Q0 carry

2016-12-10 17:56:10

8253微机接口芯片作为定时器和计数器时实质相同吗?定时器/计数器8253内部有多少个16位的计数器?

2021-10-20 06:16:30

、T1的启动和停止计数,同时包含了T0、T1的状态。单片机复位时,两个寄存器的所有位都被清0。4种工作方式(方式0-方式3):M1 M0 工 作 方 式0 0 方式0,13位定时器/计数器。0 1 方式1,16位定时器/计数器。1 0 方式2,8位常数自动.

2022-02-28 10:42:12

两个32位计数器,但我希望这些计数器的计数速率高达3GHz。看起来低端FPGA(即Spartan 6)的最大频率为200-300 MHz。因此,我计划使用离散ECL逻辑在片外实现4个LSB,并在FPGA

2019-04-19 13:34:34

TTL 二进制同步可逆计数器

2009-08-03 09:05:53 26

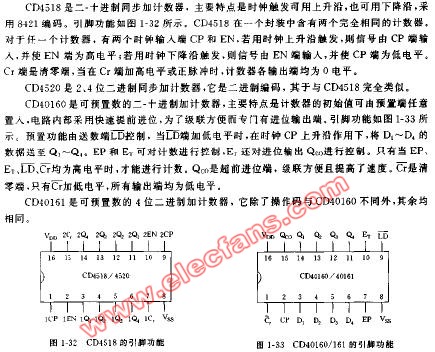

26 4位二进制同步计数器74LS161引脚图及功能表

4位二进制同步计数器74LS161

2007-11-22 12:51:59 59976

59976

计数器级联时的时钟构成方式可以采用同步时钟,也可以采用异

2008-06-30 00:03:32 11945

11945

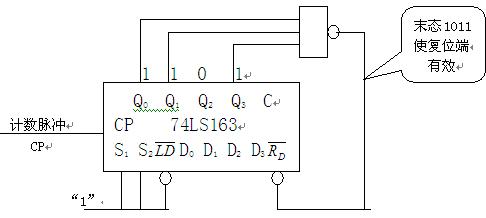

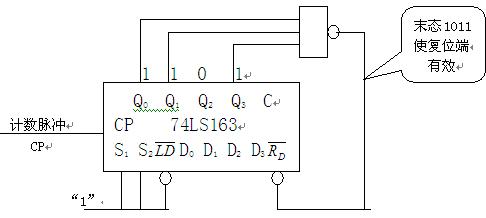

在具有同步复位功能的集成计数器中使用复位法(同步复位法),和在具有异步复位功能的集成计数器中使用复位法(异步复位法)是有区别的。这是由同步复位功能与异步

2008-07-05 14:13:15 11686

11686

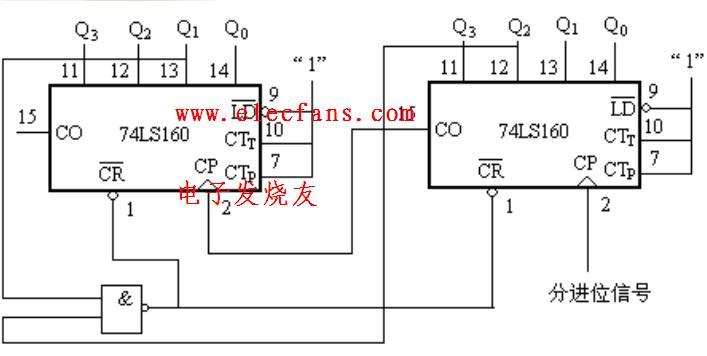

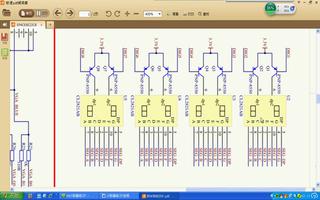

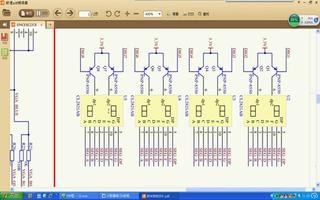

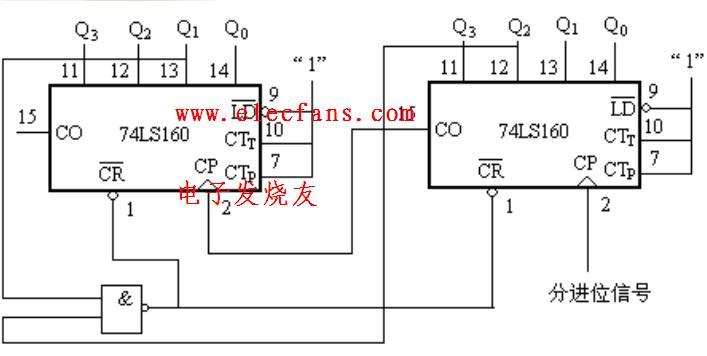

我们可以采用具有保持功能的同步集成计数器(如74LS160)组成同步计数器,电路如图3-4所示。在160计数器中当S1=S2

2008-07-05 14:17:49 5303

5303

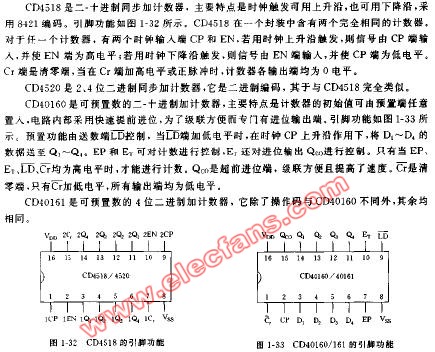

同步计数器的应用:详细介绍CD40161芯片.

2008-12-17 14:33:18 1107

1107

定时器/计数器的结构和工作原理

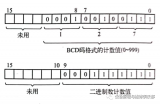

定时器/计数器的结构 定时器/计数器的实质是加1计数器(16位),由高8位和低8位两个寄存器组成

2009-03-29 09:08:05 20284

20284

第二十五讲 同步计数器

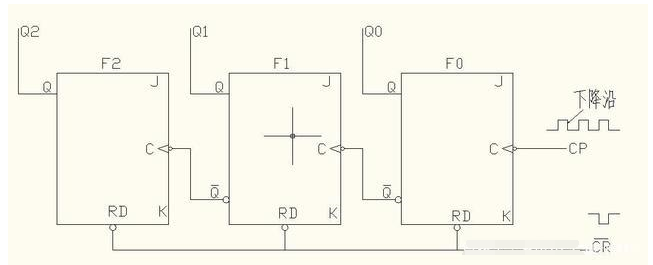

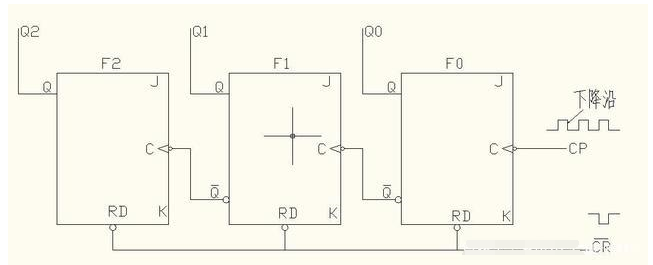

7.3.2 同步计数器一、同步二进制计数器1.同步二进制加法计数器JK触发器组成的4位同步二进制加法

2009-03-30 16:28:45 9958

9958

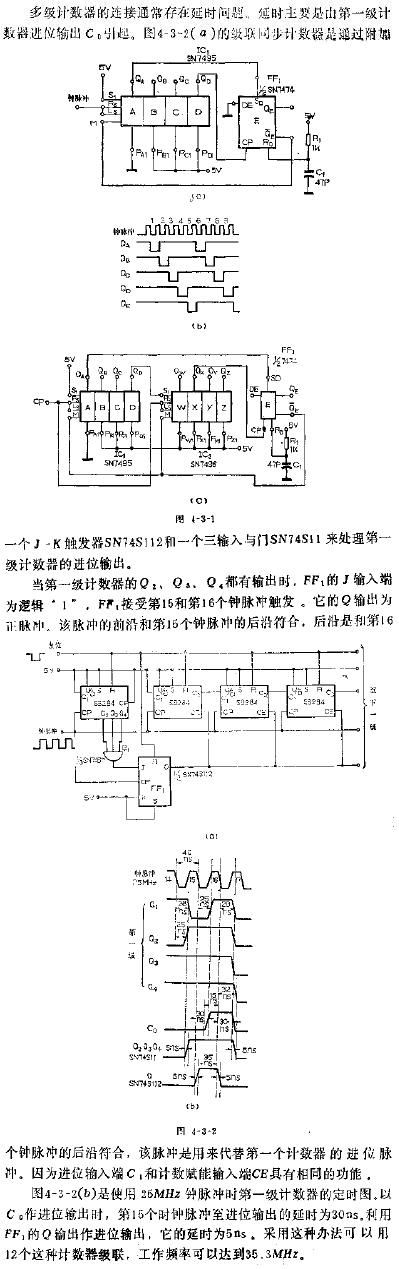

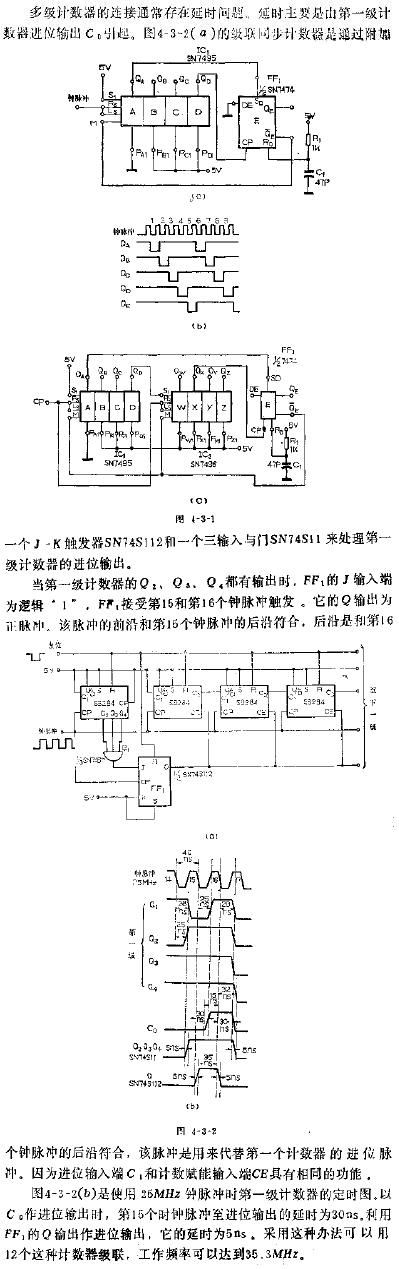

宽频带级联同步计数器

2009-04-10 10:24:56 863

863

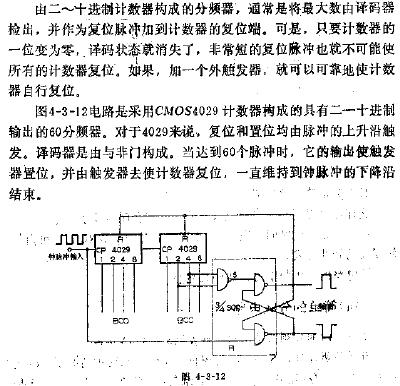

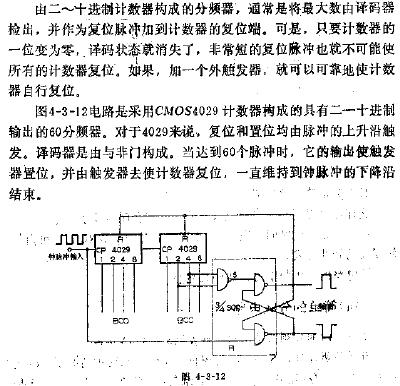

用一个外加触发器使计数器可靠的自行复位

2009-04-10 10:27:12 505

505

12位二进制计数器

2009-09-16 15:56:08 6790

6790

8421码同步十进制递增计数器

2009-09-24 11:09:34 6883

6883

同步二进制计数器

1. 同步与异步二进制加法计数器比较态序表和工作波形一样电路结构不同: 异步二进制加法

2009-09-30 18:37:29 12854

12854

利用复位端构成的模6计数器电路

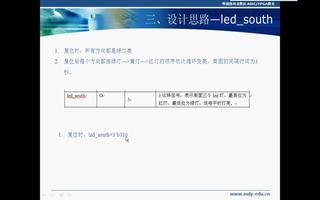

利用集成计数器的预置端和复位端可以构成任意模计数器。下图所示依次是利用74163和74192构成的

2010-01-12 13:54:31 5952

5952

计数器的同步扩展

2010-01-12 13:57:16 1257

1257

环形计数器和扭环形计数器

移位寄存器也可以构成计数器,称为移位型计数器。它有两种结构:环形计数器和扭环形计数器。

2010-01-12 14:07:46 10310

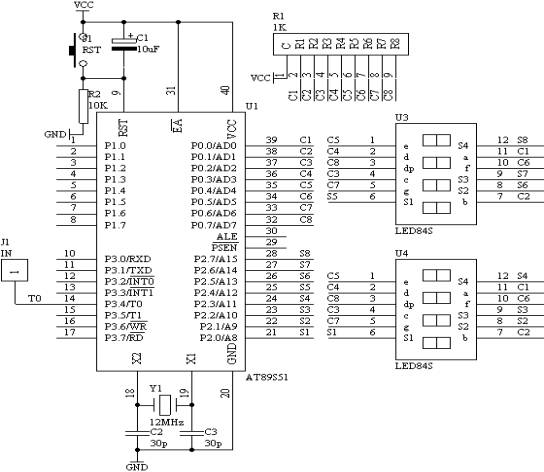

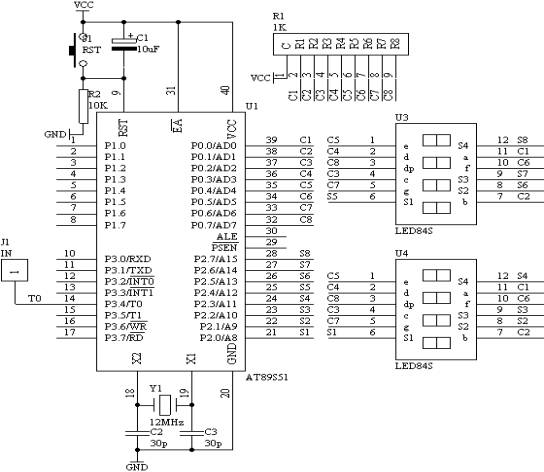

10310 6位数显频率计数器

1.实验任务

利用AT89S51单片机的T0、T1的定时计数器功能,来完成对输入的信号进行频率计数,计数的频率结果通过8位动态数码管显示出来。

2010-02-02 10:57:39 1995

1995

计数器,计数器的工作原理是什么?

在数字系统中使用最多的时序电路是计数器。计数器不仅能用于对时钟脉冲进行计数还可以用于分频、定时,产生

2010-03-08 13:50:14 62401

62401 简单改变FPGA计数器规格使作为DAC功能PWM计数器的纹波降低。

2012-04-06 11:11:57 2240

2240

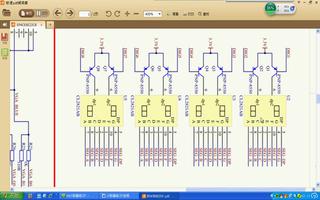

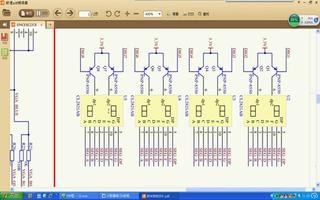

计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值计数器电路,并用Multisim软件进行了

2013-07-26 11:38:41 134

134 介绍计数器的基本原理(如异步,同步二进制计数器,以及对误差,性能的分析)

2015-12-17 14:52:39 3

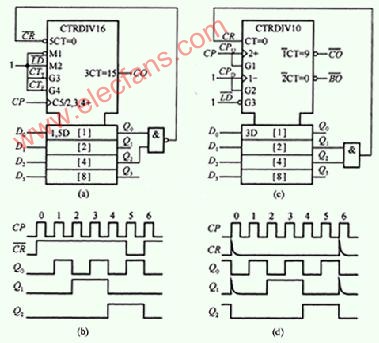

3 数字电子技术--中规模集成计数器及其应用--同步、异步二五十进制计数器-PPT

2016-03-22 14:33:06 0

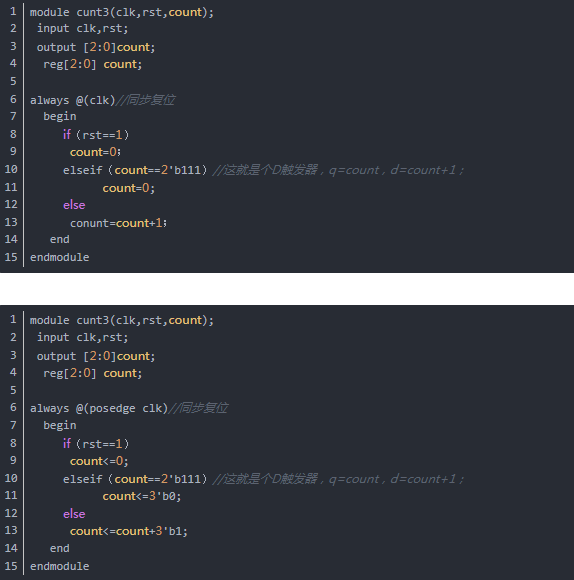

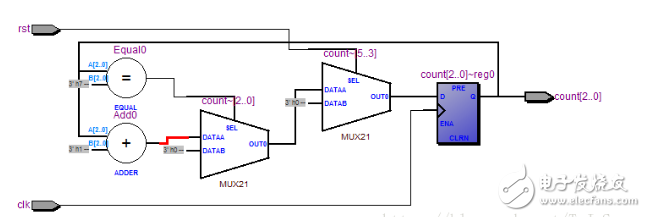

0 1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 17

17 基于VHDL的EDA实验---3位二进制计数器

2017-11-08 17:45:53 1

1 本文主要介绍了74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)。74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端

2018-01-18 10:56:39 496025

496025

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 7577

7577 计数器

2019-09-03 06:07:00 2313

2313

计数器

2019-09-03 06:15:00 2096

2096

计数器

2019-09-03 06:14:00 2052

2052

计数器

2019-09-03 06:11:00 4211

4211

计数器

2019-09-03 06:10:00 3681

3681

计数器

2019-09-03 06:09:00 3231

3231

计数器

2019-09-03 06:08:00 2461

2461

计数器

2019-09-03 06:06:00 3401

3401

计数器

2019-09-03 06:05:00 3079

3079

计数器

2019-09-03 06:04:00 6168

6168

计数器

2019-09-03 06:03:00 3008

3008

计数器

2019-09-03 06:02:00 2687

2687

计数器

2019-09-03 06:01:00 3592

3592

计数器

2019-09-02 06:10:00 6141

6141

同步计数器之所以被称为是因为计数器内所有单个触发器的时钟输入都由同一时钟信号同时同时计时。

2019-06-23 10:16:39 27682

27682

采用同步清零或置数方式完成的计数器,一般不会出现竞争冒险现象,而采用异步清零或置数方式完成的计数器往往会出现竞争冒险现象。以 74LS160 同步计数器( 异步复位、同步置数) 组成的 7 进制

2019-08-28 08:00:00 7

7 本文档的主要内容详细介绍的是同步7进制计数器的设计资料免费下载。

2020-05-20 08:00:00 11

11 该计数器从0 计数到4294967295,然后回滚到0 并重新开始计数。它只需要FPGA 上一点点的资源就可以迅速完成计数,这都多亏了FPGA 中隐藏的进位链。让我们来看这种计数器的几种变体。

2020-12-11 17:26:55 12

12 该计数器是一个3位二进制异步减法计数器,它与前面介绍过的3位二进制异步加法计 数器一样,是由3个JK触发器组成,其中J、K端都悬空(相当于J=1、K=1),两者的不同 之处在于,减法计数器是将前一个触发器的Q非端与下一个触发器的CP端相连。

2021-04-18 11:19:47 19763

19763

(定时/计数选择位):C/T=0——定时模式C/T=1——计数模式3.M0M1(工作方式选择位)00——方式0——13位定时/计数器01——方式1——16位定时/计数器10——方式2——8位自动重装定时/计数器11——方式3——两个独立的8位定时计数器(仅T0,T1不工作)二 TCON(

2021-11-22 16:36:03 8

8 在生产过程中,经常需要记录现场发生的次数,并据此发出控制命令,计数器就是为完成这一功能而开发的。 S7 CPU为计数器预留了一个计数器存储区。每个计数器都有一个16位计数器字和一个二进制计数器位

2021-12-21 16:27:37 3846

3846 定时器/计数器的工作原理及应用定时器/计数器是增1计数器定时器/计数器T0、T1有四种工作方式(方式0123),由TMOD选择,TCON控制启停+显示状态计数器的起始计数是从初值开始。单片机复位时计数器

2021-12-31 19:31:50 11

11 计数器清零就是将计数值清零,那么计数器同步清零和异步清零之间有什么区别呢?

2022-01-29 16:45:00 33841

33841 multisim仿真四位计数器资料分享

2022-07-23 09:57:41 14

14 电子发烧友网站提供《FPGA上的十六进制计数器.zip》资料免费下载

2022-11-23 10:47:06 10

10 本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA 板上实现。

2022-12-20 14:52:25 4

4 S7-1200的计数器为IEC计数器,用户程序中可以使用的计数器数量仅受CPU的存储器容量限制。

2023-01-29 09:31:56 11556

11556 可预置同步4位二进制计数器;异步复位-74LVC161

2023-02-15 19:23:09 0

0 可预置同步 4 位二进制向上/向下计数器-74HC191

2023-02-15 19:39:04 5

5 可预置同步 4 位二进制向上/向下计数器-74HC_HCT193

2023-02-15 19:40:01 0

0 可预置同步4位二进制计数器;同步复位-74LVC163

2023-02-16 20:48:19 0

0 可预置同步4位二进制计数器;异步复位-74HC161_Q100

2023-02-16 21:10:00 1

1 可预置同步4位二进制计数器;异步复位-74HC161

2023-02-16 21:10:17 4

4 双4位同步二进制计数器-74HC_HCT4520_Q100

2023-02-17 19:22:15 0

0 双4位同步二进制计数器-74HC_HCT4520

2023-02-17 19:22:25 1

1 可预置同步BCD十进制计数器;异步复位-74HC160

2023-02-20 20:05:50 11

11 可预置同步4位二进制计数器;同步复位-74HC_HCT163_Q100

2023-02-21 18:35:38 0

0 可预置同步4位二进制计数器;同步复位-74HC_HCT163

2023-02-21 18:35:57 0

0 8位同步二进制递减计数器-74HC40103

2023-03-03 19:49:59 3

3 在数字电子产品中,计数器是由一系列触发器组成的时序逻辑电路。顾名思义,计数器用于计算输入在负或正边沿转换中出现的次数。根据触发触发器的方式,计数器可以分为两类:同步计数器和异步计数器。了解这两种计数器的工作原理以及它们之间的区别。

2023-03-25 17:31:07 29523

29523

加计数器(S_CU)在计数初始值预置输入端S上有上升沿时,PV装入预置值,输入端CU每检测到一次上升沿,当前计数值CV加1(前提是CV 小于999);当前计数值大于0时,Q输出为高电平“1”;当R端子的状态为“1”时,计数器复位,当前计数值CV为“0”,输出也为“0”。加计数器指令和参数见图2

2023-04-27 15:38:22 4139

4139

同步计数器和异步计数器的区别详解 同步计数器和异步计数器是数字电路中两种常见的计数器类型,它们在实现方式和功能上存在明显的区别。本文将详细介绍同步计数器和异步计数器的区别,包括其工作原理、特点

2023-12-13 14:54:24 15772

15772 同步计数器和异步计数器是两种常见的数据结构,它们都用于控制对共享资源的访问。它们的主要作用是实现多个线程之间的同步和并发控制。尽管它们都被用于同步的目的,但它们有很多不同的特点和用例。 同步计数器

2023-12-15 10:49:43 3177

3177 计数器是一种被广泛应用于各个领域的实用工具,在我们的日常生活中随处可见。无论是进行时间统计,协助工作任务的完成,还是用于科学研究和编程技术,在各个领域都起到了重要的作用。本文将详细介绍计数器

2024-02-03 10:04:14 9281

9281 计数器是计算机领域中常用的一种数据结构,用于记录和控制程序执行中的指令或事件发生的次数。计数器可以根据同步机制或异步机制进行操作。本文将详细讨论计数器的同步性和异步性,深入探讨两者的区别及其在实际

2024-02-22 15:14:02 5568

5568 电子发烧友网站提供《同步4位十进制和二进制计数器数据表.pdf》资料免费下载

2024-05-09 11:29:05 3

3 电子发烧友网站提供《同步4位上/下二进制计数器数据表.pdf》资料免费下载

2024-05-14 09:40:27 0

0 电子发烧友网站提供《同步4位上/下计数器数据表.pdf》资料免费下载

2024-05-15 10:16:05 0

0 电子发烧友网站提供《同步4位计数器数据表.pdf》资料免费下载

2024-05-15 10:08:34 0

0 电子发烧友网站提供《同步8位上/下计数器数据表.pdf》资料免费下载

2024-05-17 09:50:53 0

0 电子发烧友网站提供《带3态输出的同步4位上/下十进位和二进制计数器数据表.pdf》资料免费下载

2024-05-17 10:17:49 0

0 电子发烧友网站提供《同步4位上/下二进制计数器数据表.pdf》资料免费下载

2024-05-17 10:52:34 0

0 电子发烧友网站提供《同步4位二进制计数器数据表.pdf》资料免费下载

2024-05-22 09:44:43 0

0 在数字电子领域,计数器是一种用于统计脉冲信号数量的设备,广泛应用于各种数字系统和电路中。其中,同步计数器作为计数器的一种重要类型,具有其独特的工作原理和分类。本文将详细探讨同步计数器的主要类型、工作原理以及其在数字系统中的应用。

2024-05-24 14:34:28 3104

3104 在数字电子领域中,计数器是一种用于统计脉冲信号数量的重要设备。其中,同步计数器和异步计数器是两种不同类型的计数器,它们在工作原理、特性以及应用场景等方面存在着显著的区别。本文将详细探讨这两种计数器的区别,以便读者能够更深入地理解它们的工作原理和应用场景。

2024-05-24 14:36:12 7834

7834 电子发烧友网站提供《SN54ALS561A、SN74ALS561A带3态输出的同步4位计数器数据表.pdf》资料免费下载

2024-06-04 11:28:09 0

0 电子发烧友网站提供《SN74HC193-Q1 4位同步递增/递减计数器数据表.pdf》资料免费下载

2024-06-04 10:46:53 0

0 FPGA(Field-Programmable Gate Array,现场可编程门阵列)中的复位操作是设计过程中不可或缺的一环,它负责将电路恢复到初始状态,以确保系统的正确启动和稳定运行。在FPGA设计中,复位方式主要分为同步复位和异步复位两种。以下是对这两种复位方式的详细探讨。

2024-07-17 11:12:21 3320

3320 计数器同步和异步是数字电路设计中的一个重要概念,它们在很多应用场景中都扮演着关键角色。 一、计数器概述 计数器是一种常见的数字电路,它可以对输入信号进行计数,并将计数结果以数字形式输出。计数器在数

2024-07-23 11:14:02 3321

3321 74LS163 是一个十进制同步计数器,它是一个集成电路(IC),用于数字电路中进行计数操作。它是一个4位二进制计数器,但由于其设计,它可以很容易地被配置为一个十进制计数器。这意味着它可以从0计数

2024-10-18 13:54:05 3780

3780

电子发烧友App

电子发烧友App

评论