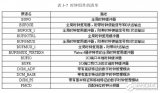

如果FPGA没有外部时钟源输入,可以通过调用STARTUP原语,来使用FPGA芯片内部的时钟和复位信号,Spartan-6系列内部时钟源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

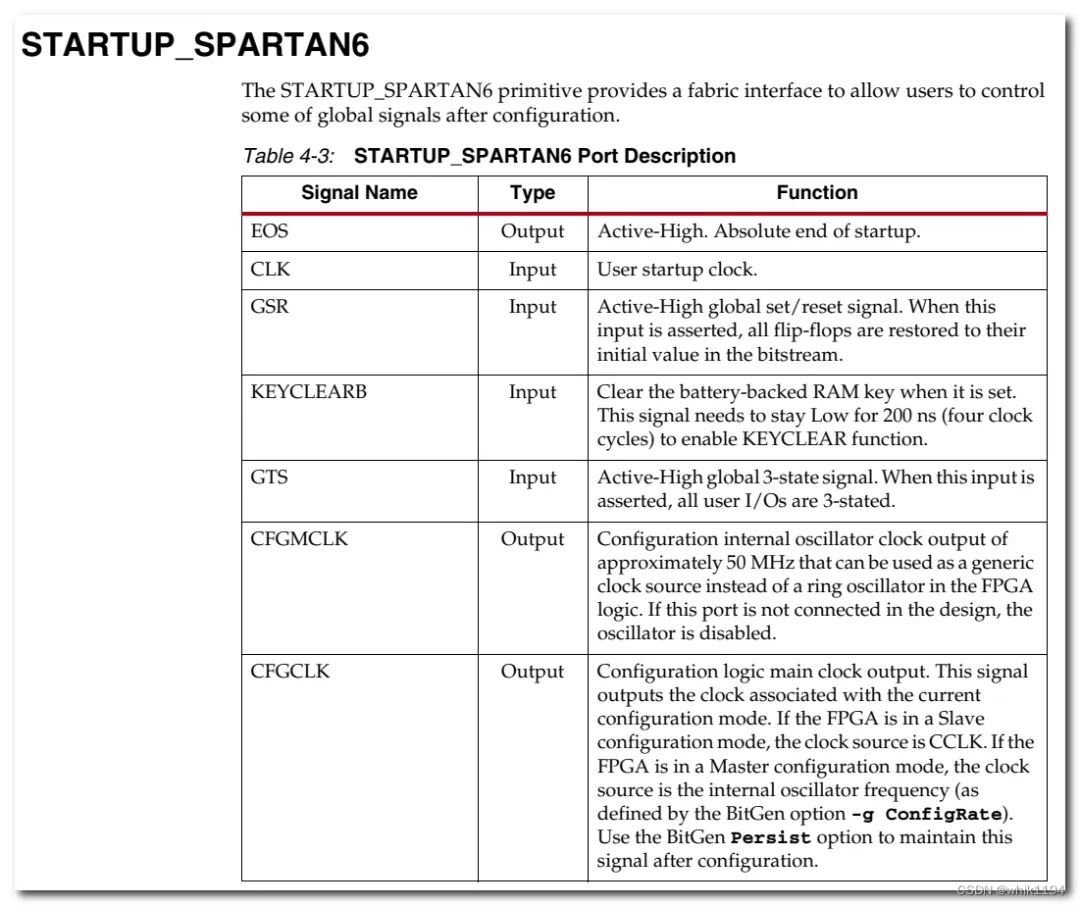

Spartan-6系列

wireclk_50m; wirerst_n; STARTUP_SPARTAN6STARTUP_SPARTAN6_inst( .CFGMCLK(clk_50m),//1-bitoutput:Configurationinternaloscillatorclockoutput. .EOS(rst_n),//1-bitoutput:ActivehighoutputsignalindicatestheEndOfConfiguration. );

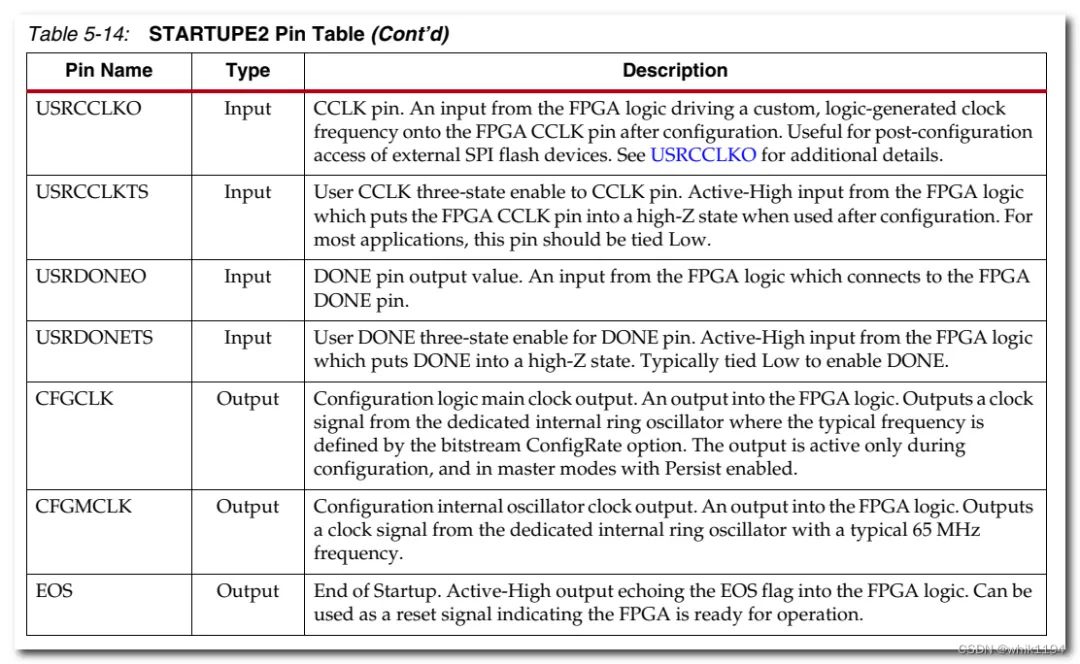

Artix-7(7系列)

wireclk_65m; wirerst_n; STARTUPE2STARTUPE2_ut0( .CFGMCLK(clk_65m),//1-bitoutput:Configurationinternaloscillatorclockoutput65MHz. .EOS(rst_n)//1-bitoutput:ActivehighoutputsignalindicatingtheEndOfStartup. );

分别可以参考文档:

UG380:Spartan-6 FPGA Configuration

UG470:7 Series FPGAs Configuration

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA芯片

+关注

关注

3文章

250浏览量

40859 -

时钟源

+关注

关注

0文章

108浏览量

16643 -

复位信号

+关注

关注

0文章

70浏览量

6753

原文标题:Xilinx FPGA芯片内部时钟和复位信号使用

文章出处:【微信号:mcu149,微信公众号:电子电路开发学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

Xilinx FPGA的GTx的参考时钟

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

发表于 09-15 09:14

•5020次阅读

Xilinx_FPGA_内部结构深入分析

个MUX。利用这种2+1的组合可以产生DDR操作,Xilinx称之为ODDR2。每个存储单元都有6个接口信号:时钟+时钟时能,数据输入+输出,置位复

发表于 08-02 22:48

在FPGA开发中尽量避免全局复位的使用?(2)

在Xilinx 的FPGA器件中,全局的复位/置位信号(Global Set/Reset (GSR))(可以通过全局复位管脚引入)是几乎绝对

发表于 02-11 11:46

•1218次阅读

Xilinx全局时钟的使用和DCM模块的使用

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其

发表于 11-22 07:09

•1.3w次阅读

FPGA的理想的复位方法和技巧

引脚类似,对 FPGA 来说往往是异步的。设计人员可以使用这个信号在 FPGA 内部对自己的设计进行异步或者同步复位。

发表于 11-22 17:03

•6306次阅读

Xilinx FPGA的同步复位和异步复位

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区

发表于 07-13 09:31

•7543次阅读

Xilinx-DCM的使用方法技巧

Xilinx-DCM的使用方法技巧(长城电源技术(深圳有限公司)-该文档为Xilinx-DCM的使用方法技巧讲解文档,是一份还算不错的参考文档,感兴趣的可以参考参考,,,,,,,,,,

发表于 09-28 12:46

•12次下载

Xilinx FPGA芯片内部时钟和复位信号使用方法

Xilinx FPGA芯片内部时钟和复位信号使用方法

评论