Xilinx Block Memory Generator(BMG)是一个先进的内存构造器,它使用Xilinx fpga中的嵌入式块RAM资源生成面积和 性能优化的内存。

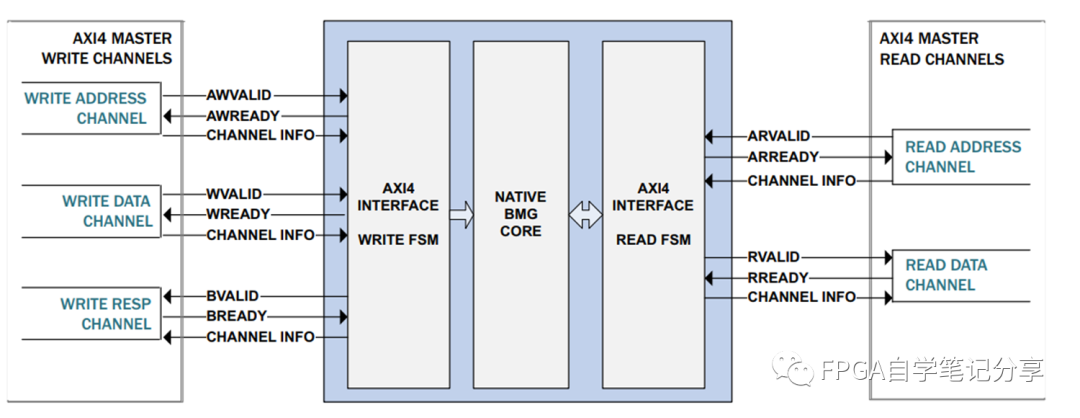

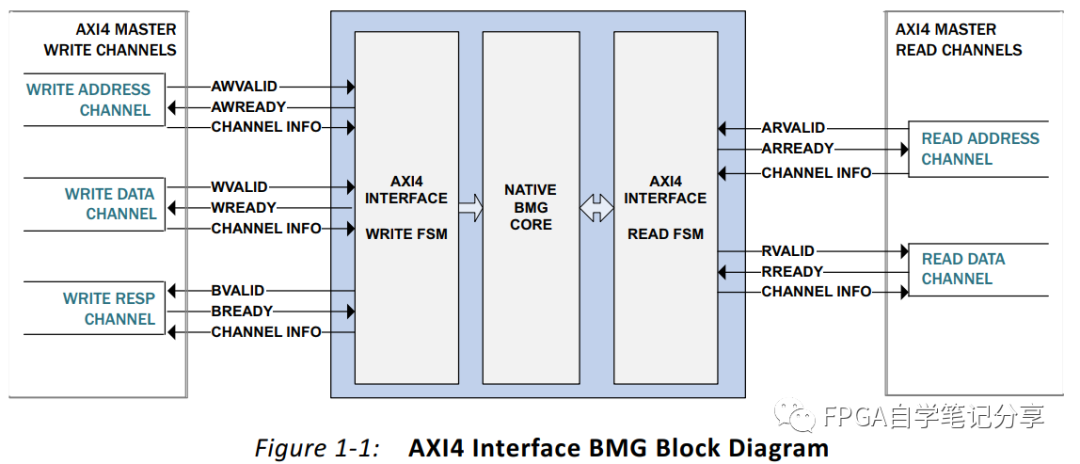

支持普通接口和AXI两种接口。BMG IP的AXI4接口配置派生自本地接口 配置,在IP中添加了一个行业标准总线协议接口。有两种可用的AXI4 接口样式:AXI4和 AXI4- lite。

功能概述:

•优化算法最小块RAM资源利用率或低功耗利用率

•可配置内存初始化

•在UltraScale™,UltraScale+™,Zynq®-7000,

Spartan®-7,Artix®-7,Kintex®-7和Virtex®-7器件上独立的byte写使能(带或不带奇偶校验)

•优化的Verilog行为模型用于仿真提速;精确的结构仿真模型用于模拟存储行为

•每个端口可选择的操作模式:WRITE_FIRST, READ_FIRST或NO_CHANGE

•SDP模式下有更低的数据宽度

•标准DOUT块RAM级联

使用普通接口时:

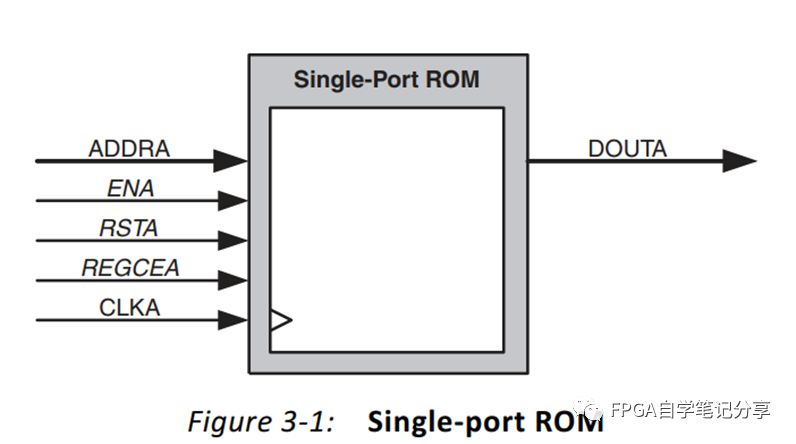

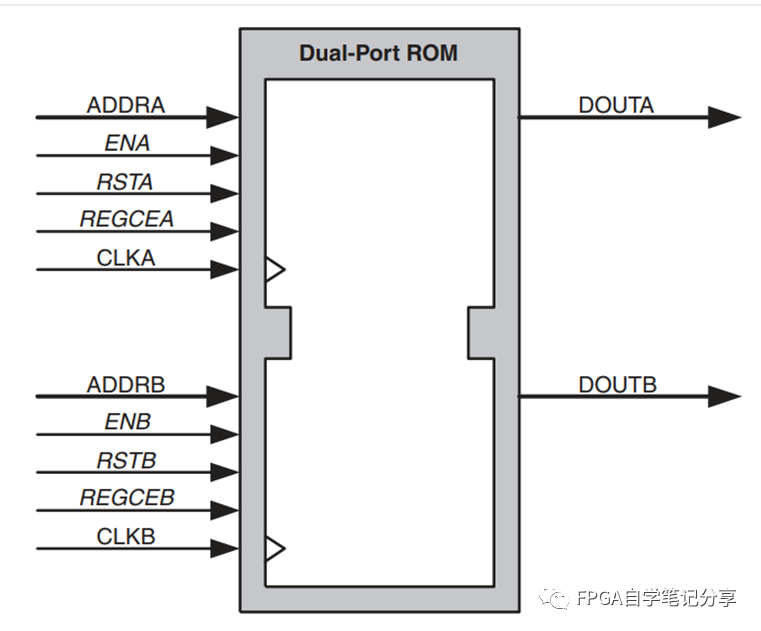

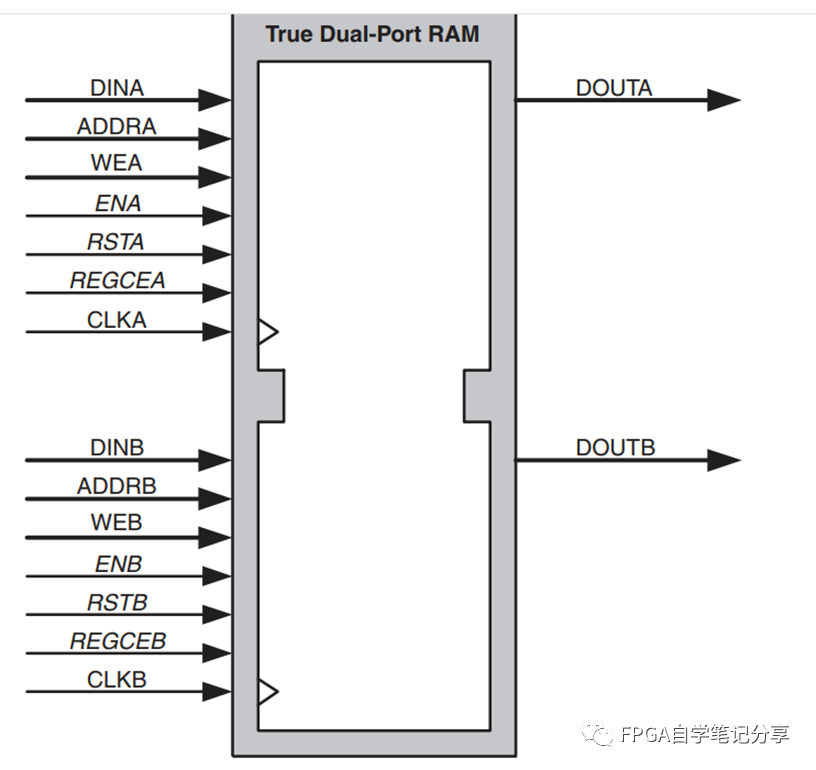

•生成单端口RAM,简单双端口RAM,真双端口RAM,单端口

ROM和双口ROM

•支持最大16M bytes的内存大小(字节大小8或9)(仅受选定部分的内存资源限制)

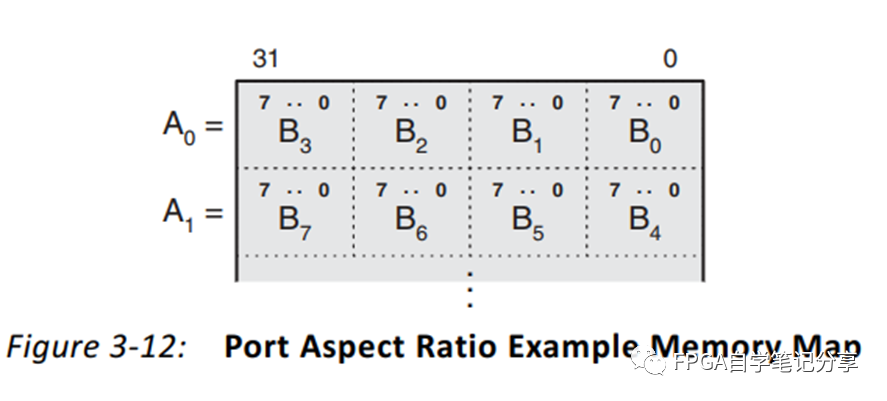

•可配置端口输入输出比

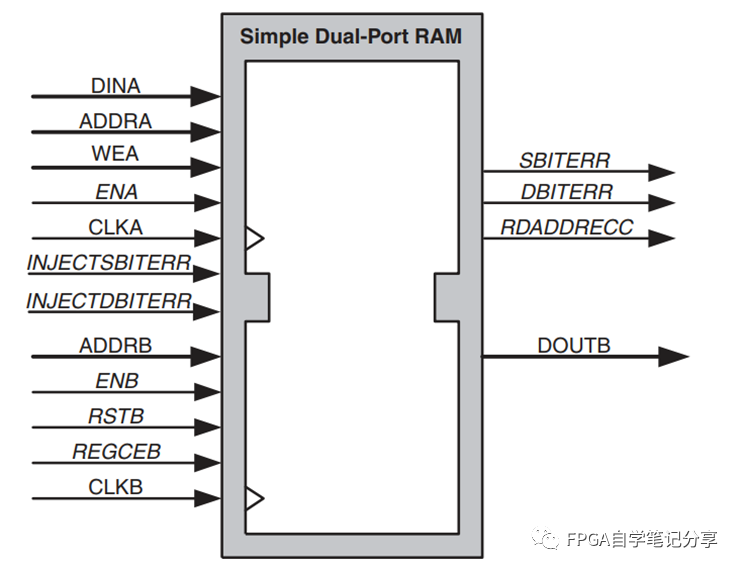

•支持内置ECC (Hamming Error Correction Capability)。错误注入引脚允许插入单位和双位错误

•支持数据宽度小于64位的软ECC (soft Hamming Error Correction)

•可选择流水线DOUT总线,以提高特定配置的性能

•在SR (Set reset)或CE的优先级之间选择输出寄存器的复位优先级

•性能高达450 MHz

使用AXI4接口时:

•支持AXI4和AXI4- lite接口协议

•符合AXI4的内存和外设从属类型

•独立的读写通道

•零延迟数据路径

•支持握手信号的寄存器输出

•INCR突发大小高达256个数据传输

•WRAP突发大小为2、4、8和16

•AXI非对齐的突发传输

•简单的双端口RAM的配置

•性能高达300Mhz

•支持数据宽度高达256位和内存深度从1到1M字(仅受选定部分的内存资源限制)

•对称输入输出

•异步active-Low复位

使用默认接口时,支持的工作模式:

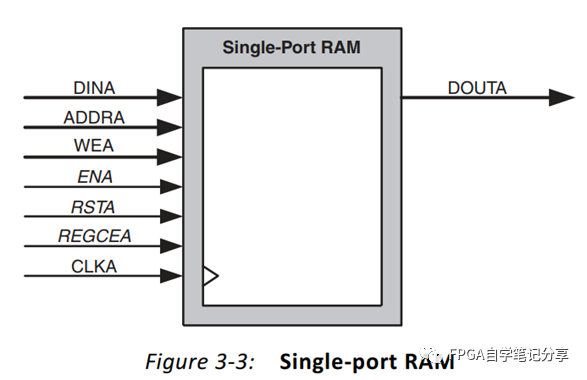

•单端口RAM

•简单的双端口RAM

•真正的双端口RAM

•单端口ROM

•双端口ROM

-

FPGA

+关注

关注

1664文章

22502浏览量

639106 -

嵌入式

+关注

关注

5209文章

20645浏览量

336925 -

Xilinx

+关注

关注

73文章

2206浏览量

131866 -

内存

+关注

关注

9文章

3234浏览量

76506

发布评论请先 登录

XILINX FPGA IP之Clocking Wizard详解

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解

Xilinx FPGA IP之Block Memory Generator AXI接口说明

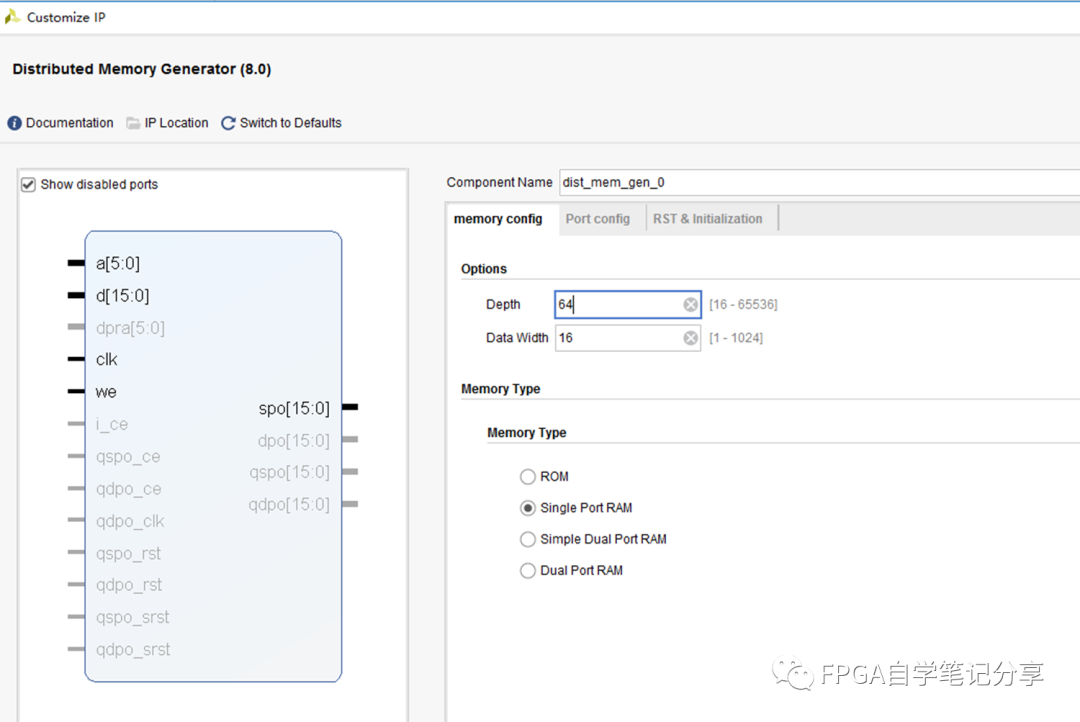

Distributed Memory Generator IP核简介

XILINX FPGA IP之AXI Traffic Generator

Xilinx FPGA IP之Block Memory Generator功能概述

Xilinx FPGA IP之Block Memory Generator功能概述

评论