总计:

方式一:普通IO口加上按键复位电路和上电自动复位电路

方式二:nCONFIG引脚输入信号作为系统复位

方式三:用其他MCU控制FPGA的上电复位,既可以将MCU的复位引脚和FPGA的复位引脚连在一起,也可以MCU单独引脚复位引脚对FPGA进行控制。

总结与讨论:

疑问:

总计:

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上电复位电路,保证程序能够正常地执行。不管是什么样的结果,这里先把一些常用的FPGA复位电路例举出来,以作公示。

方式一:普通IO口加上按键复位电路和上电自动复位电路

上图是两种复位方式的集合,可以实现上电复位和按键复位。电路图中左半部分是实现按键复位的,右图则是实现上电自动复位的。

按键复位: 默认状态电路图为高电平,当按键按下后,电路产生一个低电平的信号,即产生一个下降沿,这样的话,就可以实现低电平的复位信号了。

上电自动复位:刚上电的时候,电容导通,复位RST引脚处为低电平,当电容充满电后,RST引脚处就为高电平了。这样也产生了低电平的复位信号。

只要将相应的引脚连接至复位引脚处,就能控制电路系统的复位了。

方式二:nCONFIG引脚输入信号作为系统复位

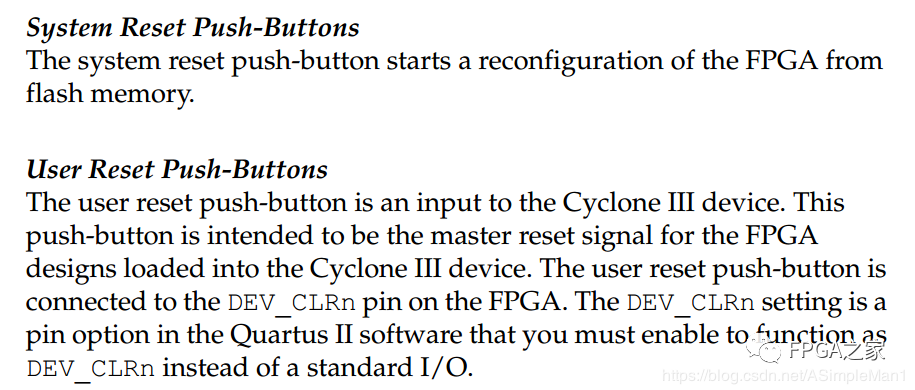

参考cycloneIII的handbook,可以发现下面这样一段话。现摘录如下:

下面则是一个很常用的复位电路,正好使用到了这部分的复位电路。电路中既有系统复位的部分,又有按键复位的部分。

具体的介绍如下,系统复位方式采用的普通的按键复位电路实现。而用户复位按钮,则是对nCONFIG引脚的控制进行复位的,这个引脚连接的是DEV_CLKn引脚,而在上面的介绍中,我们可以看到nCONFIG至少保持低电平500ns以上,就可以实现对整个cycloneIII系列FPGA的重新复位。需要注意的是,这要求QuartusII的设置中不能讲DEV_CLRn配置为普通引脚。

方式三:用其他MCU控制FPGA的上电复位,既可以将MCU的复位引脚和FPGA的复位引脚连在一起,也可以MCU单独引脚复位引脚对FPGA进行控制。

MCU控制FPGA的复位可以在方式一和方式二的方式上进行实现。

例如在底板的STM32中添加按键复位,这个复位既连接了STM32本身的复位信号,又连接了FPGA相应的复位信号引脚,这样的话,就可以达到STM32和FPGA同时复位的效果。当然你也可以使用上电自动复位电路进行实现。

还有一种方式就是,MCU引出一个引脚,控制这个引脚输入低电平,延时一段时间后再重新拉高,这样的话,就会产生一个上升沿的信号,同样可以控制FPGA复位。

总结与讨论:

总之,实现FPGA复位的方式有很多。可能不仅仅上面例举的一些。而且,上面的实现方式,可能并不是最好的,仅仅作为一种参考。

下面进行一些讨论。

FPGA在组合电路中是没有时钟信号的,这样的话,也就不可能添加所谓的复位信号,复位信号应该不是必须的。

疑问:

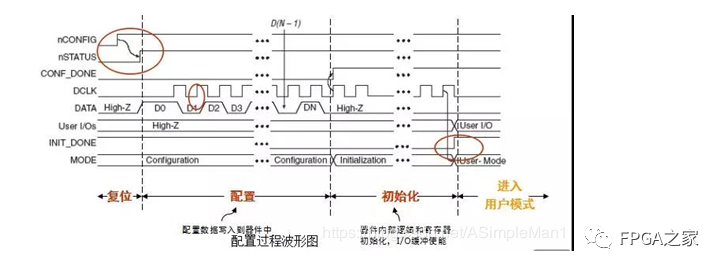

cycloneIII系列程序的下载过程如下:

(1)首先注意的nCONFIG引脚,当其由低电平进入高电平时,程序进入配置过程。

在此过程中,nSTATUS引脚也由低置高,程序进入配置过程。

波形有从低电平到高电平的跳变过程,说明进入了配置过程。

(2)然后注意的引脚是CONFIG_DOWN引脚,当其由低电平进入高电平时,程序配

置完成,进入初始化,这部分才算程序下载完毕。

这样的话,我是否可以使用CONFIG_DOWN引脚输出,连接相应的复位RST引脚,遮样的话,就可以自动的上电自动复位,而不用添加任何的辅助电路?

欢迎大家楼下一起交流

-

FPGA

+关注

关注

1603文章

21326浏览量

593230 -

复位电路

+关注

关注

13文章

308浏览量

44277 -

上电复位

+关注

关注

1文章

38浏览量

15630

发布评论请先 登录

相关推荐

FPGA中三种常用复位电路

FPGA 外置复位电路怎么设计比较好?

FPGA复位电路的设计

FPGA设计中常用的复位设计

FPGA的理想的复位方法和技巧

FPGA怎么搭复位电路 fpga复位电路设计方案

硬件设计——外围电路(复位电路)

FPGA复位电路的实现方式

FPGA复位电路的实现方式

评论