使用Verilog设计电路模块时,为什么推荐使用register out的方式?

在进行design partition时,相比register in更推荐register out,请问为什么呢?如果前后两个模块时钟域不同,register in会有什么问题?

@0431大小回:

1.为了logic level可控:因为一般大一点的工程都是多人负责的模块化设计,如果你的输出不是寄存器输出,而是组合逻辑直接输出,这样别人在衔接你这个模块的时候,根本不知道你的输出前有多少级组合逻辑级数。如果在输入的时候寄存也可以,但是这样就相当于我们把自己该做好的事情让别人来做了,所以这个时候就约定俗成的让输出都寄存。这样可以在写或者修改该模块的设计者能掌握好自己设计的逻辑级数.

2.为了约束:以FPGA设计为例,在后续做implementation的时候,有的时候发现wns比较差是因为fanout比较高,比如某些关键使能信号驱动了多个大位宽数据。这个时候可以在顶层模块例化连接找到这个信号,显式限制(max_fanout = xxx)。但是在vivado里这个语句只适用于寄存器,而不适用于wire形变量,所以我猜测还有一些其他的显示约束方法对寄存器输出有强需求。

@顽猴溜溜:

你这个问题,必须从物理实现的角度来解释。

1.如果fanout目标一个在东、一个在西,那么register out很容易clone成东西两个register,来优化布线,且不会引入任何额外的延时。register in的优化就没这么简单了。

2.如果fanout目标成千上万(high fanout),那么register out很容易clone成多组register,来降低fanout优化布线,且不会引入任何额外的延时。register in的优化就没这么简单了。

3.如果连线过长需要引入额外的延时,那么register out很容易插入repeater或pipeline,而register in的处理相对更困难。

4.register out的时序行为更容易描述,且不会出现毛刺,所以工艺迁移更容易,标准IP也更喜欢。

-

寄存器

+关注

关注

31文章

5618浏览量

130386 -

时钟

+关注

关注

11文章

1999浏览量

135224 -

Register

+关注

关注

0文章

36浏览量

14428

原文标题:使用Verilog设计电路模块时,为什么推荐使用register out的方式?

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT DDR2 Register SSTUB32S868BHLFT 器件分析

VSCODE+ESP-IDF运行\'\'hello world\",partition-table进程卡住

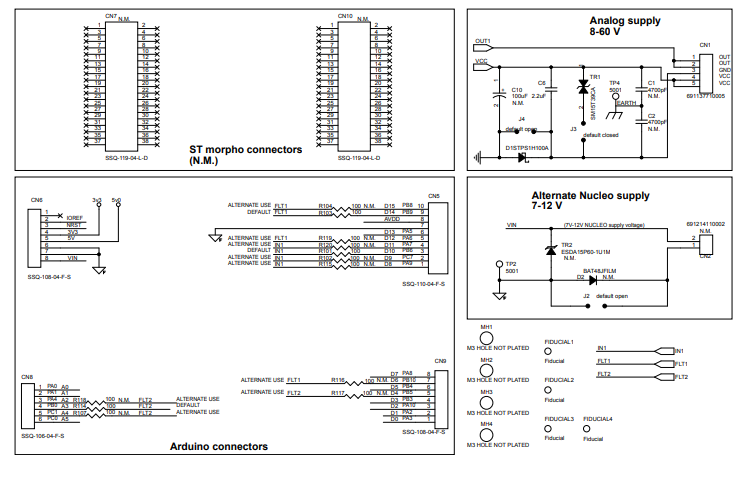

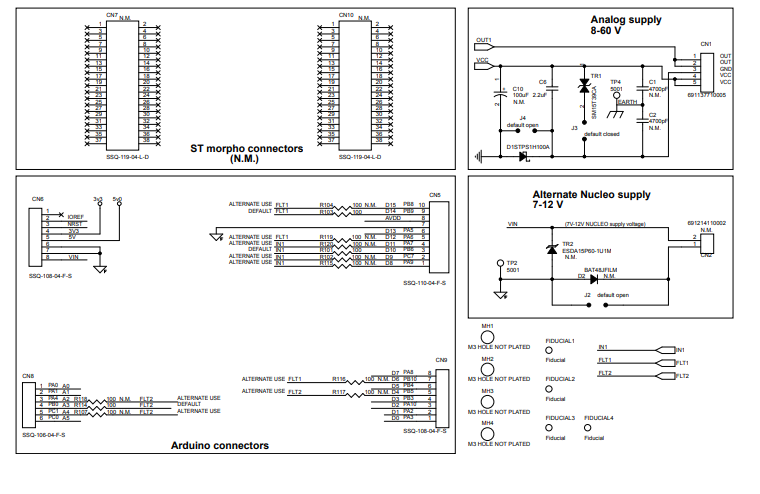

STMicroelectronics X-NUCLEO-OUT04A1扩展板数据手册

ST X-NUCLEO-OUT03A1扩展板技术详解与工业应用指南

STM32工业数字输出扩展板X-NUCLEO-OUT06A1技术详解

STM32工业数字输出扩展板X-NUCLEO-OUT05A1技术解析与应用指南

利用蜂鸟E203搭建SoC【2】——外部中断扩展与验证

STMicroelectronics X-NUCLEO-OUT09A1/OUT19A1扩展板数据手册

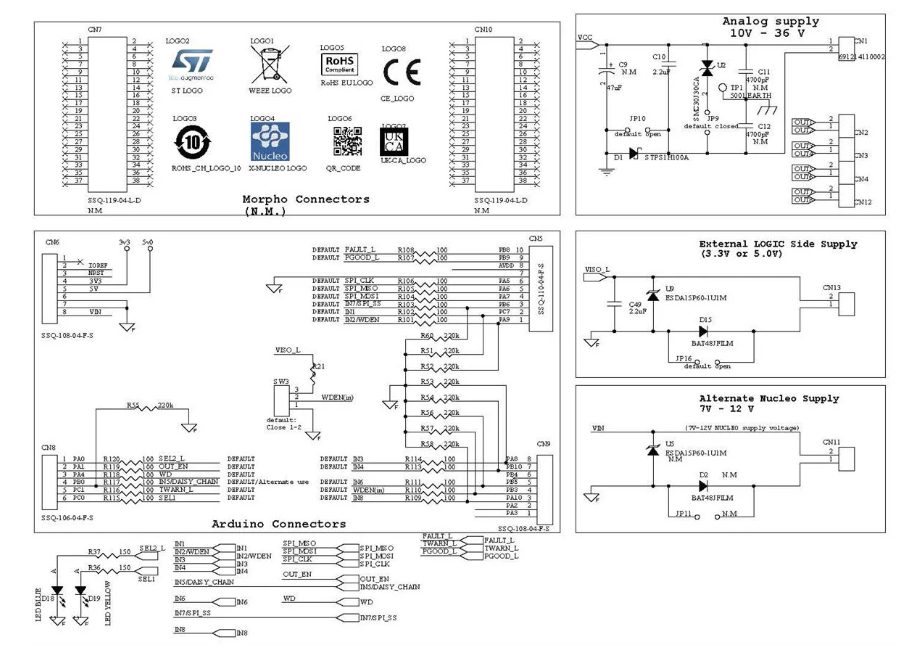

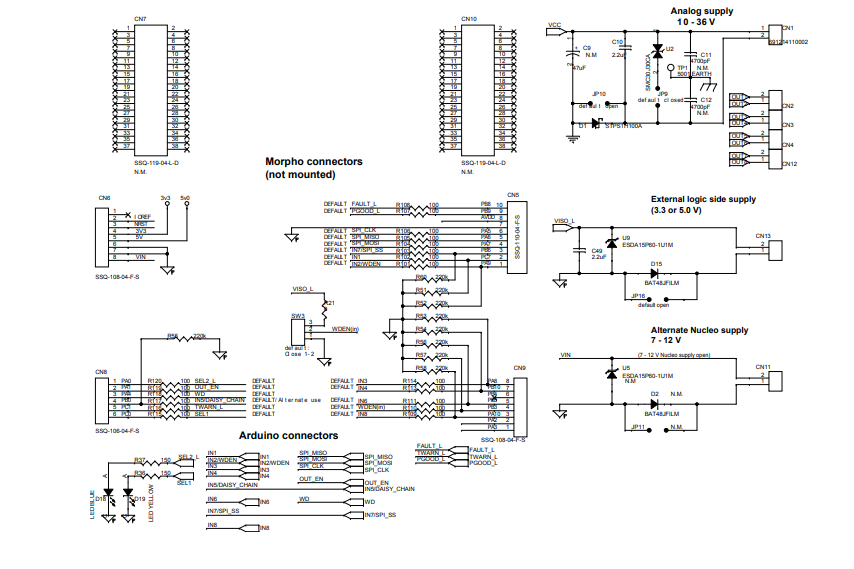

X-NUCLEO-OUT01A2工业数字输出扩展板技术解析

X-NUCLEO-OUT16A1工业数字输出扩展板技术解析与应用指南

X-NUCLEO-OUT17A1工业数字输出扩展板技术解析与应用指南

进行design partition时,为什么推荐使用register out的方式

进行design partition时,为什么推荐使用register out的方式

评论