在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台

2011-10-21 16:13:51 1270

1270

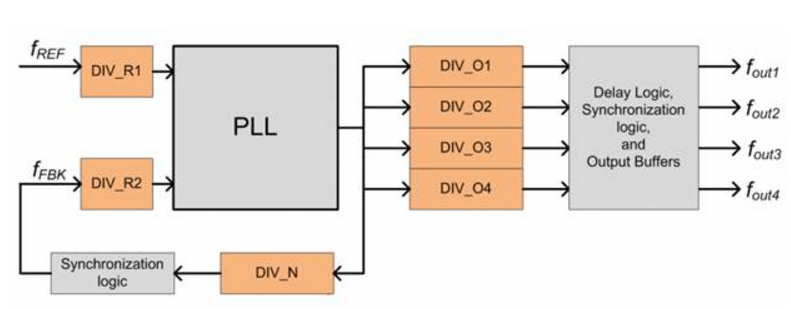

致力于提供功率、安全、可靠与高性能半导体技术产品的领先供应商美高森美公司(Microsemi Corporation,纽约纳斯达克交易所代号:MSCC)宣布推出双通道ZL30240和单通道ZL30241时钟发生器产品,用于包括通信设备、企业路由器和交换、网络存储设备和服务器等多种应用。

2013-04-23 13:42:44 1208

1208 针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2013-11-28 18:49:00 12149

12149

的高性能时钟发生器系列产品,特别针对10/25/100G应用提供业界最高集成度的时钟解决方案。新型Si5332时钟系列产品利用Silicon Labs经过验证的MultiSynth小数时钟合成技术,提供

2017-09-26 12:24:08 9289

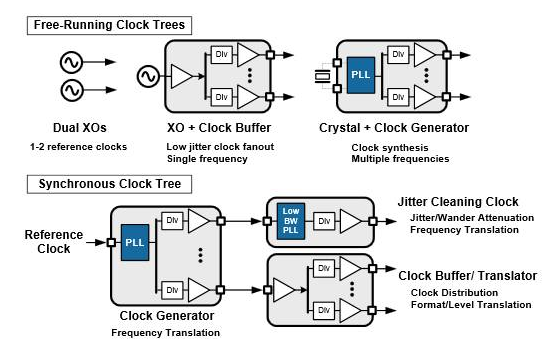

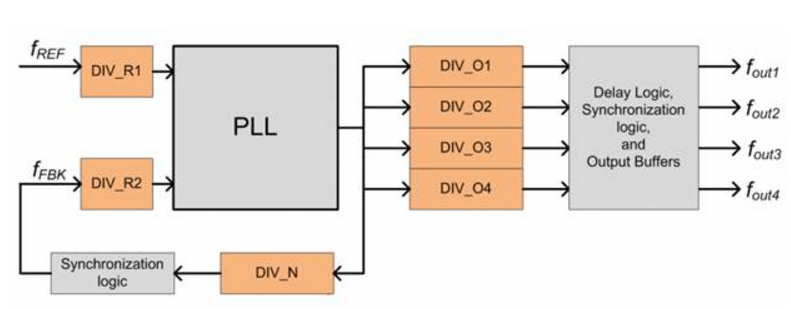

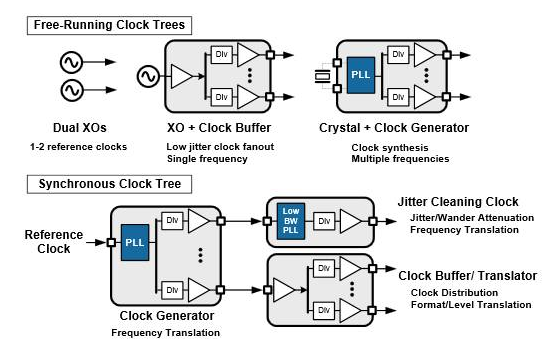

9289 在高性能应用中,例如通信、无线基础设施、服务器、广播视频以及测试和测量装置,当系统集成更多功能并需要提高性能水平时,硬件设计就变得日益复杂,为系统提供参考时序的板级时钟树也走向这种趋势。在进行时钟

2017-10-31 09:45:13 5550

5550

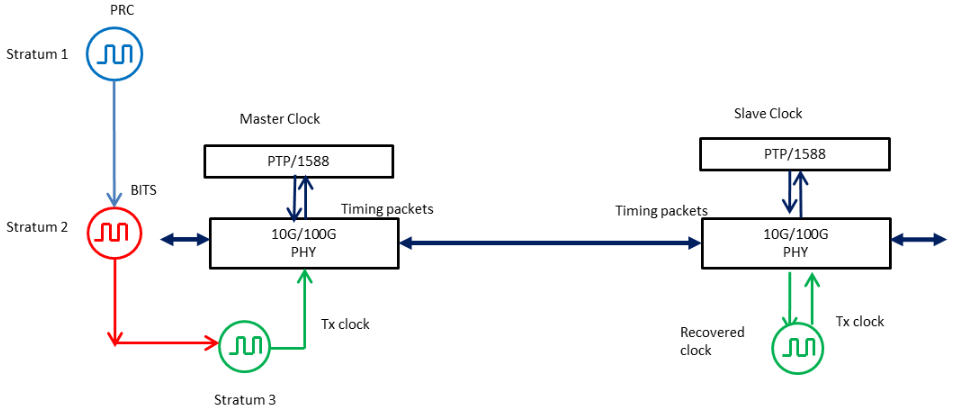

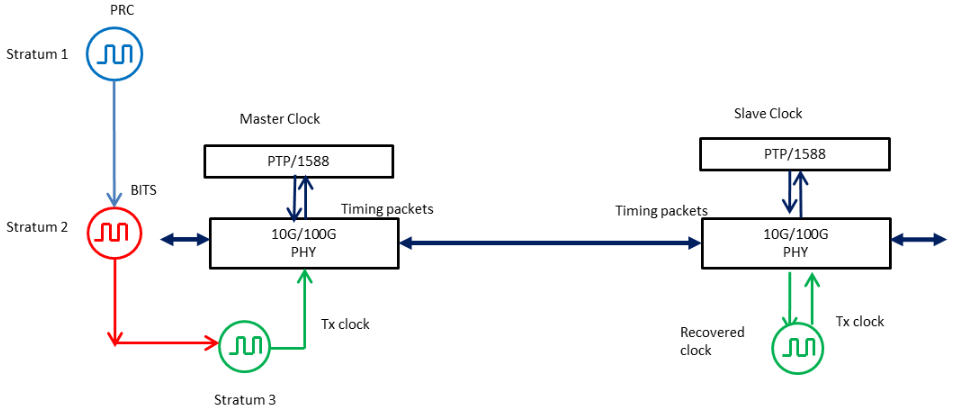

同步以太网是一种采用以太网链路码流恢复时钟的技术, 简称SyncE。同步以太网通过从串行数据码流中恢复出发送端的时钟,从而实现网络时钟同步。但SyncE不能提供时间同步。

2020-05-12 09:24:02 1945

1945

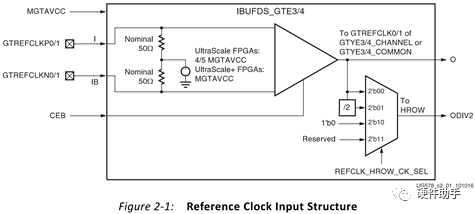

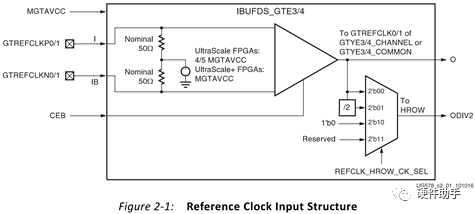

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。 参考时钟的模式 参考时钟可以配置为输入模式也可以是输出模式,但是在运行期间不能切换。作为

2020-11-14 11:39:15 13866

13866

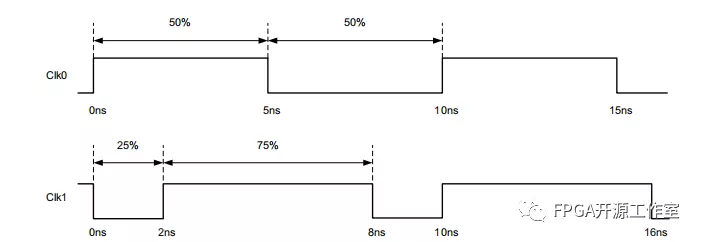

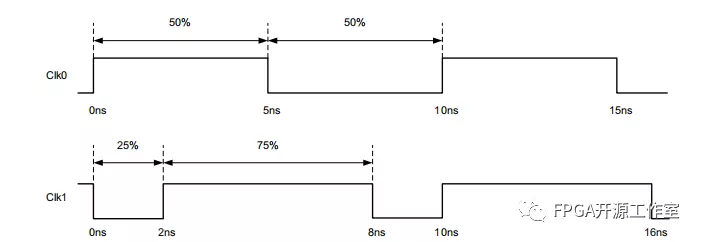

1. 时钟介绍 在数字设计中,时钟代表从寄存器(register)到寄存器可靠传输数据的时间基准。Xilinx Vivado集成设计环境(IDE)时序引擎使用ClocK特征计算时序路径要求,并通过

2020-11-29 10:51:45 5359

5359

7系列FPGA拥有丰富的时钟资源。各种缓冲器类型、时钟输入管脚和时钟连接,可以满足许多不同的应用需求。选择合适的时钟资源可以改善布线、性能和一般FPGA资源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA时钟资源通过专用的全局和区域I/O和时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏移和抖动过滤等功能。非时钟资源,如本地布线,不推荐用于时钟功能。

2022-07-28 09:07:34 1276

1276 。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期

2023-07-24 11:07:04 655

655

通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配

2023-08-31 10:44:31 1032

1032

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

2023-09-15 09:14:26 1956

1956

新推出的精密时序主时钟,搭配网关时钟和最快速的高性能边界时钟,增强5G移动网络的相位保护。

2020-04-22 14:32:03 711

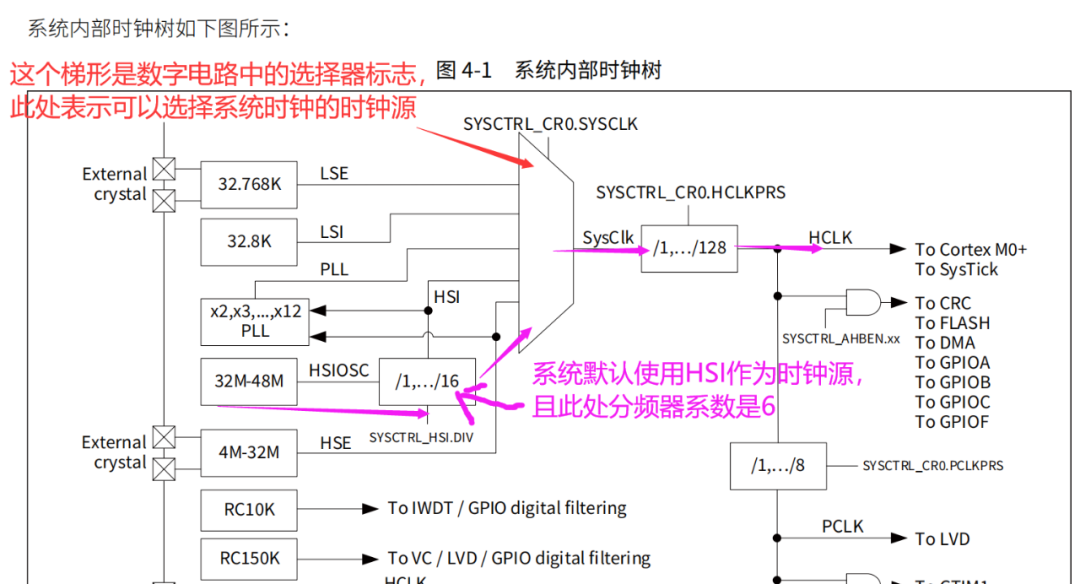

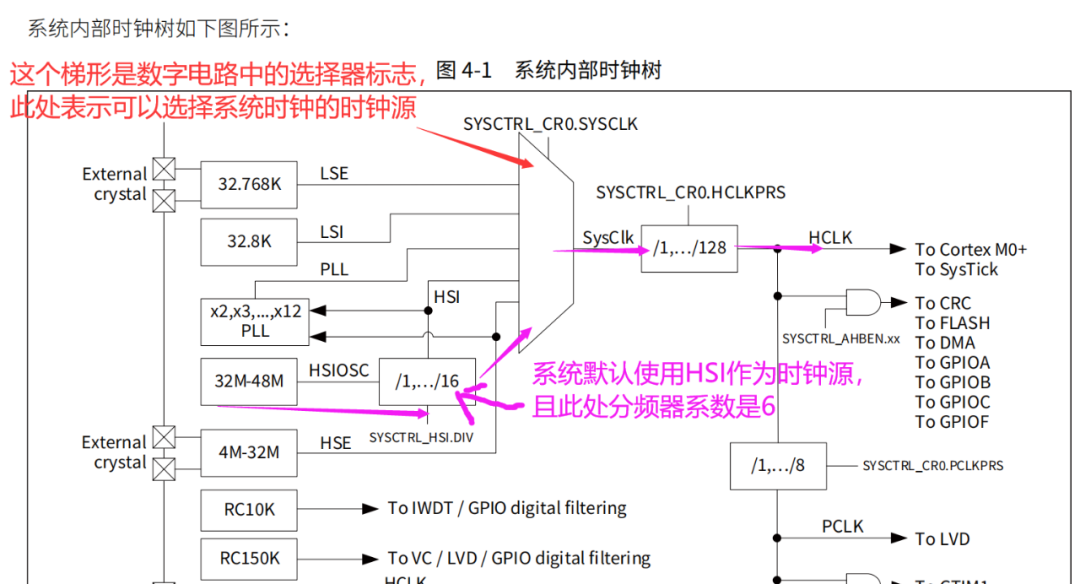

711 学习STM32的同学知道,STM32有好多时钟,如32.768Khz,8Mhz,被时钟树搞迷糊了,下面一一解析。HSE:高速外部时钟信号(4--16Mhz常用的为8Mhz)HSI:高速内部时钟信号

2017-04-27 16:34:26

嗨,我想了解7系列收发器的Kintex xc7k325tffg900-2 FPGA。https://www.xilinx.com/support/documentation/user_guides

2020-05-11 08:09:08

引言: 我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xilinx 7系列FPGA给出相关参考,给FPGA硬件开发人员提供使用。通过本文,可以了解到

2021-05-28 09:23:25

系列有哪些主要特性/优势? Kintex UltraScale系列产品的主要优势来自于UltraScale在架构上的重要创新,包括: o 类似ASIC时钟功能,实现可扩展性、高性能和低动态功耗

2013-12-17 11:18:00

时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等

2019-08-12 06:50:43

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

的主要缺点是,您放弃了实现dc、地震、音频和更高带宽应 用的绝对最高可能性能所需的自定义和优化。在急于重用和完 成设计的过程中,往往会牺牲精确性能。其容易忽略和忽视 的一个主要方面是时钟。在本文中,我们将讨论时钟的重要性, 并为正确设计高性能转换器提供指导。

2021-01-27 07:27:36

。一般的频谱分析仪的噪底高于高性能时钟缓冲的噪底。正确测量时钟缓冲的相噪和附加抖动需要专业的信号分析仪。图5 国产厂商无锡有容微电子时钟缓冲GM50101的相位噪声测试图图5是国产厂商无锡有容微电子高性能

2022-06-08 12:54:33

时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等

2018-08-27 09:46:58

对于广大初次接触STM32的读者朋友(甚至是初次接触ARM器件的读者朋友)来说,在熟悉了开发环境的使用之后,往往“栽倒”在同一个问题上。这问题有个关键字叫:时钟树。众所周知,微控制器(处理器)的运行

2011-10-21 14:36:05

Aurix系列单片机时钟系统有哪些特点

2024-02-04 06:48:15

,FPGA上的全局时钟管脚用完了就出现不够用的情况。FPGA全局时钟约束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

LPC1768时钟解析:

2016-12-29 17:41:01

STM32系统架构基础名词有哪些呢?STM32时钟系统有哪些性能呢?

2021-12-14 07:49:07

Xilinx Virtex 4 和高性能时钟合成器 LMX2531 来满足 9 位 ENOB 高速数字转换器的系统要求。 特性2 个 GSPS 模数转换通道大于 9 位 ENOB 超宽输入频率范围面向测试和测量系统的低成本双通道高速数字转换器原型

2022-09-20 07:01:22

ZN-81CCG高性能高级维修电工技能培训考核装置有什么特点?

2021-10-20 06:15:11

单元每个7系列的FPGA都有最高24个时钟管理单元(CMTs),每个时钟管理单元都包含一个混合时钟管理(MMCM)部分和一个锁相环(PLL)。混合模式时钟管理器和锁相环有很多相同的特点,例如都能实现

2016-11-01 15:52:18

我有一个关于多个Xilinx芯片时钟的问题。我正在审查另一位数字工程师的设计。有多个机箱,每个机箱都有自己的Xilinx芯片(XC9500)。一些Xilinx芯片正在与其他芯片进行交互。但是,每个

2019-01-09 10:41:26

基于V7的高性能PCIe信号处理板是什么?基于V7的高性能PCIe信号处理板有哪些主要功能?基于V7的高性能PCIe信号处理板有哪些应用?

2021-06-25 06:21:15

老化效应抖动ClockEdge 确实是 STA 的补充, ClockEdge 将成为您的时钟签核工具。所有设备老化模型均由您的代工厂提供。作为 ClockEdge 性能的一个例子,它运行在一个有

2022-11-04 11:08:00

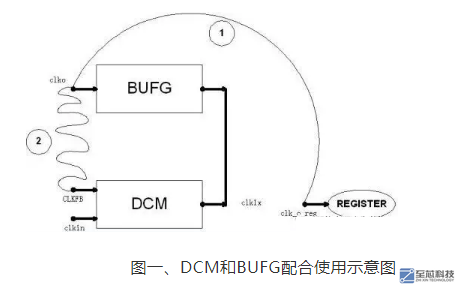

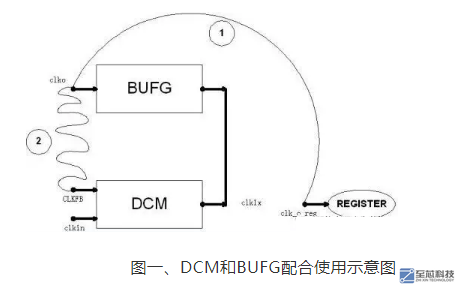

个数字时钟管理模块(DCM)。与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

2019-10-22 06:01:34

您好请教一下 10MHz的参考时钟clkref进入 要使一个板子上的FPGA(Xilinx zynq 7020)和ADC(AD9211)同步,FPGA工作和ADC的工作频率都是256MHz现在方案有

2018-08-02 09:02:02

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

请大神指教,fpga提供的pll有最低时钟输出限制,请问有pll之外的什么方式输出高性能时钟?

2013-08-26 10:53:39

嗨,我在级联模式下使用Xilinx DCM(数字时钟管理器),使用6.144 MHz时钟生成48 kHz时钟。但是,由于我的设计相当大(在区域内),这种配置无法满足时序约束并对整个设计产生影响。因此

2019-03-25 14:09:18

描述适用于 GSPS 数据转换器的低成本、高性能时钟解决方案。此参考设计讨论如何使用低噪声频率合成器 TRF3765 为 4 GSPS 模数转换器 (ADC12J4000) 生成采样时钟。实验展示了

2018-08-16 06:56:42

X12XX系列实时时钟的特点及应用:

2009-05-22 13:25:24 18

18 系统时钟源的比较选择及高性能PLL的发展趋势安森美半导体公司 供稿在所有电子系统中,时钟相当于心脏,时钟的性能和稳定性直接决定着整个系统的性能。典型的系统时序

2009-12-20 09:28:06 31

31 无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖

2009-07-06 18:37:55 449

449

安森美时钟管理产品系列增加新的时钟和数据驱动IC

应用于绿色电子产品的首要高性能、高能效硅方案供应商安森美半导体(宣布扩充公司的时钟驱动器系列,推出NB7L

2010-02-01 13:42:09 866

866 MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 778

778 讨论了物理设计中时钟网络的设计技术,并以现有的CPU时钟网络的为例,介绍了高性能CPU的时钟网络设计技术。

2011-12-27 15:28:56 46

46 高性能的时钟同步系统是任何通信传输领域必不可少的,并且在很大程度上决定了整个传输系统的性能,可称之为传输系统的心脏 时钟同步系统是基于锁相环路的同步原理,跟踪一个高

2011-12-28 16:39:39 41

41 ADI最近宣布收购Multigig,Inc.,这家小型私营企业位于加利福尼亚州圣何塞,专注于高度创新的高性能时钟技术。

2012-04-18 09:19:40 565

565 DLL在_FPGA时钟设计中的应用,主要说明DLL的原理,在Xilinx FPGA中是怎么实现的。

2015-10-28 14:25:42 1

1 当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢? BUFIO是IO时钟网络,顾名思义

2017-02-08 05:31:40 2048

2048

谈到数字逻辑,谈到FPGA设计,每位工程师都离不开时钟。这里我们简单介绍一下xilinx 7 系列中的时钟资源。时钟设计的好坏,直接影响到布局布线时间、timing的收敛情况,FPGA的时钟

2017-02-08 05:33:31 561

561

1. Xilinx 时钟资源 xilinx 时钟资源分为两种:全局时钟和第二全局时钟。 1. 全局时钟资源 Xilinx 全局时钟采用全铜工艺实现,并设计了专用时钟缓冲与驱动结构,可以到达芯片内部

2017-02-09 08:43:41 1315

1315 我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

2017-02-10 18:40:10 5965

5965

PLL),再到Virtex-6基于PLL的新型混合模式时钟管理器MMCM(Mixed-Mode Clock Manager),实现了最低的抖动和抖动滤波,为高性能的FPGA设计提供更高性能的时钟管理功能。

2017-02-11 09:14:01 1030

1030

现议价。不幸的是,相对较少信息已出现在晶体电路和工程师们常常把水晶电路视为一种黑色艺术,最好留给几个熟练的从业者(见盒子),关于石英水晶。 事实上,最高性能的晶体时钟电路要求各种复杂的考虑和微妙实现技术。然而,

2017-05-05 11:38:25 14

14 时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。

2017-08-30 11:04:04 4285

4285

高性能CPU的时钟网络设计

2017-10-30 15:28:58 23

23 树结构 针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

2017-11-22 07:09:36 8891

8891

作为一种高性能、低成本的线卡时钟解决方案,LMK04800 可以实现传统的 SDH/SONET 系统时钟和分组交换网络中的同步以太网时钟频率的灵活转换,同时提供 150fs 级别的低抖动性能,满足

2017-11-28 16:57:56 5

5 STM32各类系列时钟

2018-01-25 16:40:35 3

3 分享到务来管理时钟节拍,而且采用哈希散列表机制来进一步减少时钟节拍处理过程所花费的时间。本文讨论μC/OS—II在时钟节拍管理方面的不足,并介绍μC/OS—III中的高效时钟节拍 管理机制 。

2018-04-09 11:29:00 1270

1270

目前对时钟频率还能代表处理器性能的话题在网上议论纷纷,情况有点复杂,自从英特尔在2008年推出睿频加速技术能动态、自动地对处理器超频后,这一技术就越来越普及了,在市场上销售的处理器都能根据能耗

2018-04-28 16:42:56 7158

7158 有些FPGA学习者,看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时钟管理单元。 1、DCM概述 DCM内部是DLL(Delay Lock Loop结构

2018-05-25 15:43:53 7884

7884

ADI研讨会:高性能时钟: 解密抖动

2019-08-20 06:05:00 1656

1656 时钟信号是任何数字电路设计的基础,而时钟源是雷达、通信、测试仪器等电子系统实现高性能指标的关键,很多电子设备和系统功能的实现都直接依赖于高性能的时钟源。文中选择时钟合成器MPC92433+FPGA

2019-10-03 11:02:00 981

981

美国马萨诸塞州诺伍德市 - 全球领先的信号处理应用高性能半导体公司ADI公司今天推出了一系列时钟IC,可满足当今高性能电子应用中最严格的信号处理要求,如作为无线基础设施收发器,仪器仪表和宽带基础设施

2019-09-15 16:52:00 3289

3289

时钟设备设计使用I2C可编程小数锁相环(PLL),可满足高性能时序需求,这样可以产生零PPM(百万分之一)合成误差的频率。高性能时钟IC具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统

2020-11-03 10:40:00 0

0 时钟篇 选用全局时钟缓冲区(BUFG)作为时钟输入信号,BUFG是最稳定的时钟输入源,可以避免误差。 只用一个时钟沿来寄存数据,使用时钟的两个沿是不可靠的,如果时钟沿“漂移”,就会导致时序错误

2020-12-11 10:26:44 1482

1482 Xilinx7系列FPGA包括四个FPGA系列,它们都是为最低功耗而设计的,以使一个通用设计能够跨系列扩展以获得最佳的功率、性能和成本。斯巴达-7系列是7系列产品中密度最低、成本最低的入门级产品

2020-12-10 14:20:00 18

18 本章介绍了高云半导体FPGA 产品的时钟资源,包括专用的时钟输入、缓冲区和布线资源。时钟的基础设施提供了一系列低电容、低偏移互连线,非常适合承载高频信号,最大限度地减少时钟偏差和提高性能,可应用于所有的时钟信号。

2020-12-10 14:20:13 9

9 全局时钟资源是一种专用互连网络,它可以降低时钟歪斜、占空比失真和功耗,提高抖动容限。Xilinx的全局时钟资源设计了专用时钟缓冲与驱动结构,从而使全局时钟到达CLB、IOB和BRAM的延时最小。

2020-12-29 16:59:35 8

8 源同步接口设计特别有用。7系列器件中的I/O Bank与时钟区域的大小相同。为了理解区域时钟是如何工作的,理解区域时钟信号的信号路径是很重要的。7系列设备中的区域时钟资源和网络由以下路径和组件组成: 时钟输入I/O I/O时钟缓冲器:BUFIO 区域时

2021-03-22 09:47:30 4631

4631

引言:7系列FPGA具有多个时钟路由资源,以支持各种时钟方案和要求,包括高扇出、短传播延迟和极低的偏移。为了最好地利用时钟路由资源,必须了解如何从PCB到FPGA获取用户时钟,确定哪些时钟路由资源

2021-03-22 10:16:18 4353

4353

引言:从本文开始,我们陆续介绍Xilinx 7系列FPGA的时钟资源架构,熟练掌握时钟资源对于FPGA硬件设计工程师及软件设计工程师都非常重要。本章概述7系列FPGA时钟,比较了7系列FPGA时钟

2021-03-22 10:25:27 4326

4326 晶振是数字电路设计中非常重要的器件,时钟的相位噪声、频率稳定性等特性对产品性能影响很大。本文基于可编程晶振SI570,就Xilinx FPGA收发器输入参考时钟的硬件设计及FPGA软件设计给出设计案例,供大家参考。

2021-04-07 12:00:44 3914

3914

AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器

2021-04-30 09:48:42 13

13 从NRZ到PAM4,信号传输技术的变革推动了通信和数据中心领域数据传输速率的重大飞跃,人们对于数据传输速率的需求正在以几何倍数增长着。同时,高性能服务器和网络基础设施中对于时钟产品的要求也日益严苛

2021-05-24 10:07:45 1649

1649 时钟设计方案在复杂的FPGA设计中,设计时钟方案是一项具有挑战性的任务。设计者需要很好地掌握目标器件所能提供的时钟资源及它们的限制,需要了解不同设计技术之间的权衡,并且需要很好地掌握一系列设计实践

2021-06-17 16:34:51 1528

1528

解析MSP430系统时钟资源

2021-09-26 11:39:09 1

1 RTX51tiny 复杂应用---时钟、温度显示、按键解析

2021-11-21 13:06:03 25

25 STM32为什么要有复杂的时钟系统首先STM32 本身非常复杂,外设非常的多,但是并不是所有外设都需要系统时钟这么高的频率,比如看门狗以及 RTC 只需要几十 k 的时钟源即可。同一个电路,时钟越快

2021-11-23 18:21:38 8

8 MSP432P401R时钟系统MSP432的时钟模块(CS),个人理解msp432最特色的功能应该是超低功耗和高性能的组合。432系列的时钟系统主要有三个方面:1、硬件时钟–时钟

2021-12-16 16:54:39 5

5 第二篇文章——STM32电源、复位、时钟电源管理电源电压调节器可编程电压监测器(PVD: Programmable voltage detector )低功耗模式复位Cortex-M3的复位信号

2022-01-05 14:25:10 10

10 HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

2022-06-13 10:07:26 1481

1481 xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13:48 2592

2592 什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock Buffer,通常是指基于非PLL

2022-10-18 18:36:54 18409

18409

在5G网络应用中,对于网络节点的时钟要求非常高,网络设备需要稳定的时钟

2023-03-15 11:12:46 900

900 HMC7043是一种高性能时钟缓冲器,用于为具有并行或串行(JESD204B型)接口的高速数据转换器分配超低相位噪声参考。

2023-05-31 10:47:57 1637

1637 。高性能时钟芯片是电子设备不可或缺的重要元器件,在服务器、交换机、基站、医疗设备中广泛应用。但是,该领域此前一直为国外厂商所垄断。极景微依托创始团队在超低抖动锁相环技术及创新时钟电路方案领域的深厚积累,成功

2021-11-22 09:47:49 1792

1792

本章针对CW32F030C8T6的时钟树进行详细解析,续第一章启动文件的相关讲解。

2023-08-17 11:42:22 961

961

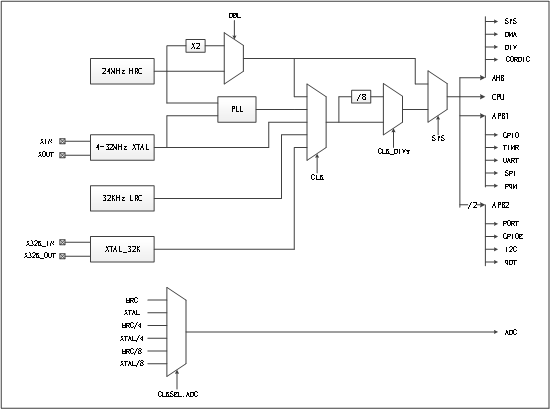

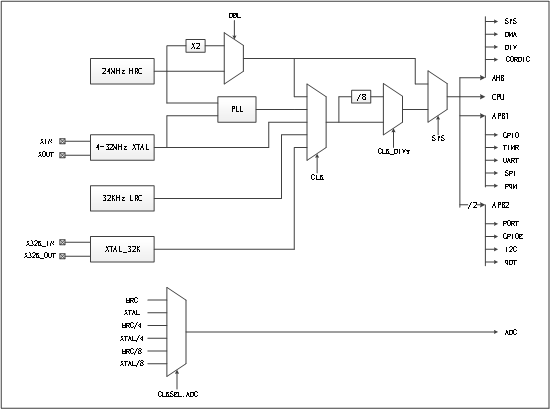

如何配置SWM系列系统时钟?

2023-09-18 16:35:11 362

362

高性能20路PCIe时钟缓冲器新品推介SQ82100PCI-Express(PCIe)是一种高速串行计算机扩展总线标准,主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。目前服务器

2023-12-20 08:19:38 240

240

电子发烧友网站提供《RX和RA系列主时钟电路和子时钟电路设计指南.pdf》资料免费下载

2024-02-19 10:20:19 0

0 国芯思辰SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。SYSREF

2024-02-19 09:41:40

电子发烧友App

电子发烧友App

评论