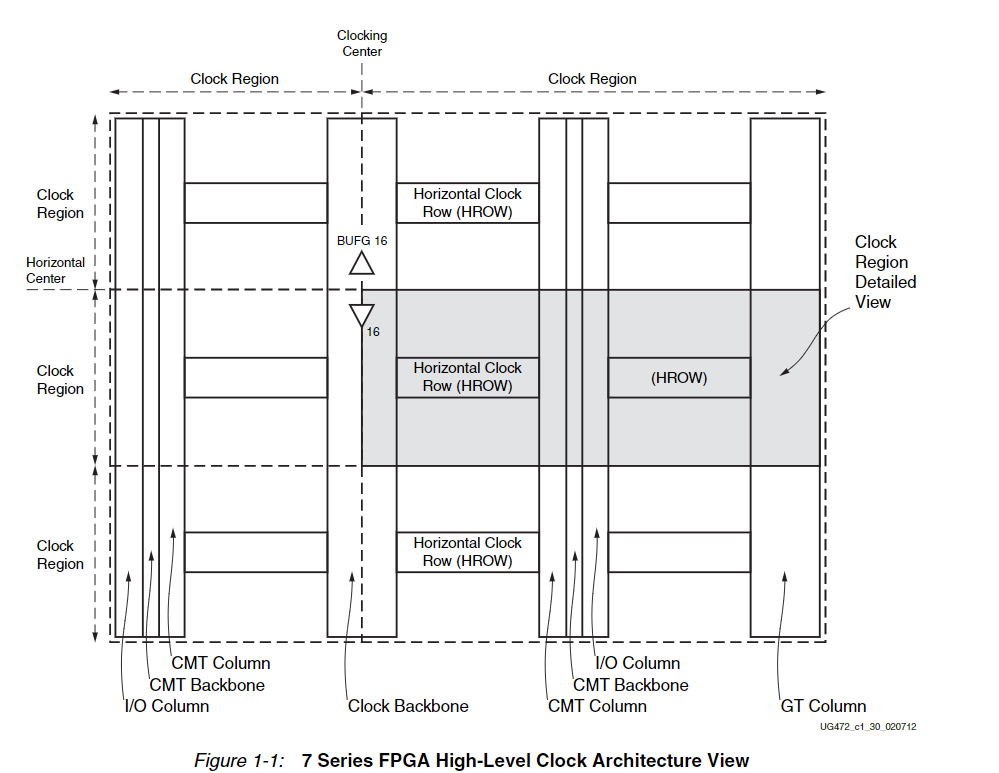

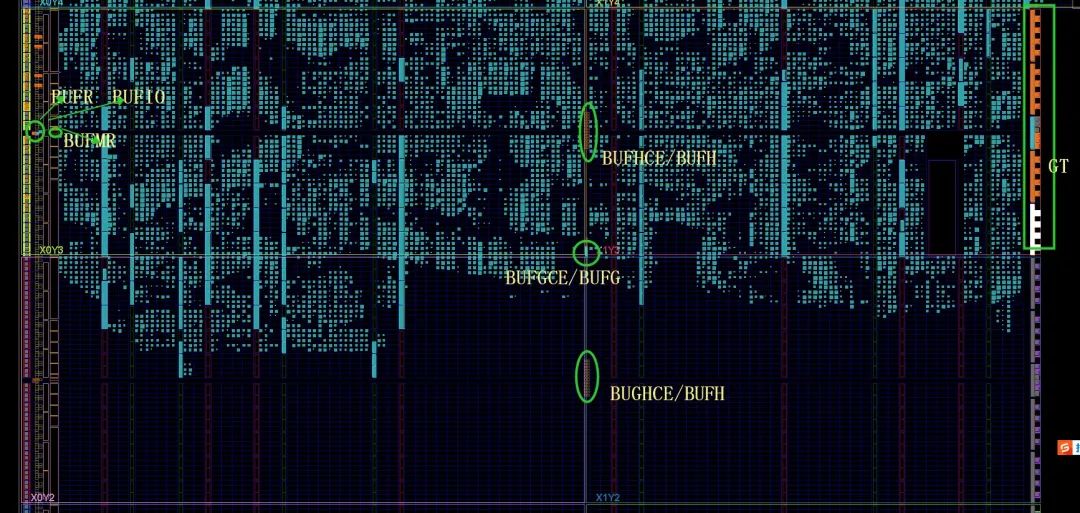

xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

Clock Region:FPGA 内部分成了很多个时钟区域。

Horizontal Center:FPGA被 Horizontal Center 分成上下两个部分,每个部分包含16个 BUFG 。

Clock Backbone:全局时钟线的主干道,将 FPGA 分成了左右两部分,所有的全局时钟布线均要从此经过。

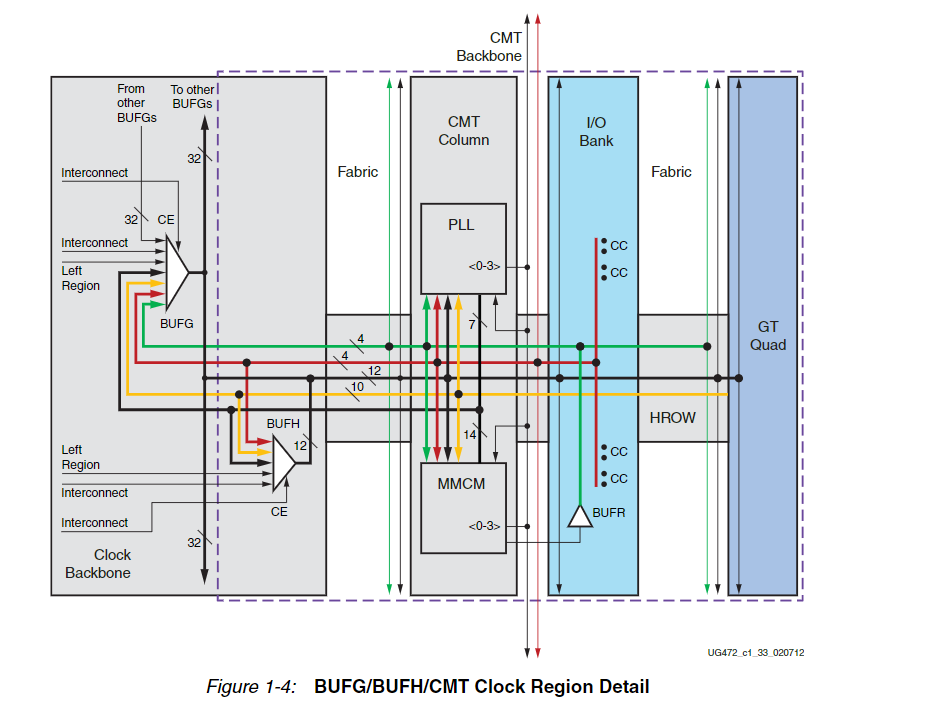

HROW:水平时钟线,从水平方向贯穿每个时钟区域的中心区域,将时钟区域分成上下完全一致的两部分。全局时钟线进入每个时钟区域的逻辑资源时,必须经过水平时钟线。

I/O Column:外部信号/时钟输入管脚。

CMT Backbone:对于相邻时钟区域的时钟布线,可以不使用珍贵的全局时钟网络,而使用每个时钟区域都包含的 CMT Backbone 通道。

CMT Column:每个时钟区域都包含一个CMT,一个CMT由一个MMCM和一个PLL组成。

GT Column:内含高速串行收发器。

总结来说,FPGA 实际上就是被分成很多个大小一样时钟区域,每个时钟区域既可单独工作又可通过全局时钟 Clock BackBone 统一工作,同时水平相邻的时钟区域又可通过 HROW 来统一工作,上下相邻的时钟区域又可通过 CMT Backbone 统一工作。

Xilinx 7系列时钟区域

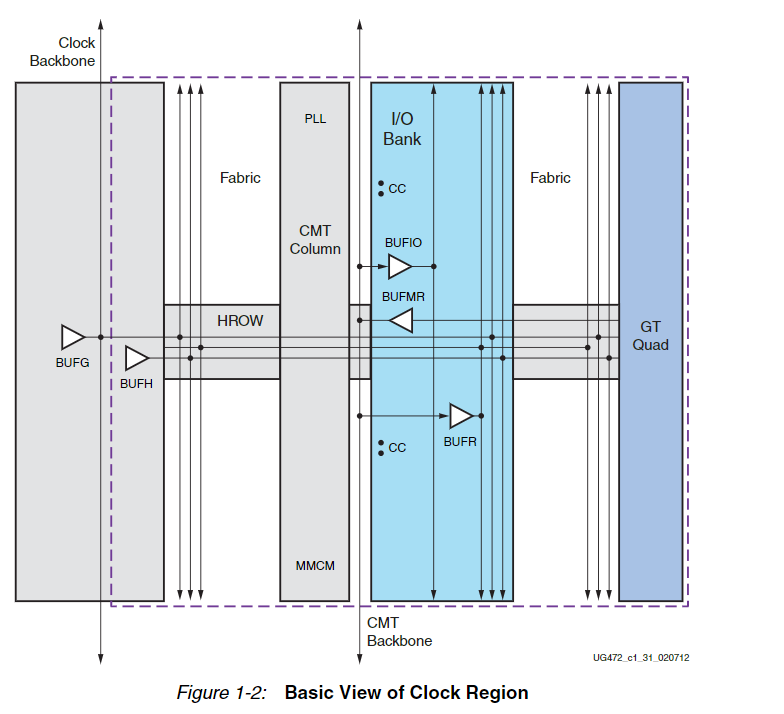

BUFG 即为全局时钟缓冲器,从图上看到,其输出时钟通过 Clock Backbone 可以到达任意一个时钟区域,而且 BUFG 通过 HROW 到达时钟区域内部的每个逻辑单元。

BUFH 即为水平时钟缓冲器,它相当于一个功能受限的 BUFG ,其输出时钟只能通过 HROW 在左右相邻的时钟区域内工作。

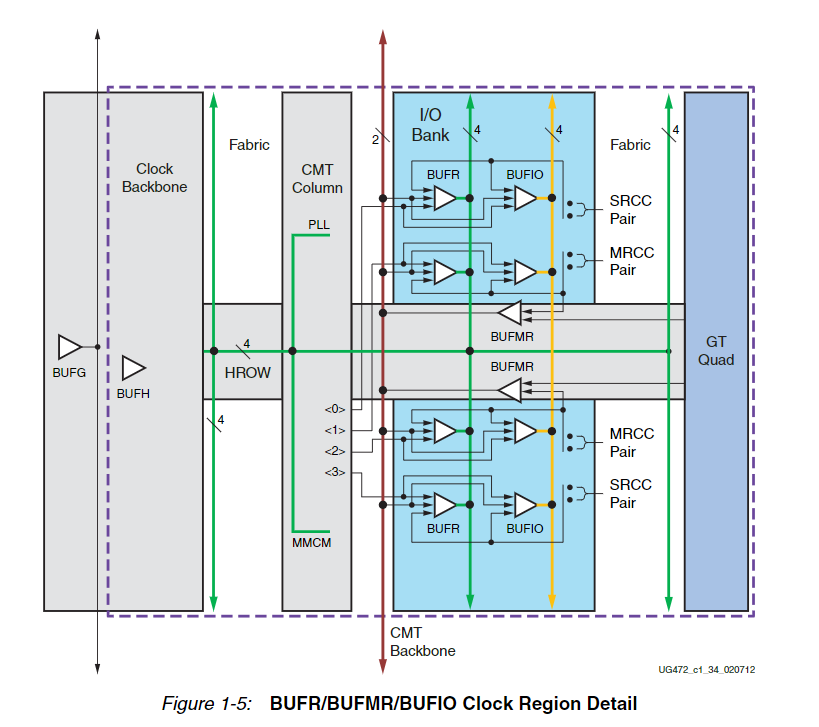

BUFIO 即为 IO 时钟缓冲器,其输出时钟只能作用在一个时钟区域的 IO 寄存器处,无法在 FPGA 内部逻辑使用。

BUFR 即为区域时钟缓冲器,其输出只能作用在一个时钟区域,相当于 BUFH 的 mini 版。

BUFMR 即为多区域时钟缓冲器,其输出作用在本时钟区域,还可以通过 CMT Backbone 作用在上下相邻两个时钟区域。

MMCM、PLL 即时钟管理模块,用来消除时钟的延迟、抖动以及产生各种不同频率的时钟。

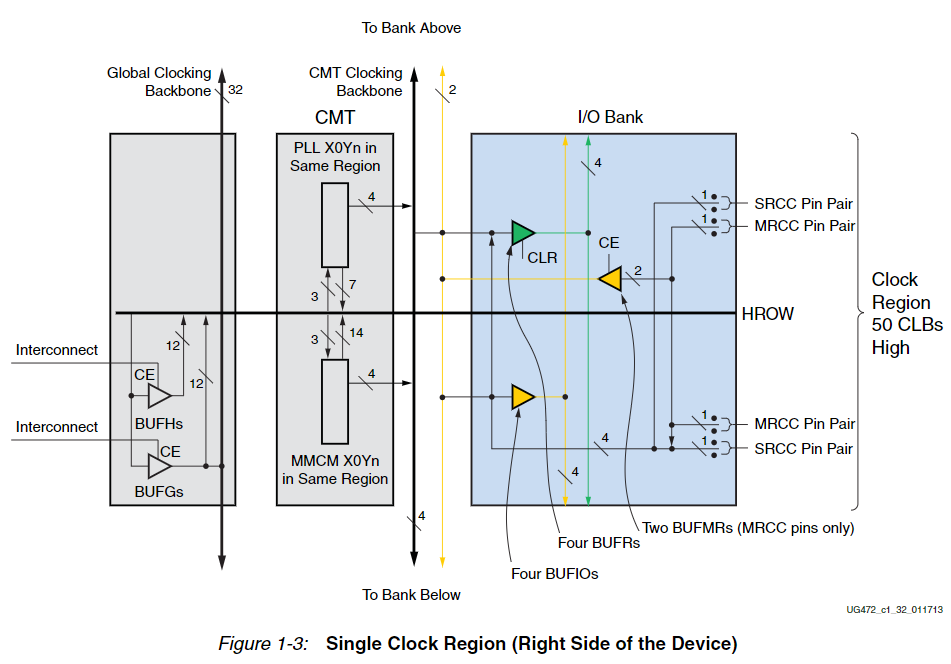

CC 即为外部时钟输入管脚,其管脚在内部可以连接到 BUFG、BUFR、BUFIO、BUFH、MMCM、PLL 等,看具体的应用具体连接。下图所示为更为细致的 CC 管脚连接图。一个时钟区域有 4 对 CC 管脚,其中 2 对 SRCC ,2 对 MRCC 。SRCC 作为区域时钟使用时,只能连接本时钟区域的 BUFR 和 BUFIO 。而 MRCC 则还可以通过BUFMR作用在上下相邻的时钟区域。

Xilinx 7系列时钟详细描述

xilinx 7 系列 FPGA 里面,一个 CMT 包含一个 PLL 和一个 MMCM。Ultra 系列 FPGA 里面包含两个 PLL 和 一个 MMCM 。所以本文以 7 系列介绍。

1.IO 的时钟分布

2.芯片上位置

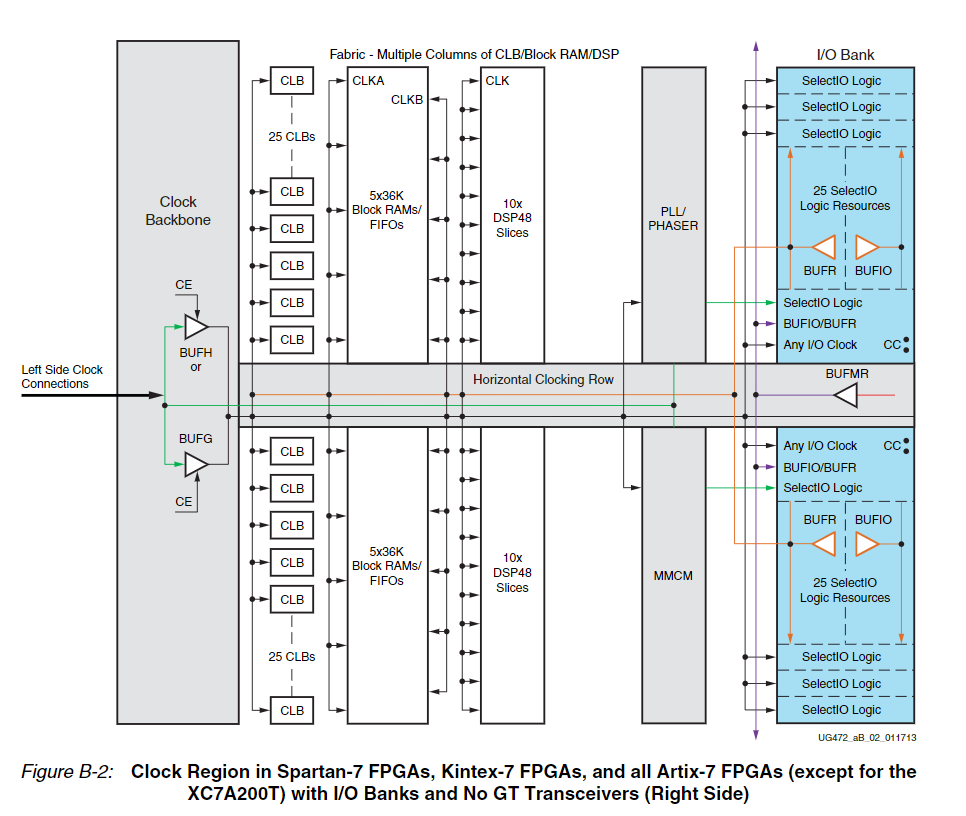

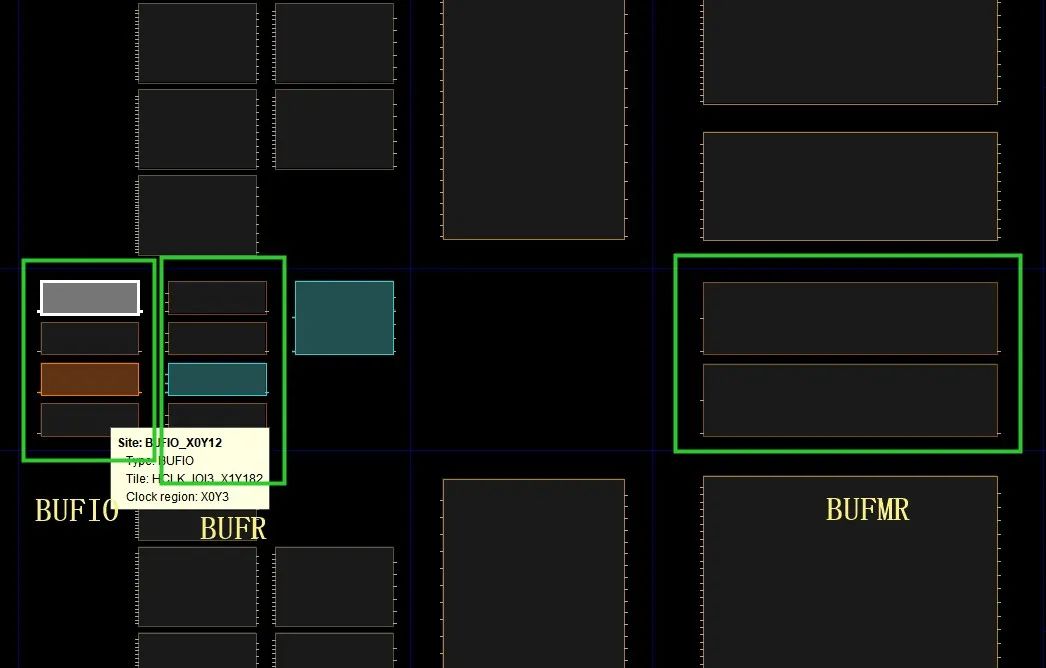

BUFG、BUFR、BUFH、BUFIO 在芯片上所处位置如下图所示

将BUFR、BUFIO、BUFMR 放大如下图所示

3.驱动能力对比

结合 BUF 在芯片上的位置,以及下图不难理解BUFG、BUFH、BUFR、BUFIO的驱动能力强弱。

物理管脚 IO

SRCC:外部差分时钟或者单端时钟驱动,只能作用于本区域时钟:4个BUFIO、4个BUFR、本时钟区域的CMT以及上下相邻时钟区域的CMT、16个BUFG、本时钟区域以及水平相邻时钟区域的BUFH。

MRCC:外部差分时钟或者单端时钟驱动,只能作用于本区域时钟:4个BUFIO、4个BUFR、2个BUFMR、本时钟区域的CMT以及上下相邻时钟区域的CMT、16个BUFG、本时钟区域以及水平相邻时钟区域的BUFH。

FPGA 芯片内部

BUFIO:在相同的时钟区域内,其可以被 MRCC、SRCC、MMCM 的 CLKOUT0~3、CLKFBOUT 驱动,还可以被本时钟区域以及上下相邻区域的 BUFMR 驱动;其只能驱动本时钟区域内的 ILOGIC、OLOGIC。

BUFR:在相同时钟区域内,其可以被MRCC、SRCC、MMCM的CLKOUT0~3、CLKFBOUT驱动,还可以被本时钟区域以及上下相邻区域的BUFMR驱动;其能驱动本时钟区域内的CMT、本时钟区域内所有逻辑单元、以及16个BUFG(不推荐)。

BUFMR:其只能被本时钟区域的MRCC以及某些GT时钟驱动;其能驱动本时钟区域以及上下相邻区域的BUFIO、BUFR。

BUFG:其能被每个时钟区域内的SRCC、MRCC、CMT、GT、BUFR(不推荐)、其他BUFG;其可以驱动CMT、GT时钟、其他BUFG、FPGA内任何逻辑单元、BUFH。

BUFH:其能被本时钟区域以及左右相邻时钟区域内的SRCC、MRCC、CMT、BUFG、GT时钟驱动;其能驱动本时钟区域的CMT、GT时钟、以及本时钟区域内的所有逻辑单元。

GT时钟之RXUSERCLK、TXUSERCLK:其能被任何BUFG、以及本时钟区域内的BUFH驱动;其只能驱动专用的串行收发器模块。

GT时钟之RXOUTCLK、TXOUTCLK:其被专用的串行收发器模块驱动;其能驱动BUFG、相同时钟区域内的CMT、BUFMR、BUFH以及相邻时钟区域内的BUFH。

MGTREFCLK:其被外部MGT时钟源驱动;其能驱动BUFG、相同时钟区域内的CMT、BUFMR、BUFH以及相邻时钟区域内的BUFH。

CMT(PLL&MMCM):其能被BUFG、SRCC(本时钟区域以及上下相邻时钟区域)、MRCC(本时钟区域以及上下相邻时钟区域)、GT(本时钟区域)、BUFR(本时钟区域或者上下相邻时钟区域加上BUFMR)、BUFMR、MMCM/PLL.CLKOUT0~3驱动;其能驱动BUFG、相同时钟区域内的BUFIO、BUFR、BUFH以及水平相邻的时钟区域的BUFH、MMCM/PLL。

审核编辑 :李倩

-

FPGA

+关注

关注

1664文章

22513浏览量

639625 -

Xilinx

+关注

关注

73文章

2208浏览量

131993

原文标题:参考链接

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

Xilinx器件封装全方位指南:设计与应用要点解析

浅谈FPGA的时钟输入要求

深入剖析TPS650864:Xilinx MPSoCs和FPGA的理想电源管理方案

FPGA时序收敛的痛点与解决之道——从一次高速接口调试谈起

Xilinx FPGA输入延迟原语介绍

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

使用Xilinx 7系列FPGA的四位乘法器设计

Xilinx FPGA串行通信协议介绍

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

E203工程源码时钟树解析

一文详解xilinx 7系列FPGA配置技巧

FPGA的定义和基本结构

xilinx的FPGA时钟结构

xilinx的FPGA时钟结构

评论