本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟,并且探讨

2013-09-26 14:34:31 3258

3258

不够的情况下有可能会造成 FIFO 的溢出。本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟。

2013-09-29 10:05:45 2100

2100

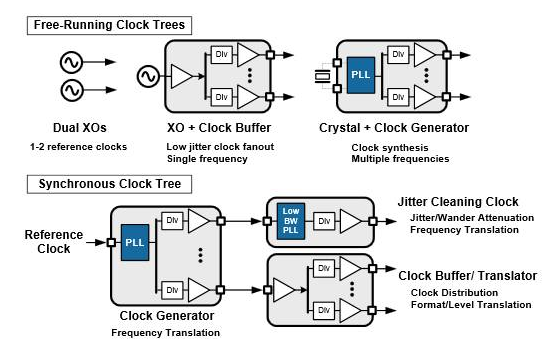

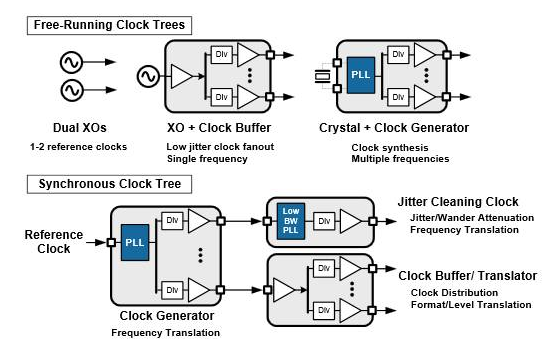

在高性能应用中,例如通信、无线基础设施、服务器、广播视频以及测试和测量装置,当系统集成更多功能并需要提高性能水平时,硬件设计就变得日益复杂,为系统提供参考时序的板级时钟树也走向这种趋势。在进行时钟

2017-10-31 09:45:13 5550

5550

GMII、SGMII和SerDes的区别和联系? GMII和SGMII区别,上一篇已经介绍了,这一篇重点介绍SGMII和SerDes区别。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29959

29959

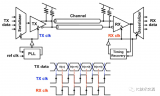

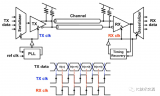

SerDes是串化(Serializer)和解串(Deserializer)的简称,下图给出了PHY的简图。发送端发送并行数据,时钟由ref_clk经过PLL锁相环振出的时钟提供,经过差分对信号传输至接收端,通过CDR恢复时钟并解串数据。

2023-08-16 17:19:23 2740

2740

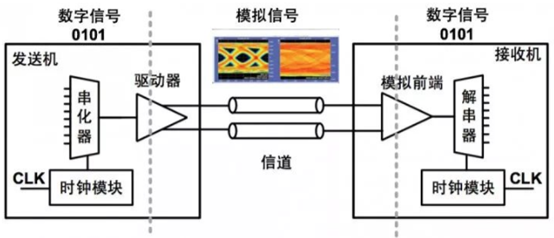

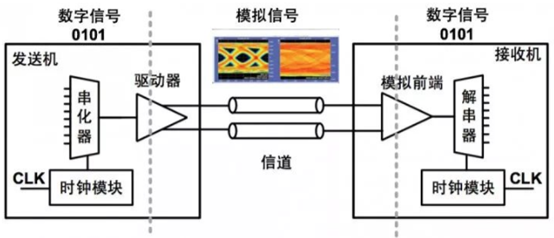

SerDes是SERializer(串行器)/DESerializer(解串器)的简称,是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

2023-11-14 09:32:39 2479

2479

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

2024-01-04 09:04:02 495

495

亲爱的Xilinx论坛,我正在实现基于SERDES协议的序列化传输。我需要在Kintex7上接收8个差分对,这些差分对承载由另一个Kintex7串行化的64位字,主时钟为100MHz。将托管FPGA

2020-03-17 09:53:11

/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道

2019-05-29 17:52:03

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中最让人头晕的当属于SerDes协议。百度百科这样解释,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

到Serial RIO,…等等,都是在借助SerDes来提高性能。SerDes是非常复杂的数模混合设计,用户手册的内容只是描述了森林里面的一棵小树,并不能够解释SerDes是怎么工作的。SerDes怎么...

2021-07-28 07:02:12

SerDes的发送端TX的均衡原理是什么?怎样利用高速接口SerDes去实现芯片间信号的有线传输?

2021-06-17 07:15:16

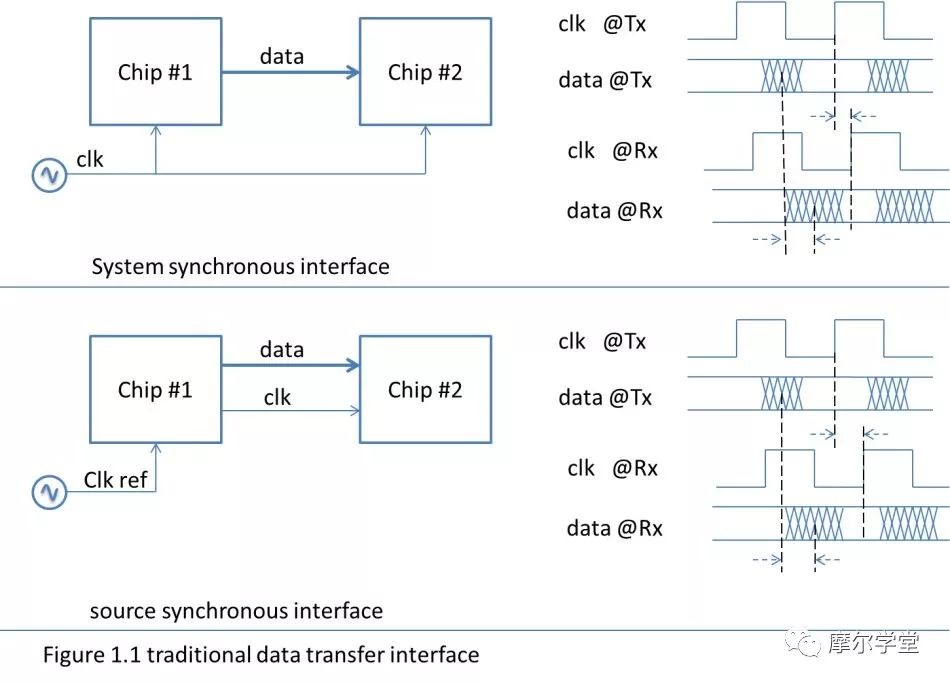

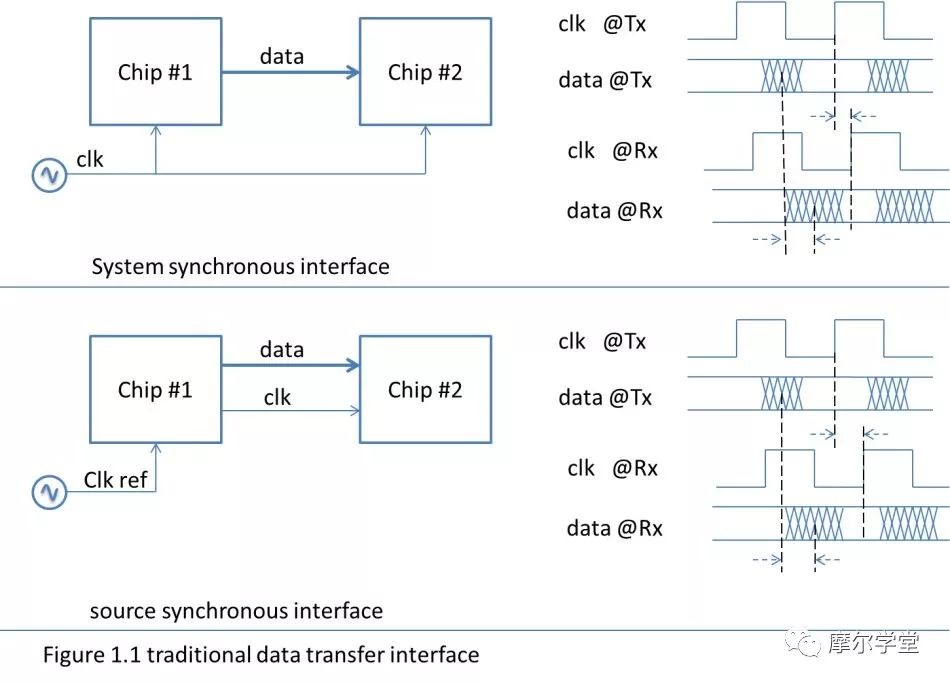

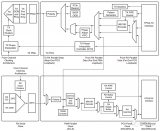

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行总线接口在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。a)、时钟...

2021-07-28 08:35:42

我想用serdes ip模拟图书馆的位置在哪里?

2020-05-20 15:05:17

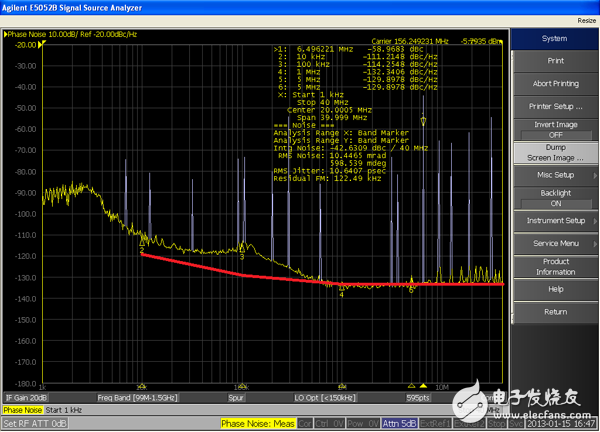

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。那么时钟抖动会对高速ADC的性能有什么影响呢?

2021-04-08 06:00:04

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

时钟相噪对ADC性能的影响是什么?锁相环的基本原理和相噪优化方式

2021-04-07 06:25:40

如题,9176DAC的PLL锁上了,证明时钟应该没问题,但是为什么DLL和serdes PLL锁不上呢?配置顺序,我是按照手册的START-UP SEQUENCE进行配置的。

2023-12-01 06:54:09

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立

2019-10-23 07:16:35

SerDes在93000平台上量产测试。本文将介绍Nautilus UDI方案是如何实现高速SerDes测试的,包括UDI结构,输入时钟设计,Load board设计,socket选型等多个测试环节。

2021-05-10 06:58:55

STM32系统架构基础名词有哪些呢?STM32时钟系统有哪些性能呢?

2021-12-14 07:49:07

),. clk_out1(link_clock))从serdes TX时钟制作绘图时钟;我希望链接时钟是txusrclk的两倍,因为GTX一次使用两个字节。但是link_clock是静态的,DRP_CLK_O是200Mhz,gt0_pll0lock_out是16Khz的方波。系统似乎一直在重置!戴夫

2020-07-31 09:10:30

我想把c6455 srio配置为1P4X的模式,是不是这种模式下只使用一个port,那么我在设置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的时候,只使能

2019-01-21 15:42:20

大家好。BUFG资源和DCM / PLL模块在许多FPGA线路上使用专用时钟布线资源。对于SerDes应用,我们使用BUFIO2来获得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

大家好, 在一个I / O块中有一个主serdes和一个slave serdes。如果我使用主设备,奴隶不能使用,是不是?谢谢。最好的祝福。

2020-06-08 15:03:22

什么是SerDes?

2021-06-24 07:52:02

嗨, 我计划在我的设计中使用SERDES(LVDS)作为背板。我已经浏览了virtex5用户指南中的advnced IO部分,并看过ISERDES_NODELAY和OSERDES宏。我已经看到了一些

2020-07-13 15:54:49

冲突、降低开关噪声、更低的功耗和封装成本等许多好处。而SERDES技术的主要缺点是需要非常精确、超低抖动的元件来提供用于控制高数据速率串行信号所需的参考时钟。即使严格控制元件布局,使用长度短的信号并

2019-05-21 05:00:13

本文将讨论通过优化封装内的阻抗不连续性和改善其回波损耗性能,以满足10Gbps SerDes键合线封装规范。

2021-04-25 07:42:13

约束将无法在时序分析期间返回任何路径”,因此,当我们使用输入SerDes时钟资源来生成DDR时钟时,我们不会期望任何分析甚至是建立/保持违规的通知。2)在同一白皮书中,“OFFSET约束不优化由内部

2019-08-09 09:54:33

我在官网上下载了CH569的数据手册和参考应用例程(EVT), 发现对SerDes这块的介绍很少, 而且EVT里也没有SerDes相关的例程.我想使用SerDes连接SFP模块来测试光纤通信.请问可以提供下关于SerDes的详细资料吗, 谢谢.

2022-05-18 08:37:16

需要生成一个低速单端时钟来测试非常慢的serdes通道(长篇故事为什么它如此低和单端)。我试图在低频模式下使用V5 DCM接受2.5MHz的输入时钟并产生15MHz-17.5MHz。当我使用GUI

2020-06-15 16:11:09

如何更有效地使用可编程时钟器件?设计SERDES参考时钟源面临的挑战有哪些?如何去实现XAUI参考时钟源?

2021-04-20 06:03:53

Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

2019-10-21 07:09:44

SerDes的基本结构是由哪些部分组成的?怎样去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有传输时钟信号吗?

2021-10-18 08:53:42

SERDES的作用有哪些?SerDes的主要构成可以分为哪几部分?

2021-10-18 09:25:08

漂移及漂移形成的原因是什么?光纤漂移引起的SERDES FIFO溢出问题分析BBU SERDES 双系时钟方案及具体实现

2021-04-19 08:35:11

的serdes?2、如果serdes是各自的,是否共享输入时钟?(外部时钟,对于我们来说是156.25MHz)3、在研究SRIO速率配置时发现文档中描述:serdes的输出时钟不能超过3.125GHz,该描述是否准确?是否适用于所有的serdes模块?谢谢!

2018-08-06 06:17:36

6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?

2018-08-02 06:11:31

7系列系列中的SERDES是否有最小延迟规范?我想了解如果SERDES直接(最短路径)连接到另一个SERDES以实现GTH收发器之间的最小延迟串行到串行连接,那将是什么样的。

2020-07-22 13:45:34

bufg用于非时钟输入逻辑?你可以使用组合逻辑和serdes选通来获得时序吗?以上来自于谷歌翻译以下为原文I'm a bit confused on the Spartan 6 clocking when

2019-06-19 06:38:52

选择SerDes参考时钟。各功能需要的时钟如下图:这就是我们需要配置的PLL1和PLL2,硬件和软件需要同时做好。参考的时钟源我们在核心板上已经做好,用户不需要额外做这部分的硬件。 具体是这样实现

2020-10-28 17:15:14

之后,还需要选择SerDes参考时钟。各功能需要的时钟如下图:这就是我们需要配置的PLL1和PLL2,硬件和软件需要同时做好。参考的时钟源我们在核心板上已经做好,用户不需要额外做这部分的硬件。 具体

2020-11-01 20:21:02

SERDES结构是怎样构成的?高速SERDES接口在网络方面有哪些应用?

2021-04-28 07:19:38

SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 应对未来高速

2021-11-12 06:46:26

引言在有线通信中,需要从数据中恢复时钟。将时钟编码到数据中的优点是可以省却发送时钟的线路,也有助于处理偏移问题。SERDES(串行器-解串器)器件诸如SCAN25100可

2008-08-15 22:51:17 21

21 M31 SerDes PHY IP M31 SerDes PHY IP为高带宽应用提供高性能、多通道功能和低功耗架构。SerDes IP支持从1.25G到10.3125Gbps的数据速率

2023-04-03 20:29:47

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统的带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

38 利用眼图模板评估串行器和解串器(SerDes)的性能

Abstract: Maxim has developed a family of serializer and deserializer

2008-11-26 14:08:24 2054

2054

摘要:Maxim开发了一系列串行器和解串器,广泛用于视频显示和数字图像系统中的高速、串行数据互联。目前,设计人员急需找到一种测试由串行器和解串器(SerDes)芯片组搭建的串行

2009-05-02 10:32:33 2031

2031

该应用笔记介绍如何根据STO超时、时钟频率和UART位时钟计算MAX9257/MAX9258可编程串行器/解串器(SerDes)的CCEN持续时间。

2011-07-30 22:55:13 1353

1353

讨论了物理设计中时钟网络的设计技术,并以现有的CPU时钟网络的为例,介绍了高性能CPU的时钟网络设计技术。

2011-12-27 15:28:56 46

46 SERDES在数字系统中高效时钟设计方案,无论是在一个FPGA、SoC还是ASSP中,为任何基于SERDES的协议选择一个参考时钟源都是非常具有挑战性的。

2012-02-16 11:23:43 5384

5384

本文以TLK3132为例,详细介绍了SERDES工作原理和器件特点,并以WI系统中的CPRI应用需求为例,提供TLK3132的设计方法等。

2012-05-07 16:01:58 6293

6293

电子发烧友网: 本文主要讲述的是 LatticeECP4 高速可配置SERDES。 LatticeECP4 FPGA系列结合了高性能 FPGA 结构、高性能I/O和多达16个通道的嵌入式SERDES,带有相关的物理编码子层(PCS)逻辑。每

2012-06-12 10:41:35 1439

1439

FPGA SERDES的应用需要考虑到板级硬件,SERDES参数和使用,应用协议等方面。由于这种复杂性,SERDES的调试工作对很多工程师来说是一个挑战。

2013-03-15 14:55:13 10360

10360

如何使用 HyperLynx DRC 来查找 SERDES 设计问题

2016-01-06 14:49:36 0

0 如何使用 HyperLynx DRC 来查找 SERDES 设计问题

2016-05-24 17:12:50 0

0 冲突、降低开关噪声、更低的功耗和封装成本等许多好处。而SERDES技术的主要缺点是需要非常精确、超低抖动的元件来提供用于控制高数据速率串行信号所需的参考时钟。即使严格控制元件布局,使用长度短的信号并遵循信号走线限制,这些接口的抖动

2017-10-26 15:37:45 4

4 高性能CPU的时钟网络设计

2017-10-30 15:28:58 23

23 在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟,然后将此时钟作为SERDES的参考时钟。

2017-11-18 12:08:49 5864

5864

的量产测试。那么,Nautilus UDI方案是如何实现包括UDI结构、输入时钟设计、Load board设计、socket选型等多个测试环节高速SerDes测试的呢?

2018-06-10 10:51:17 4434

4434

对于10Gbps及以上数据速率的SerDes,每个数据位的单位间隔是随着近 20~30ps的信号上升/下降时间而缩短的。

2018-07-18 17:18:48 7390

7390

Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

2019-05-24 15:33:25 4073

4073

只要SERDES接口的高级架构是合理的,SERDES总线的成功实现就归结为“实现细节”。

2019-08-14 17:57:00 2615

2615 随着SerDes 速度的增加,参考时钟所需的 RMS 相位抖动性能随之减少。在本次网络研讨会上,我们概述最新一代FPGA、光学DSP、相干DSP 和网络处理器的参考时钟要求,并重点介绍Si54x Ultra Series XO 和 VCXO 产品家族的关键功能

2020-11-03 17:13:10 2613

2613 为满足目前的56GPAM-4 SerDes技术,以支持更高带宽的100G+以太网和光网络设计。硬件开发人员通常需要100fs(典型值)以下RMS相位抖动规范的时钟。这些设计通常需要与CPU和系统时钟等其他频率时钟混用。

2020-11-12 15:25:55 4154

4154 为了学习xilinx serdes 原语的使用,以及交流学习经验,在工程项目中方便的应用SERDES进行设计,故编写此文档。

2021-02-26 10:04:00 37

37 ADN2865:连续速率12.3Mb/s至2.7 Gb/s时钟和数据恢复IC,带环路定时SERDES初步数据表

2021-05-09 14:33:49 7

7 ,另一个优势是能够通过一对差分对信号引脚(而不是8、16、32或N个数据引脚和一个时钟引脚)发送数据。在串行传输这个方面得益于更小的数据包和更密集的pcb而节省了成本。具体取决于晶片成本、封装成本、PCB成本和PCB拥塞等因素。 距离优势 在过去的十年里,SERDES在PCB和基

2021-07-23 11:59:46 3795

3795 SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 应对未来高速

2021-11-07 10:21:00 47

47 SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量。对于早期的SERDES,这意味着数据可以通过同轴电缆或光纤发送。

2022-07-22 10:39:21 2436

2436 112Gbps SerDes设计将根据应用情况在各种配置中被采用。下图展示了长距离(LR)、中距离(MR)、极短距离(VSR)和超短距离(XSR)拓扑,其中112G信令路径在每个拓扑中都突出显示。

2022-07-27 15:05:16 1091

1091 FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。

2022-10-31 11:28:41 1350

1350 SerDes 是空间到时间到空间的转换。并行数据同时传输但占用不同的物理互连,串行数据共享相同的物理空间但占用不同的时间时刻

2023-01-31 14:13:37 3369

3369 到Serial RIO……等等,都是在借助SerDes来提高数据传输的性能。SerDes是非常复杂的数模混合设计,用户手册的内容只是描述了相对粗略的概念以及使用方法,并不能完全解释SerDes是怎么工作

2023-03-16 10:28:11 1915

1915

同时介绍一种采用光电集成技术的,即采用光SerDes而非电SerDes的高速收发器。

2023-04-01 09:28:58 1078

1078 首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03:55 4707

4707

8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数

2023-07-27 16:10:01 1566

1566

Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路

2023-07-29 16:47:04 468

468

业界高端FPGA的卓越性能和高口碑声誉都有哪些因素了?其中很重要的一个因素就是FPGA内部丰富的时钟资源使得FPGA在处理复杂时钟结构和时序要求的设计中具有很大优势。设计师可以更好地控制和管理时钟信号,提高时序性能、减少时钟相关问题,并满足设计的高性能和稳定性要求。

2023-08-31 10:44:01 530

530 到Serial RIO……等等,都是在借助SerDes来提高数据传输的性能。SerDes是非常复杂的数模混合设计,用户手册的内容只是描述了相对粗略的概念以及使用方法,并不能完全解释SerDes是怎么工作

2023-10-16 14:50:37 558

558

尽管设计和验证很复杂,SERDES 已成为 SoC 模块不可或缺的一部分。随着 SERDES IP 模块现已推出,它有助于缓解任何成本、风险和上市时间问题。

2023-10-23 14:44:59 449

449

电子发烧友App

电子发烧友App

评论