一、前言

Ultrascale是赛灵思开发的支持包含步进功能的增强型FPGA架构,相比7系列的28nm工艺,Ultrascale采用20nm的工艺,主要有2个系列:Kintex和Virtex。Ultrascale+采用16ns,有3个系列:Artix,Kintex,Virtex。不仅是工艺制程方面,在其他方面也存在较大改进,如时钟资源与架构,本文将重点介绍Ultrascale的时钟资源与架构,Ultrascale+和Ultrascale大体上相似。

二、时钟架构

2.1 全局时钟输入

芯片外部的全局时钟通过FPGA的全局时钟输入(GC)进入到成对的差分时钟引脚。在每个Bank内都有4个GC,可以直接进入到全局时钟缓冲器,MMCM,PLL等。

2.2I/O bank

每个I/O bank都是处于一个单独的时钟区域中,包含了52个I/O引脚,还有4个全局时钟GC输入,4个GT。每个全局时钟输入引脚都可以连接到一个差分或单个时钟输入侧,可以配置成任意的I/O标准,包含差分端口标准,并且有一个P侧和N侧,P侧和N侧是主从关系,P为主,N为从。

2.3时钟轨道

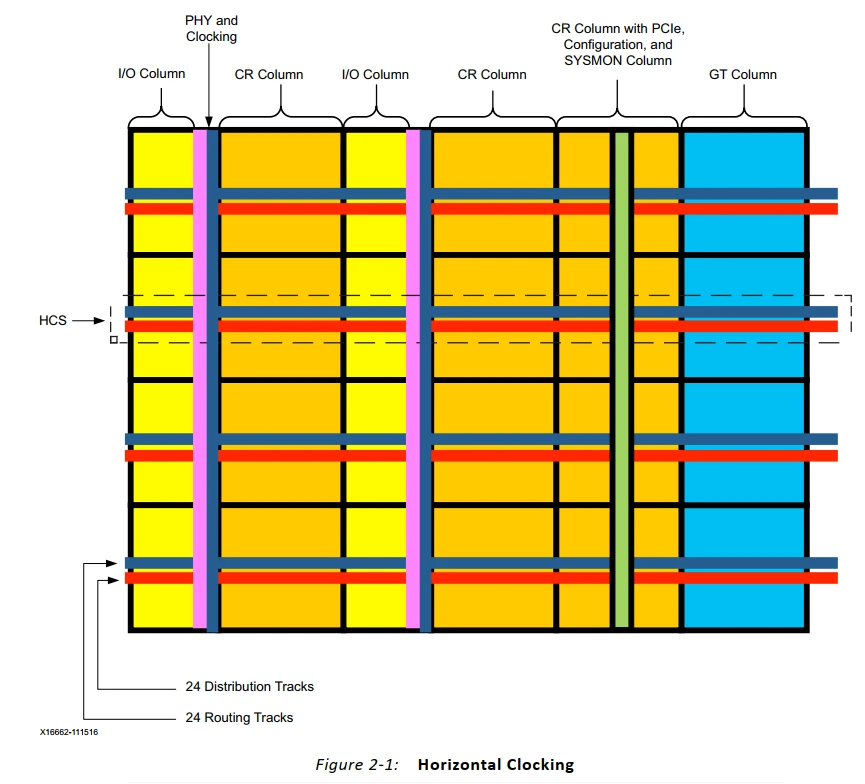

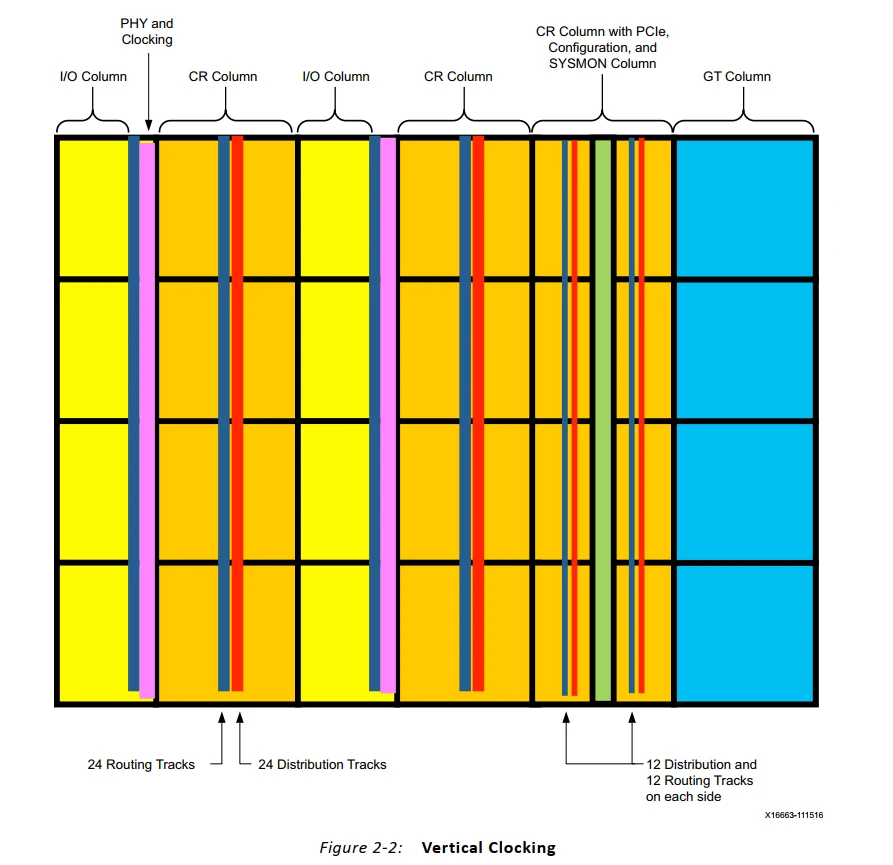

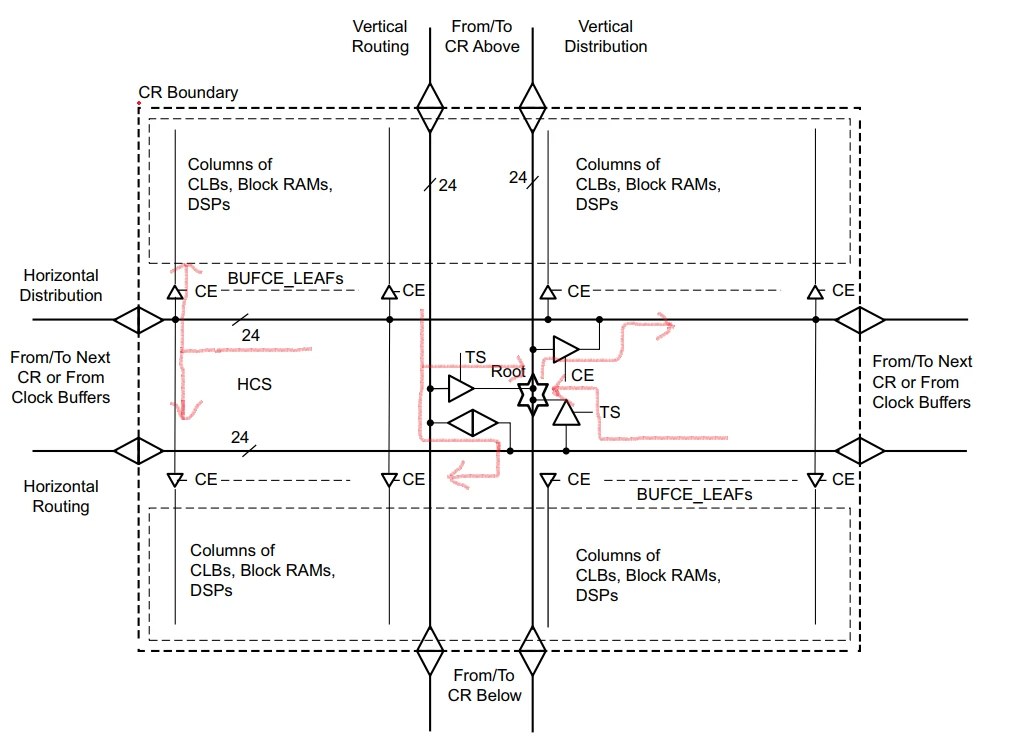

从时钟进入方向两个角度考虑,分为水平时钟和垂直时钟,通过水平时钟结构图,看出时钟架构中组成有普通CR列,特殊CR(带有PCIE,配置,系统监视器)类,I/O列,GT列,HCS和物理时钟。其中,CR(Clock Region)为时钟区域,HCS(Horizontal Clock Spine)为水平时钟脊。

CR和7系列的时钟区域类似,包含了可配置逻辑块CLBs,DSP,块状RAM,相关的时钟。一个CR纵向上包含60个CLBs,24个DSP和12个块状RAMs,HSC将会水平穿过中间位置。

HCS包含了水平布线资源和水平分布资源,叶子时钟缓冲器,时钟网络互连资源,根时钟网络,时钟缓冲器直接进入HCS,每个HCS有24个水平分布式轨道和12个水平布线轨道。

邻近输入/输出块列是物理层块PHY,它具有CMTs,全局时钟缓冲器,全局时钟多路选择结构,I/O逻辑管理功能。水平时钟布线轨道和分布轨道在水平方向上驱动进入各个时钟区域CRs,垂直布线和分布轨道在垂直方向上驱动邻近的时钟域CRs,分布轨道可以被布线轨道或PHY中的时钟单元直接驱动。I/O端口可以直接被PHY中的时钟驱动或者是通过布线轨道来自邻近的PHY,CMT包含了一个混合模式时钟管理器MMCM和2个锁相环PLLs。

垂直时钟是在垂直方向上进行驱动,在垂直方向上,没一列时钟域的中间位置都存在两类时钟轨道贯穿芯片:24条垂直布线轨道和24条垂直分布轨道,但在靠近GT列旁边CR列中,则是在CR列中间两侧位置各12条垂直布线轨道和12条垂直分布轨道。

三、时钟缓冲器

Ultrascale器件有三种全局时钟缓冲器:BUFGCTRL,BUFGCE,BUFGCE_DIV,还有一种本地BUFCE_LEAF时钟缓冲器,它可以驱动叶子时钟从水平分布轨道到达器件的不同位置。BUFGCTRL可以生成其他类型如BUFGMUX, BUFGMUX1, BUFGMUX_CTRL和 BUFGCE_1。

PHY的全局时钟包含了BUFGCTRL,BUFGCE,BUFGCE_DIV三类全局时钟缓冲器,它们都能被邻近I/O bank中的4个GC引脚驱动,也可被所属PHY中的MMCM和PLL驱动。然后这些时钟缓冲器驱动整个器件的布线轨道和分布轨道。每个PHY包含了24个BUFGCTRL,8个BUFGCE,4个BUFGCE_DIV,但只能同时使用其中的24个。

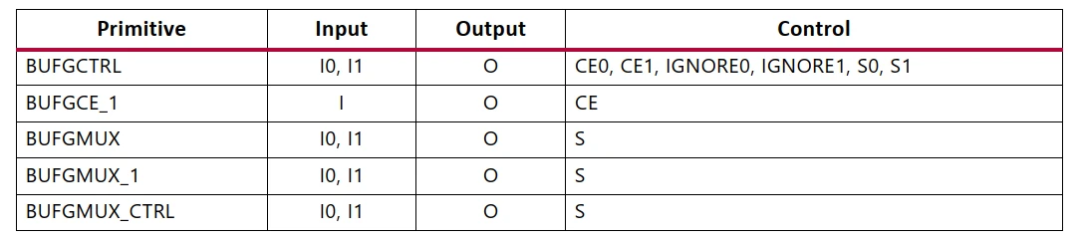

3类全局时钟缓冲器的端口差异如下图

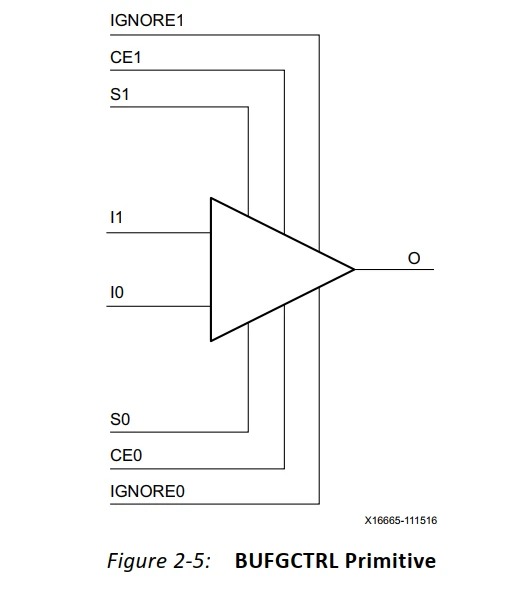

3.1 BUFGCTRL

BUFGCTRL用于在两个时钟输入源间进行切换,结构和选择逻辑如下图

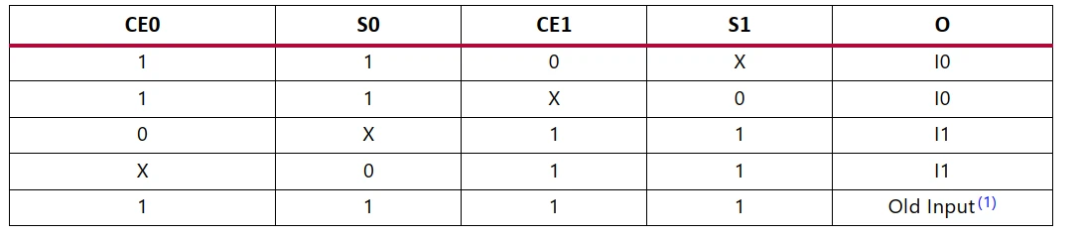

控制端口选择的真值表,其中最后一行Old Input是指在状态获取到之前的时钟有效输入值。

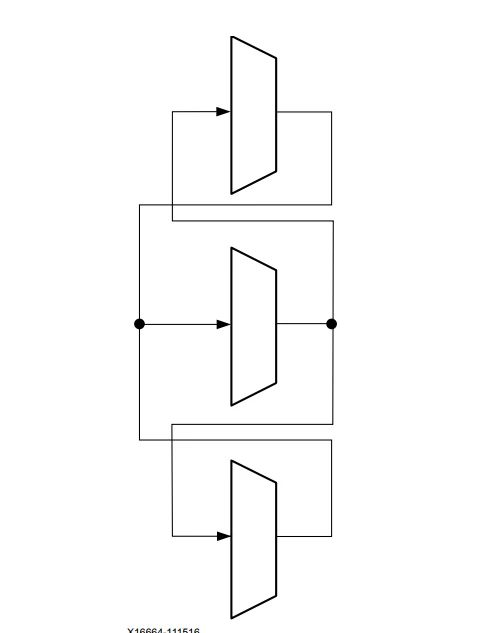

BUFGCTRL同时支持级联,可级联成环,如下图所示

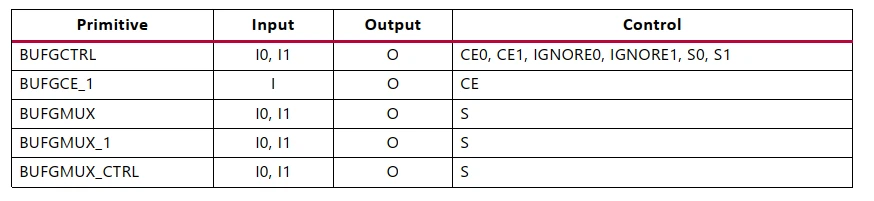

BUFGCTRL衍生出的其他几个全局时钟的原语输入关系如下表:

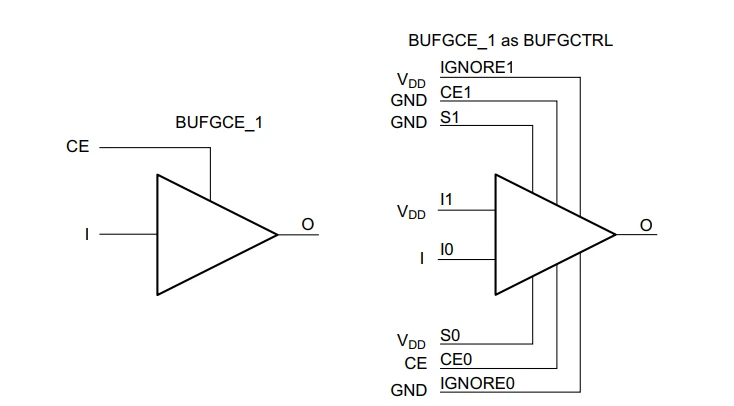

3.2 BUFGCE_1

BUFGCE_1的端口相对简单,只有1个输入端口I,一个使能端口CE和和1个输出端口O,BUFGCTRL将相应的一些端口设置为高低电平也可实现BUFGCE_1的功能。

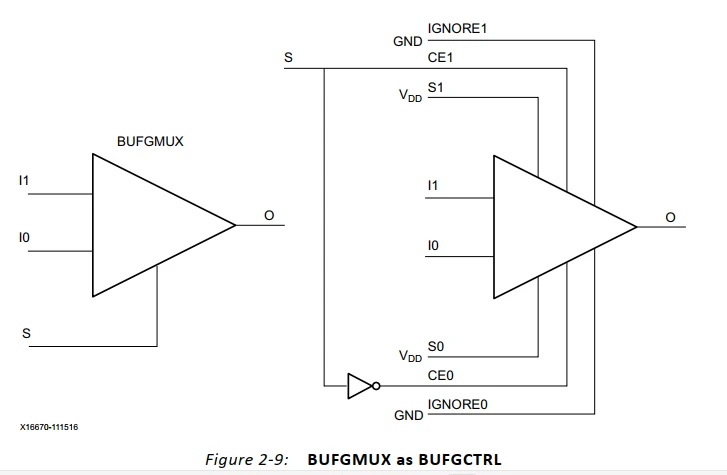

3.3 BUFGMUX和BUFGMUX_1

BUFGMUX有两个时钟输入端口,一个选择端口和一个时钟输出端口,通过将BUFGCTRL的一些输入引脚连接逻辑高电平或低电平,关系如下图

BUFGMUX_1是上升沿敏感,高电平保持,BUFGMUX和BUFGMUX_1的位置都可以进行手动约束。

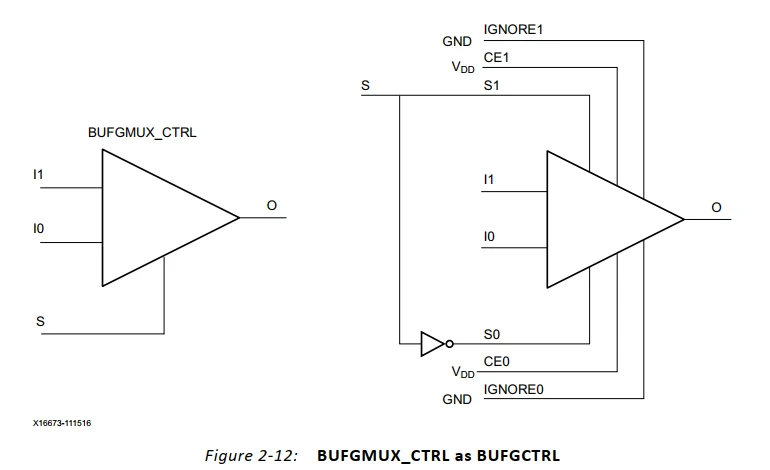

3.4 BUFGMUX_CTRL

BUFGMUX_CTRL也是2个时钟端口输入,1个选择端口,一个时钟输出端口的时钟缓冲器,和BUFGCTRL的关系如下图,

BUFGMUX_CTRL用S端口作为选择端口,S端口可以在任何时候切换,也不会造成干扰。 S端口的建立和保持时间取决于输出端口在切换时钟前是否通过一个之前选择时钟的额外脉冲信号。

3.5 BUFCE_LEAF

BUFCE_LEAF是一个有使能端口CE,可以让叶子单元驱动水平的HCS行,也是一个叶子时钟缓冲器的交汇口,驱动带有单个时钟输入的不同区域。当使能端口CE为低电平时输出为0,高电平时输出为输入I

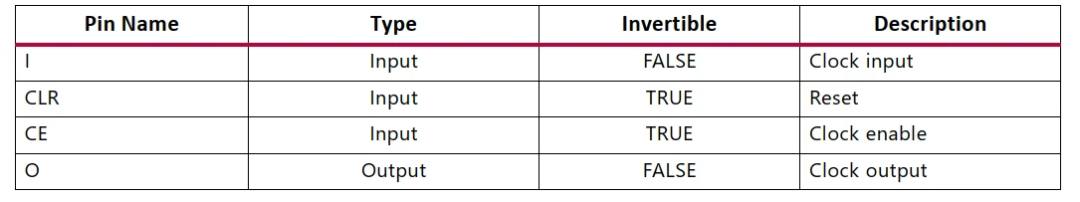

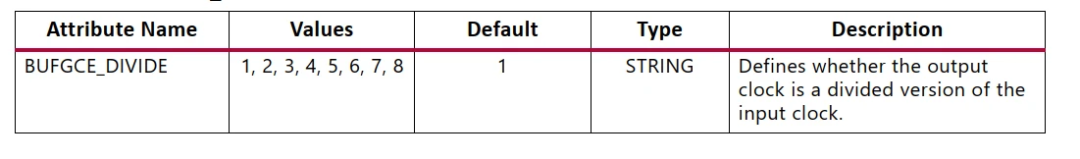

3.6 BUFGCE_DIV

BUFGCE_DIV有3个输入端口I、使能CE、清零CLR和输出端口O,可以直接驱动布线轨道和分布轨道,并且可以进行时钟的1-8分频。BUFGCE_DIV的输入端口和属性如下

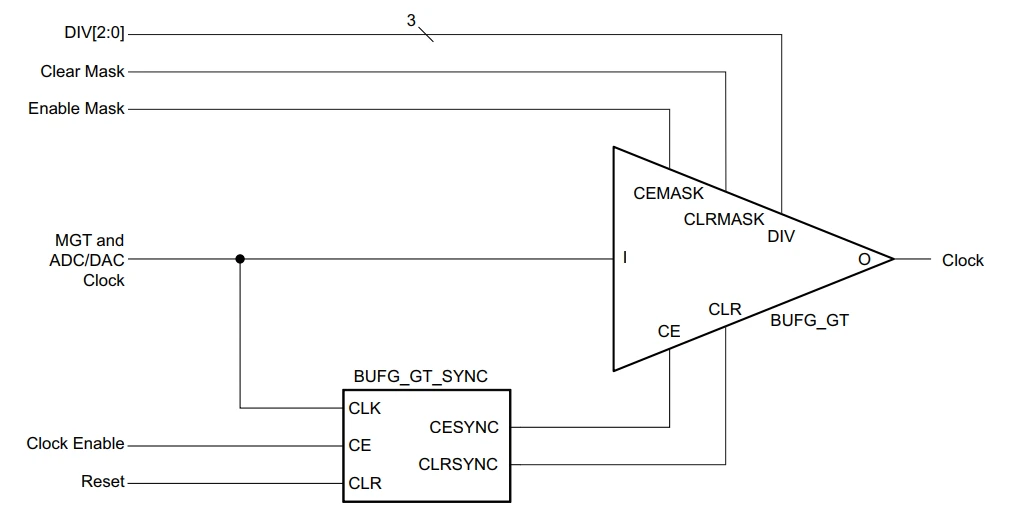

BUFG_GT是被高速收发器GT和射频SOC中的ADC/DAC所驱动,BUFG_GT是这些模块实现驱动时钟布线轨道的唯一方式,用于GT时钟的分频。BUFG_GT_SYNC是BUFG_GT的同步器,是靠Vivado软件自动插入,不会在设计文件中体现,可以直接驱动布线轨道和分布轨道,也属于时钟缓冲器。

在UltraScale器件中每个GT Quad有24个BUFG_GT和10个BUFG_GT_SYNC,UltraScale+器件中每个GT Quad有24个BUFG_GT和14个BUFG_GT_SYNC。BUFG_GT的端口相对较多,如下图。

3.7 BUFG_PS

BUFG_PS是只有一个输入,一个输出的简单时钟缓冲器,属于Zynq UltraScale+系列中PS的时钟缓冲器,可以让时钟从PS进入到PL中。共有18个PS 时钟可以驱动BUFG_PS,布局位置处于PS的旁边。

四、时钟驱动关系

在一个CR中,垂直布线轨道和水平布线轨道是互通的,垂直分布轨道可以单向通到水平分布轨道,但分布轨道不能通向布线轨道。布线轨道也可以驱动邻近CR的布线轨道和分布轨道,分布轨道可以驱动邻近CR的水平分布轨道。

时钟进入时钟缓冲器有两种方式。

方式一:时钟可以直接通过布线轨道进入到CR的中心位置,即图中的root,然后可以驱动水平分布轨道和垂直分布轨道。通过这种方式,时钟缓冲器可以驱动到CR内一个特点位置,时钟缓冲器在该位置上可以先通过垂直分布轨道,再水平分布轨道进入到时钟点。时钟点可以通过当前CR或邻近CR中带有使能端口CE的叶子时钟驱动,这种分布方案可以将根节点移动到指定的位置来改善,降低偏斜。

方式二:时钟点可以被本区域内或邻近区域内带有使能端口CE的叶子时钟驱动,时钟点驱动时钟缓冲器,时钟缓冲器再进入分布轨道,这将减少时间插入时延。

五、缩略词

CR: Clock Region 时钟区域

GT:Gigabit Transceivers G比特收发器

GC:Global Clock 全局时钟

HCS:Horizontal Clock Spine 水平时钟脊

MMCM:Mixed-mode Clock Manager 混合模式时钟管理器

PHY:Physical Layer 物理层

PS: Processor Sytem 处理器系统

SYSMON:System Monitor 系统监视器

-

FPGA

+关注

关注

1664文章

22504浏览量

639293 -

Xilinx

+关注

关注

73文章

2208浏览量

131908 -

UltraScale

+关注

关注

0文章

126浏览量

32411

原文标题:Xilinx之Ultrascale系列时钟资源与驱动关系

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Xilinx UltraScale 系列发布常见问题汇总

Xilinx Ultrascale 16nm FPGA/SoC电源解决方案

直击关于Xilinx UltraScale架构、Virtex和Kintex UltraScale架构FPGA 和最新的Vivado开发工具的9大要点

Xilinx 7系列FPGA架构的区域时钟资源介绍

Xilinx全新UltraScale架构介绍

UltraScale/UltraScale+的时钟资源

Xilinx 7系列与Ultrascale系列FPGA的区别

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

评论