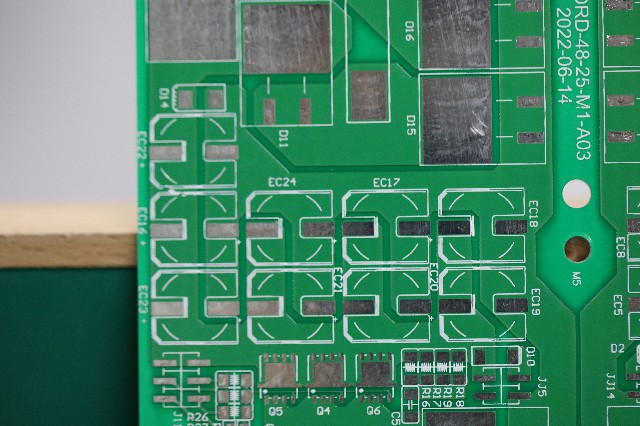

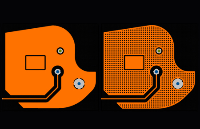

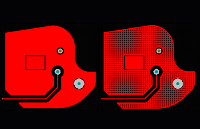

一般在空白区域的敷铜绝大部分情况是接地。只是在高速信号线旁敷铜时要注意敷铜与信号线的距离,因为所敷的铜会降低一点走线的特性阻抗。也要注意不要影响到它层的特性阻抗,例如在dual strip line的结构时。

这里又涉及到阻抗匹配的问题:可以把电源平面上面的信号线使用微带线模型计算特性阻抗,电源和地平面之间的信号可以使用带状线模型计算,在计算特性阻抗时电源平面跟地平面都必须视为参考平面。例如四层板: 顶层-电源层-地层-底层,这时顶层走线特性阻抗的模型是以电源平面为参考平面的微带线模型。

一般软件自动产生测试点是否满足测试需求必须看对加测试点的规范是否符合测试机具的要求。另外,如果走线太密且加测试点的规范比较严,则有可能没办法自动对每段线都加上测试点,当然,需要手动补齐所要测试的地方。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源

+关注

关注

185文章

18709浏览量

261394 -

pcb

+关注

关注

4391文章

23742浏览量

420763 -

地平面

+关注

关注

0文章

8浏览量

6977

发布评论请先 登录

相关推荐

热点推荐

【PCB】四层电路板的PCB设计

步骤。可以这样说,前面各项准备工作都是为它而做的。PCB布线有单面布线、双面布线和多层布线。布线的方式有两种:自动布线和交互式布线。

在PCB设计

发表于 03-12 13:31

云计算环境下的IP地址分配方式

之前我们聊过在计算机环境下IP地址的分配方式,但在云计算环境下,IP地址的分配方式更加灵活,可以根据实际需求进行配置,用来满足不同企业和应用的需求。 在云计算环境

高速PCB设计中多个信号层敷铜在接地和接电源上分配方式

高速PCB设计中多个信号层敷铜在接地和接电源上分配方式

评论