作者:Mculover666 1.实验目的 用HDL语言+Vivado创建一个挂载在AXI总线上的自定义IP核 2.实验步骤 2.1.创建一个新的项目 2.2.调用Create

2020-12-21 16:34:14 4566

4566

在FPGA设计中,复位电路是非常重要的一部分,它能够确保系统从初始状态开始启动并保证正确运行。本文将分别介绍FPGA中三种常用复位电路:同步复位、异步复位和异步复位同步释放,以及相应的Verilog代码示例。

2023-05-14 14:44:49 3405

3405

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-12-12 09:19:08 3688

3688

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

2025-03-01 14:44:19 2709

2709

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是与FPGA独立的,只是集成在了一起呢,还是占用了FPGA的资源来形成一个RAM?如果我以ROM的形式调用该IP核,在

2013-01-10 17:19:11

的基础上,给出了一种仿真调试方 案;利用该方案指出了其中若干逻辑错误并对其进行修改,最终完成了修改后IP核的FPGA下载测试。1 OC8051结构分析OpenCores网站提供的OC8051 IP核

2012-08-11 11:41:47

的情况时,总会遇到一些以前未曾接触过的新内容,这些新内容会让我们感到陌生和恐惧,不知道该如何下手。

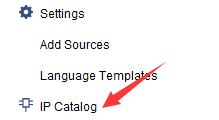

那么今天以xilinx vivado 为例分享学习FPGA 新IP核的正确打开方式。

一、常规

2023-11-17 11:09:22

FPGA的IP软核使用技巧主要包括以下几个方面:

理解IP软核的概念和特性 :

IP软核是指用硬件描述语言(如VHDL或Verilog)描述的功能块,但并不涉及具体的电路实现细节。它通常只经过功能

2024-05-27 16:13:24

IP核简介IP核是指:将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器、SDRAM控制器、PCI接口等等设计成可修改参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD

2011-07-15 14:46:14

参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用IP核是一个发展趋势。许多公司推荐使用现成的或经过测试的宏功能模块、IP核,用来增强

2011-07-06 14:15:52

发生IP核锁定,一般是Vivado版本不同导致的,下面介绍几种方法: 1 常用的方法 1)生成IP核的状态报告 Report -》 Report IP Status 2)点击

2021-01-08 17:12:52

Vivado中xilinx_courdic IP核(求exp指数函数)使用

2021-03-03 07:35:03

Vivado浮点数IP核的一些设置注意点

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一个IP核实

2025-10-24 06:25:22

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸载过Modelsim,用vivado打开过ISE工程,因为工程中很多IP核不能用所以在重新生成过程中发现了这个问题,还请大神告知是怎么回事?

2023-04-24 23:42:21

刚刚接触FPGA,通过视频学习发现使用VIVADO编写FPGA程序可以通过调用IP核连线和编写.v文件,实际做过程什么时候该调用IP,怎么知道有该功能的IP,先调用IP连线还是先写.V文件呢?

2022-08-29 08:44:03

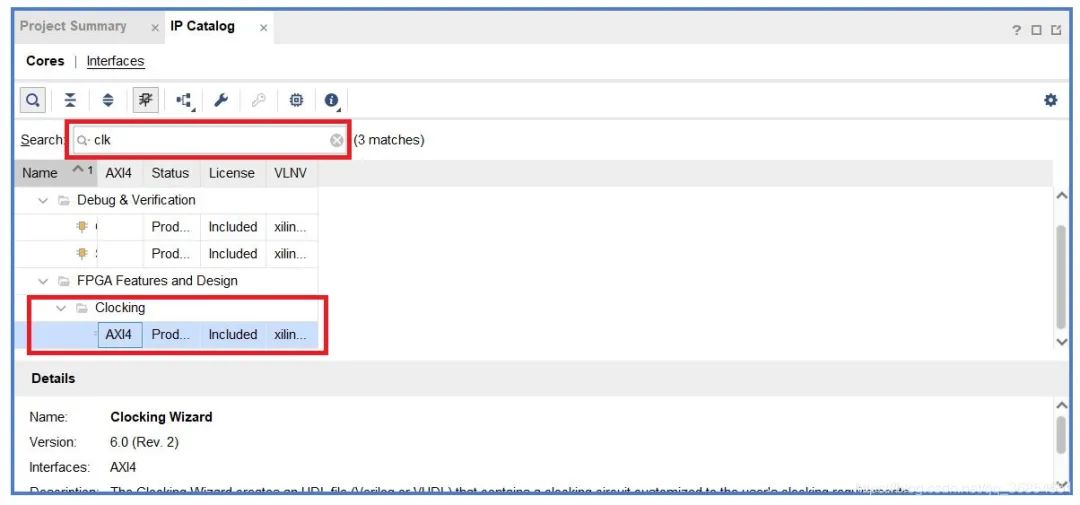

大家伙,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:39:13

,int b);最后经过编译可以生成VHDL等硬件描述文件与IP核文件.我想调用自己写的IP核(add函数)我在vivado 中添加了自定义IP核与PS(处理系统)我知道网上说用AXI Steam? 来连接

2016-01-28 18:40:28

vivado的三速以太网IP核接口太多了,完全不知道应该怎么用,哪位大佬能发我一份设计或者仿真吗?简单的就好

2021-04-15 12:58:00

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源代码;另一个方法是将网表文件edf文件与端口声明结合,这种方法只能实现不带ip核的封装

2017-07-14 09:18:30

vivado三种常用IP核的调用当前使用版本为vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点

2021-07-29 06:07:16

常用的FBAR模型有哪三种?

2021-03-11 06:16:18

做TCP通讯的时候,有时候需要知道自己的IP虽然知道自己电脑ip可以不用这么麻烦,但是有时候就想用自己所学来获得自己所需,职业病 咳咳这里给出得到本地IP的三种方法。源程序,在附件里。

2012-11-27 17:17:54

有没有大神可以提供xilinx FPGA的FFT IP核的调用的verilog 的参考程序,最近在学习FFT的IP核的使用,但是仿真结果有问题,所以想找些参考设计,谢谢

2016-12-25 17:05:38

用vivado2019.2建立工程,工程中调用cordic IP核进行atan求解,功能仿真时正常且满足要求;综合时正常;实现时报错提示多重驱动。

如果经cordic计算后的输出值不用于后续的操作

2023-06-06 17:17:37

方式;固核则通常介于上面两者之间,它已经通过功能验证、时序分析等过程,设计人员可以以逻辑门级网表的形式获取。FPGA的开发方式分为三种,分别是:原理图、Verilog HDL以及IP核。其中原理图方式

2016-12-22 23:37:00

为什么vivado2016调用MIG ip核会收到严重警告呢?这个critical warning会有影响吗,要怎么解决呢?

2021-10-18 09:41:21

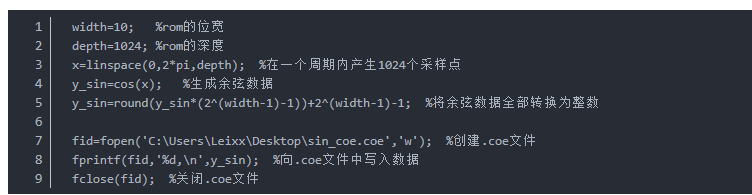

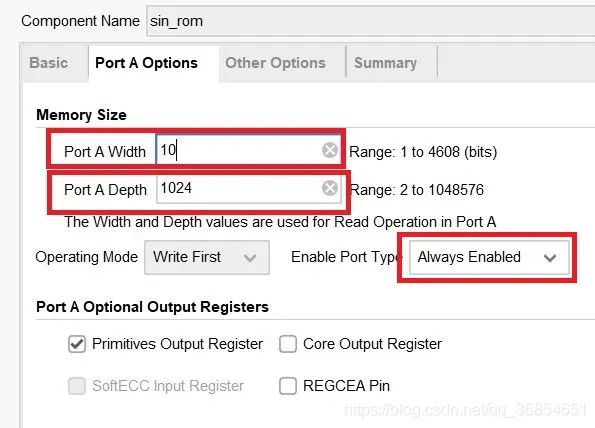

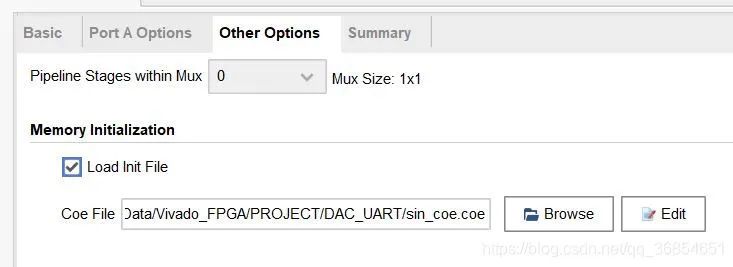

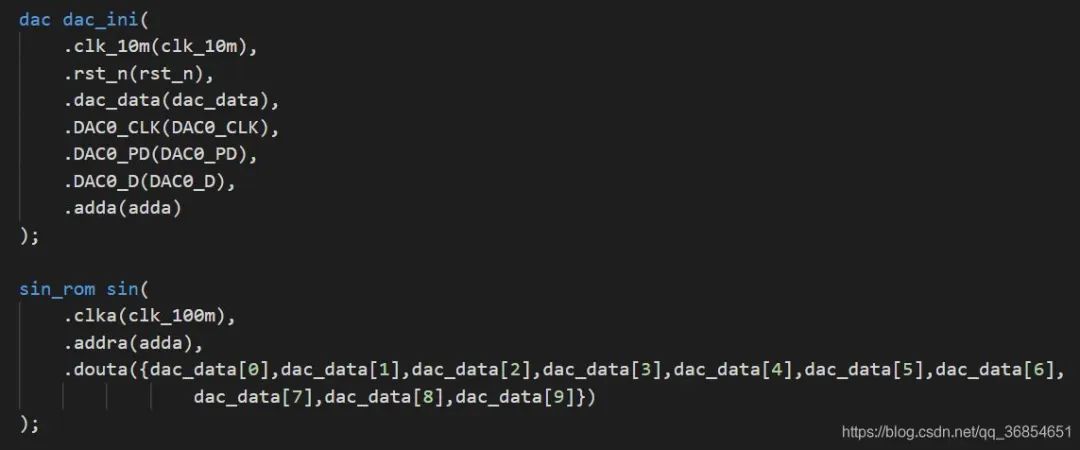

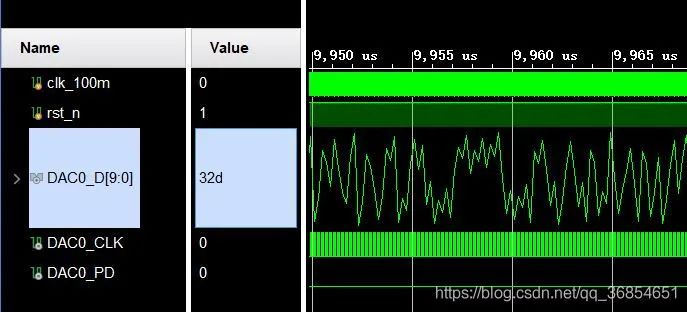

本例程主要使用Vivado 调用ROM IP核,用含有正弦曲线的.coe文件初始化ROM,最终通过仿真实现波形的显示 一、首先建立工程 二、选择芯片的型号 我

2021-01-08 17:16:43

对于深入学习使用FPGA的小伙伴们,特别是一些复杂的、大规模的设计应用,适宜的IP核对开发能起到事半功倍的作用。IP核的概念与我们sdk里库的概念相似。IP即电路功能模块,用户可以直接调用这些模块

2024-04-29 21:01:16

quartus ii9.0创建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)这些文件都有用吗,想在其他工程里调用这些IP核,这几个文件全部要添加吗?

2013-07-02 17:20:01

单片机系统中最常用的三种通信协议是什么?

2022-02-17 06:03:46

%91/vivado2016-%E8%B0%83%E7%94%A8MIG-ip%E6%A0%B8%E4%B8%A5%E9%87%8D%E8%AD%A6%E5%91%8A-Project-1-19/m-p/884989链接不管用的话就按照下图自己找吧。回复: vivado2016 调用MIG ip核

2021-07-28 07:16:27

飞舞,这里就不赘述了,以免有凑字数的嫌疑。下面我们就Matlab和FPGA两个工具双管齐下,比对Vivado的FFT IP核生成的数据。2 Matlab产生测试数据,绘制cos时域和频域波形

2019-08-10 14:30:03

核的分类和特点是什么?基于IP核的FPGA设计方法是什么?

2021-05-08 07:07:01

的经验几乎为0,因此我想就如何解决这个问题提出建议。这就是我的想法:1 - 首先,用Vivado HLS转换VHDL中的C代码(我现在有一些经验)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

`玩转Zynq连载21——Vivado中IP核的移植更多资料共享腾讯微云链接:https://share.weiyun.com/5s6bA0s百度网盘链接:https://pan.baidu.com

2019-09-04 10:06:45

Vivado的FFT IP核生成的数据。 2 Matlab产生测试数据,绘制cos时域和频域波形使用projectzstar_ex67matlab文件夹下的Matlab源码fft_1line.m,运行产生1组

2020-01-07 09:33:53

大家伙,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-16 11:42:55

IR900NAT配置常用的三种情景

2024-07-26 07:02:10

三种不同的“防 Ping”技巧

浅析三种不同的“防 Ping”方法

众所周知,Ping命令是一个非常有用的网络命令,大家常用它

2010-04-14 13:53:00 1287

1287 FPGA中IP核的生成,简单介绍Quartus II生成IP核的基本操作,简单实用挺不错的资料

2015-11-30 17:36:15 12

12 FPGA的IP核设计技术的系列资料,大家可以收集看下,这些都是我看过过滤后留下的,感觉不错,希望对大家有帮助

2015-11-30 17:49:01 6

6 利用FPGA的IP核设计和实现FFT算法

2016-05-24 14:14:47 37

37 引入IP核的三维FPGA结构研

2017-01-07 20:32:20 2

2 本文基于xilinx 的IP核设计,源于音频下采样这一需求。 创建vivado工程 1. 首先打开vivado,创建一个新的project(勾选create project subdirectory

2017-02-08 02:25:09 5883

5883

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言

2017-02-08 13:08:11 3085

3085

有关FPGA——VIVADO15.4开发中IP 的建立

2017-02-28 21:04:35 16

16 在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软件 VCS软件最好安装

2018-07-05 03:30:00 12369

12369

中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。 IP内核的三种类型 IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。

2017-11-15 11:19:14 10744

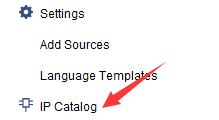

10744 在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动添加到当前工程中;另一种是利用Manage IP,创建独立

2017-11-18 04:22:58 6145

6145 中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。 IP内核的三种类型 IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。

2017-11-28 15:49:58 2339

2339 在给别人用自己的工程时可以封装IP,Vivado用封装IP的工具,可以得到像xilinx的ip一样的可以配置参数的IP核,但是用其他工程调用后发现还是能看到源文件,如何将工程源文件加密,暂时没有找到方法,如果知道还请赐教。

2018-06-26 11:33:00 8932

8932 大家好,又到了每日学习的时间了,今天咱们来聊一聊vivado 调用IP核。 首先咱们来了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

2018-12-16 11:31:21 14210

14210

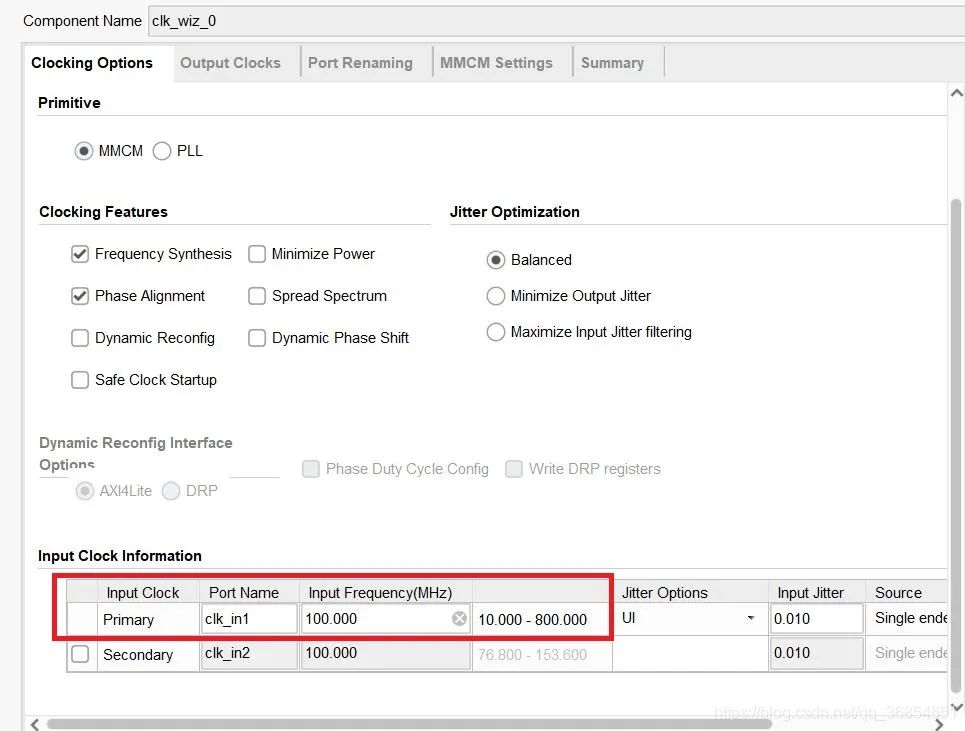

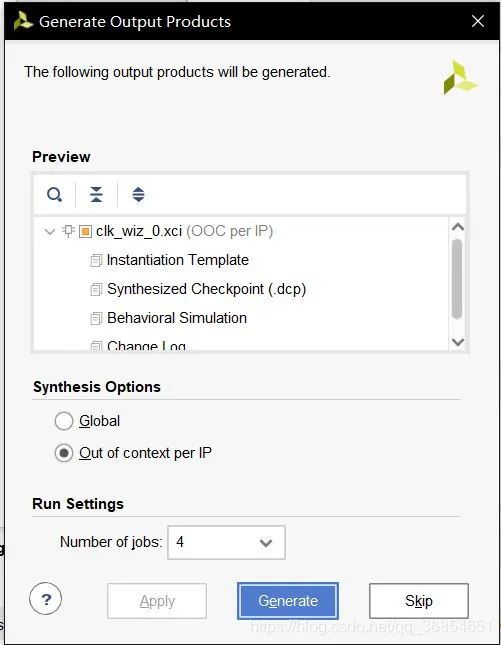

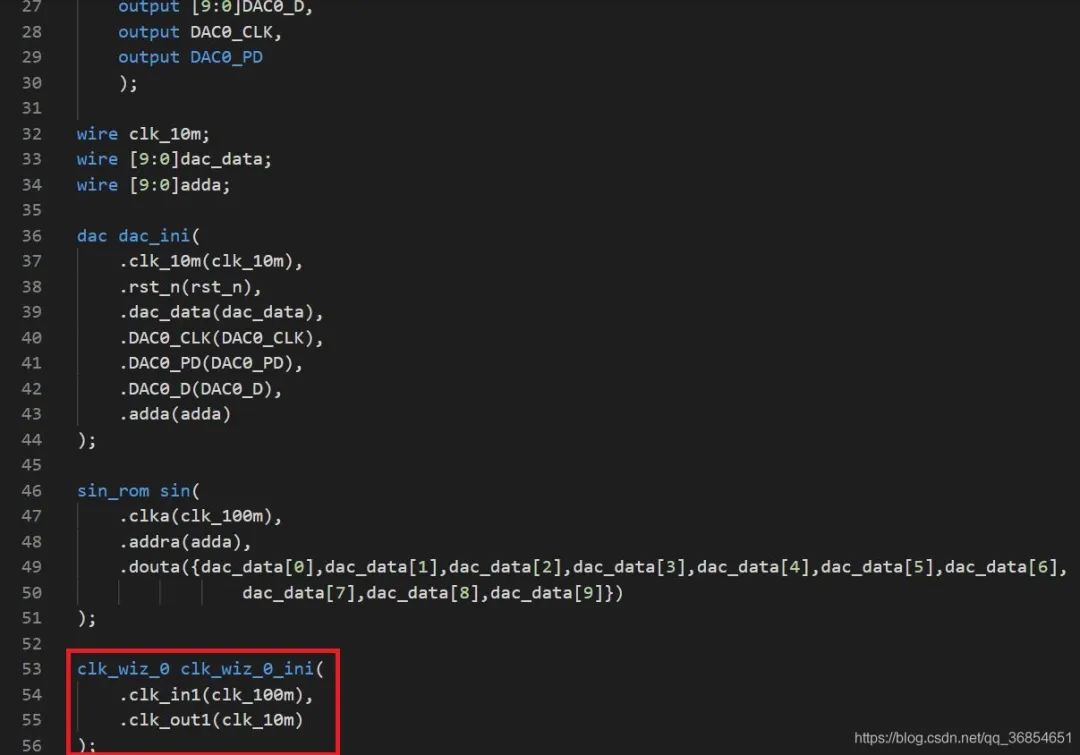

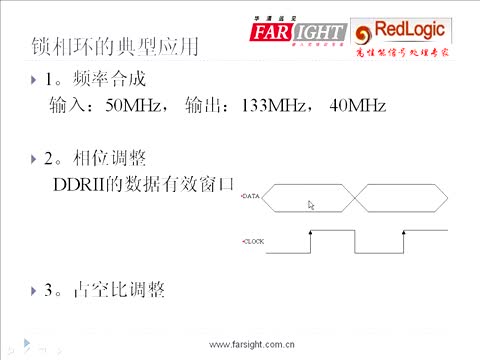

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

2018-12-22 14:26:38 5200

5200 在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,这是同步时序电路的关键,这时就需要使用到时钟向导IP,下面就介绍一下在vivado中进行PL开发时调用IP的方法。

2018-12-22 15:14:38 10894

10894 IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

2019-12-19 07:07:00 2268

2268

IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

2019-10-08 07:09:00 1940

1940 IP核有三种不同的存在形式:HDL语言形式,网表形式、版图形式。分别对应我们常说的三类IP内核:软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种IP内核实现方法也各具特色。

2019-09-26 07:08:00 2545

2545

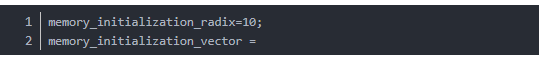

.coe格式的数据文件简介 在Vivado中,对rom进行初始化的文件是.coe文件.它的格式如下: memory_initialization_radix=10

2020-11-20 15:01:24 7939

7939

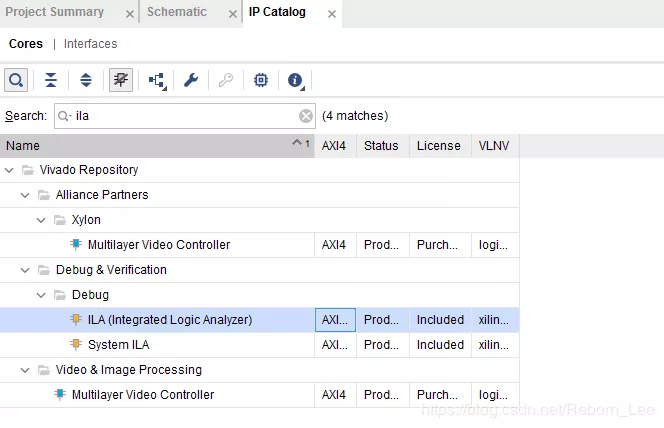

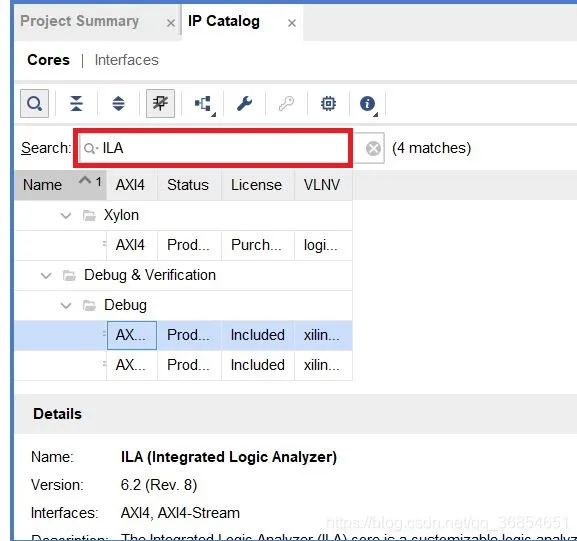

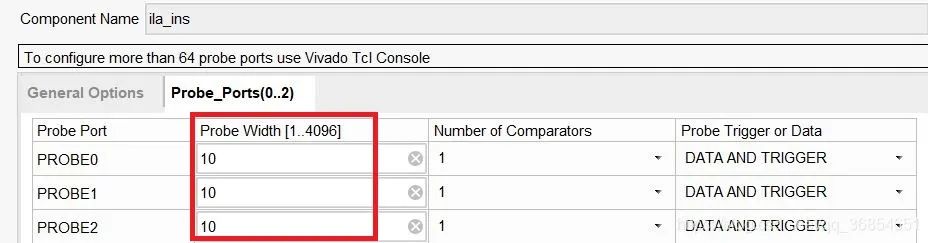

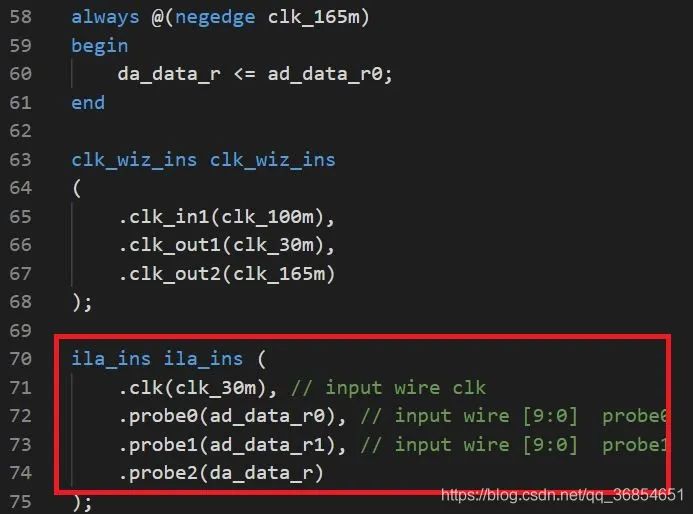

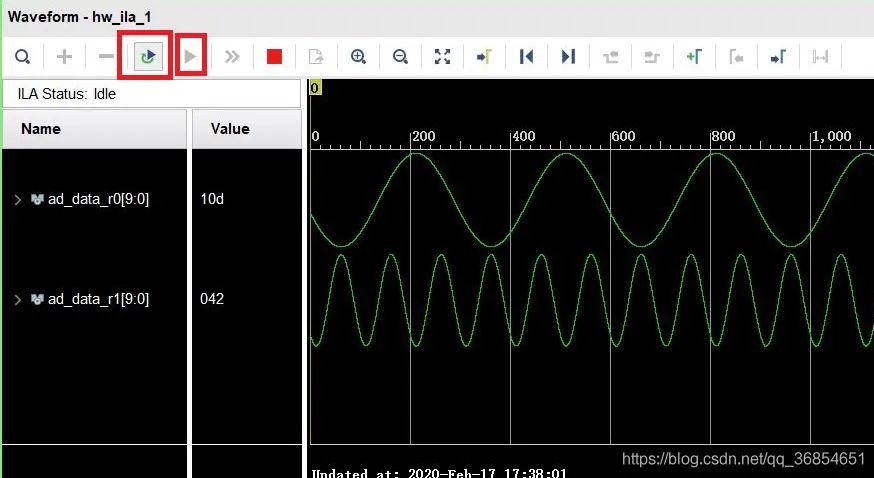

Vivado中提供了多种Debug的操作方式,下面就来总结一下: 1. 代码中例化ILA IP核 第一种,直接例化ILA IP核: 需要探测多少个信号,信号的位宽是多少,直接选择即可: 下面界面可以

2020-11-11 17:07:13 11668

11668

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

13270 Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5种类型:Single-port RAM

2021-03-10 06:15:56 19

19 些许改进,所以写这篇文章补充下。 在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。 对于没有使用SECURE IP核的IP核仿真,只需要在VCS

2021-03-22 10:31:16 5360

5360 本次使用Vivado调用DDS的IP进行仿真,并尝试多种配置方式的区别,设计单通道信号发生器(固定频率)、Verilog查表法实现DDS、AM调制解调、DSB调制解调、可编程控制的信号发生器(调频调相)。

2021-04-27 16:33:06 8131

8131

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

2021-04-27 15:45:12 25681

25681

Vivado提供了三种封装IP的方式:(1)将当前工程封装为IP;(2)将当前工程中的BD(IPI 设计)封装为IP;(3)将指定的文件目录封装为IP。 IP Packager支持的输入文件HDL

2021-08-10 18:09:29 9155

9155

调用第三方仿真软件查看波形的过程中存在的一些问题。 1、添加新的观测信号需要重新仿真 Vivado直接调用Modelsim/QuestaSim进行仿真时,波形文件里默认只会出现仿真最顶层中包含

2021-09-02 10:12:06 10120

10120

本文以一个案例的形式来介绍lattice DDR3 IP核的生成及调用过程,同时介绍各个接口信号的功能作用

2022-03-16 14:14:19 2713

2713

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此IP。因此本次详细介绍使用VIvado来封装自己的IP,并使用IP创建工程。

2022-04-21 08:58:05 7941

7941 前年,发表了一篇文章《VCS独立仿真Vivado IP核的一些方法总结》(链接在参考资料1),里面简单讲述了使用VCS仿真Vivado IP核时遇到的一些问题及解决方案,发表之后经过一年多操作上也有些许改进,所以写这篇文章补充下。

2022-08-29 14:41:55 4676

4676 最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

2023-06-06 11:09:56 4032

4032

在仿真Vivado IP核时分两种情况,分为未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

FPGA IP核(Intellectual Property core)是指在可编程逻辑器件(Field-Programmable Gate Array,FPGA)中使用的可复用的设计模块或功能片段。它们是预先编写好的硬件设计代码,可以在FPGA芯片上实现特定的功能。

2023-07-03 17:13:28 8969

8969 Modelsim是十分常用的外部仿真工具,在Vivado中也可以调用Modelsim进行仿真,下面将介绍如何对vivado进行配置并调用Modelsim进行仿真,在进行仿真之前需要提前安装Modelsim软件。

2023-07-24 09:04:43 5396

5396

在 Linux 系统中,经常需要查找 IP 地址以进行网络配置、故障排除或安全管理。无论是查找本地主机的 IP 地址还是查找其他设备的 IP 地址,本文将介绍三种简单的方法,帮助你在 Linux 中轻松找到所需的 IP 地址。

2023-08-02 09:53:30 973

973

Vivado IP核提供了强大的FIFO生成器,可以通过图形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

IP(Intellectual Property)是知识产权的意思,半导体行业的IP是“用于ASIC或FPGA中的预先设计好的电路功能模块”。一些常用的复杂的功能模块(如FIFO、RAM、FIR

2023-08-22 15:04:43 7796

7796

上一篇介绍了常用的锁相环IP,这一节将介绍一种较为常用的 存储类IP核 ——ROM的使用方法。ROM是 只读存储器 (Read-Only Memory),顾名思义,我们只能读出事先存放在固态中的数据

2023-08-22 15:06:38 7616

7616

在给Vivado中的一些IP核进行配置的时候,发现有Shared Logic这一项,这里以Tri Mode Ethernet MAC IP核为例,如图1所示。

2023-09-06 17:05:12 3014

3014

Vivado是Xilinx公司2012年推出的新一代集成开发环境,它强调系统级的设计思想及以IP为核心的设计理念,突出IP核在数字系统设计中的作用。

2023-09-17 15:37:31 3220

3220

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 FPGA(现场可编程门阵列)的编程涉及到三种主要的硬件描述语言(HDL):VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。这些语言在FPGA设计和开发过程中扮演着至关重要的角色。

2024-03-15 14:36:01 2412

2412 本文介绍了Vidado中FFT IP核的使用,具体内容为:调用IP核>>配置界面介绍>>IP核端口介绍>>MATLAB生成测试数据>>测试verilogHDL>>TestBench仿真>>结果验证>>FFT运算。

2024-11-06 09:51:43 5640

5640

电子发烧友App

电子发烧友App

评论