当前使用版本为vivado 2018.3

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

今天介绍的是vivado的三种常用IP核:时钟倍频(Clocking Wizard),实时仿真(ILA),ROM调用(Block Memory)。

Clocking Wizard

该IP核可以将输入的时钟信号进行倍频,倍数可以大于1,也可以小于1,非常方便。

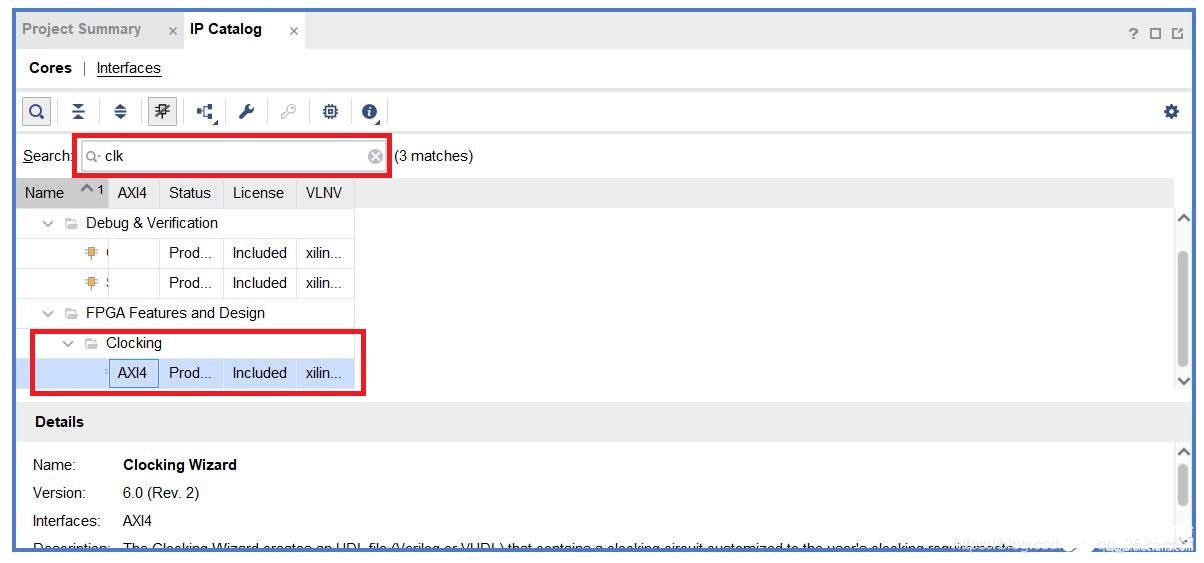

打开vivado 找到IP Catelog

在右侧输入栏中输入clk,找到Clocking Wizard

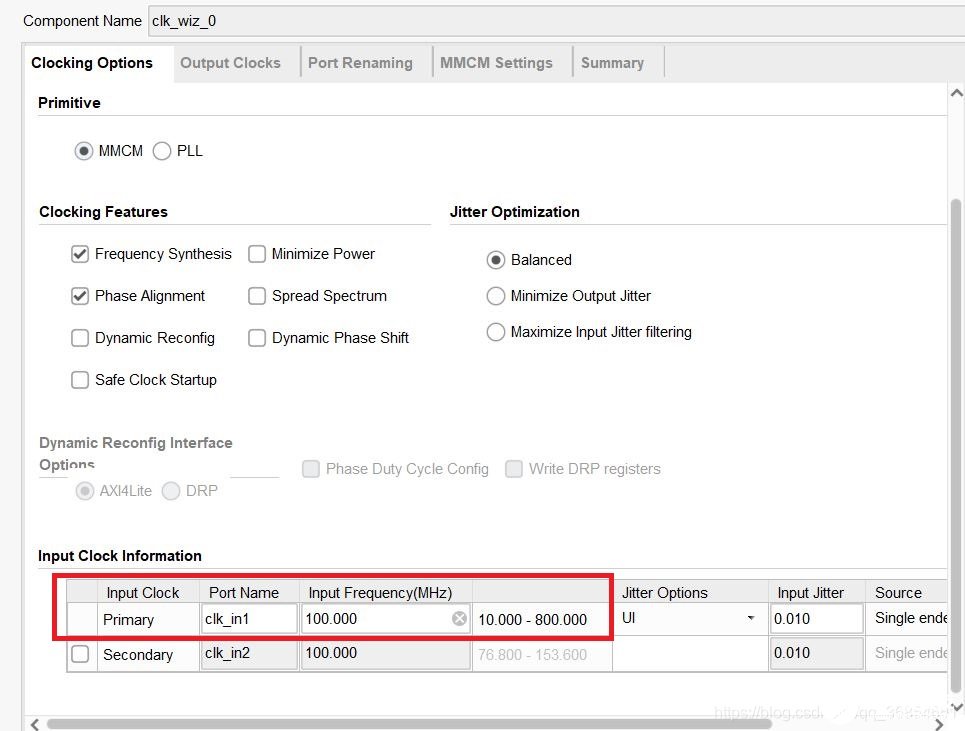

双击该项目打开,根据开发板上晶振频率进行输入时钟配置

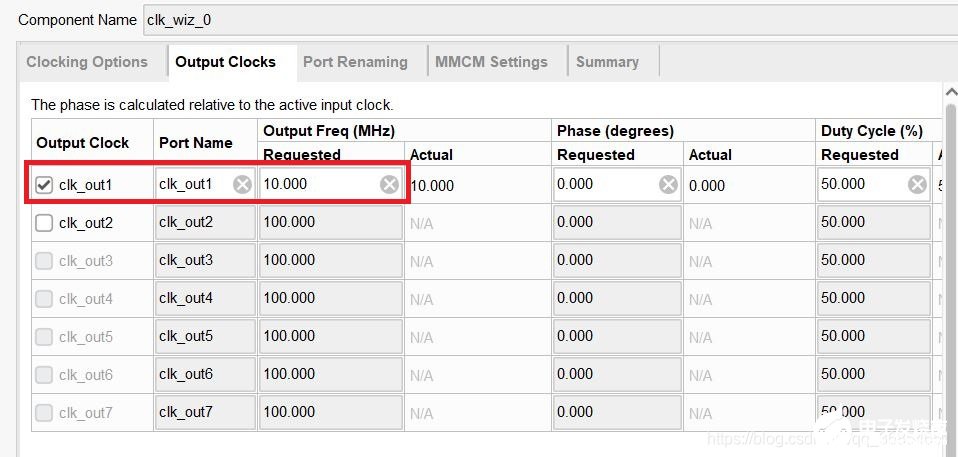

配置需要输出的倍频频率

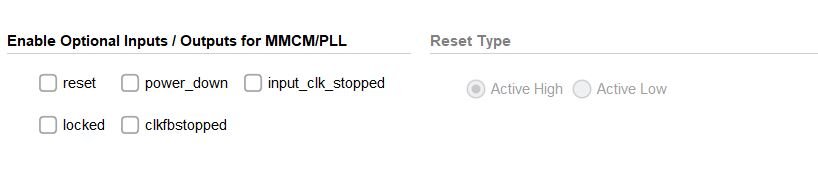

在最下方可选择IP核需要的引脚,我都没用到,因此全取消了(之前有遇到选择reset和lock引脚后IP核不能使用的情况,原因还未弄清楚)。

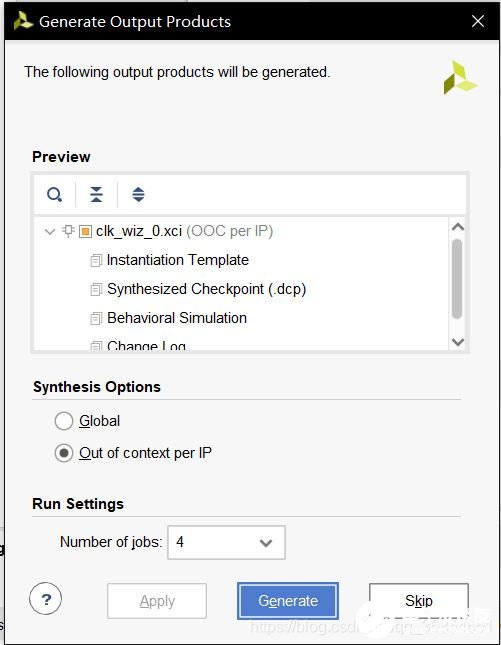

点击OK,并点击Generate,完成Clocking Wizard的配置

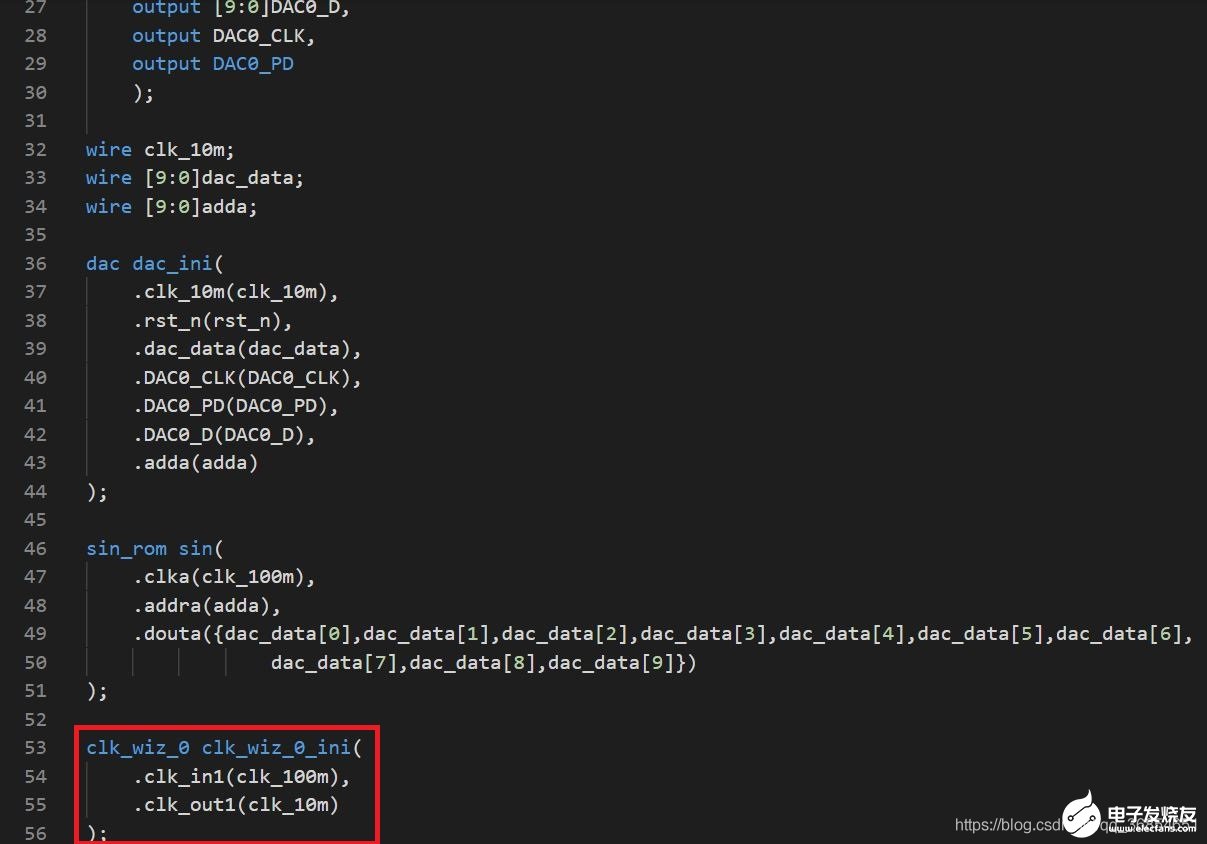

在代码中对IP核进行调用

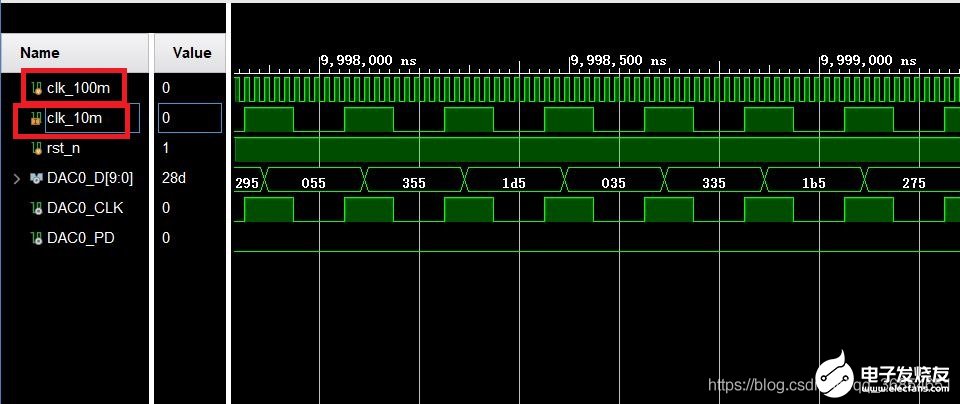

编写TESTBENCH,仿真结果如下

ILA

ILA是用于实时仿真的IP核,在你将bit文件烧入芯片后,可在ILA核中看到你想观察的图像和数据。

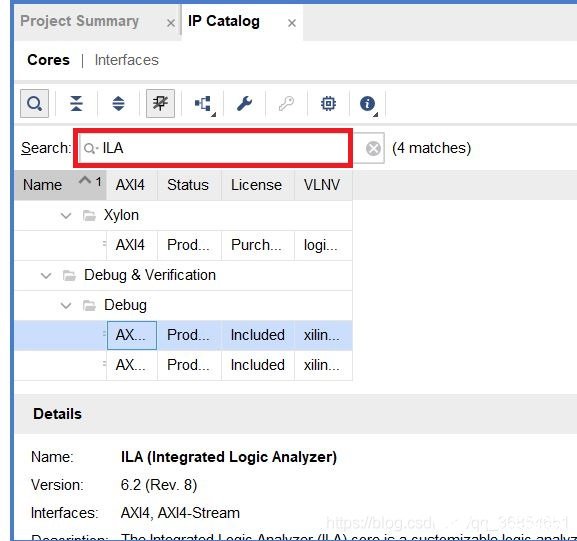

打开IP Catelog,输入ILA

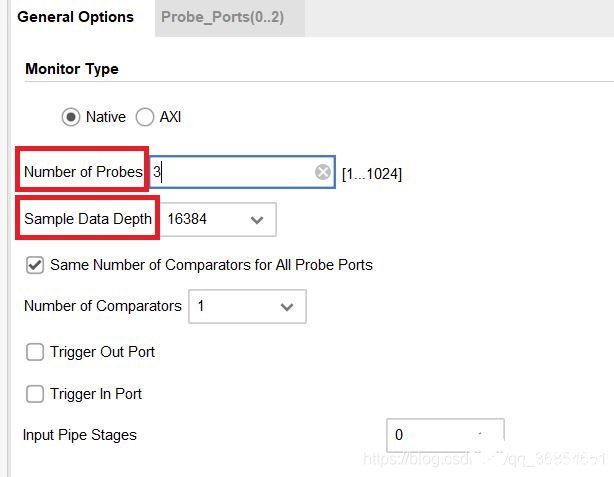

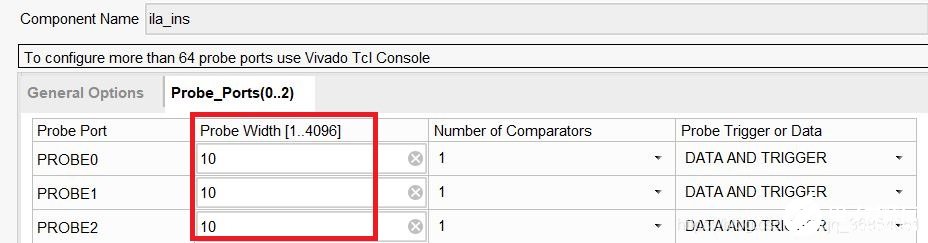

双击打开项目,配置需要观察的端口数,采样的深度

配置观察端口的位数

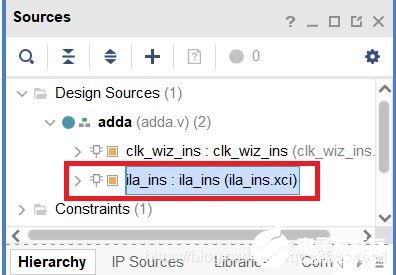

点击OK,和Generate完成IP核配置

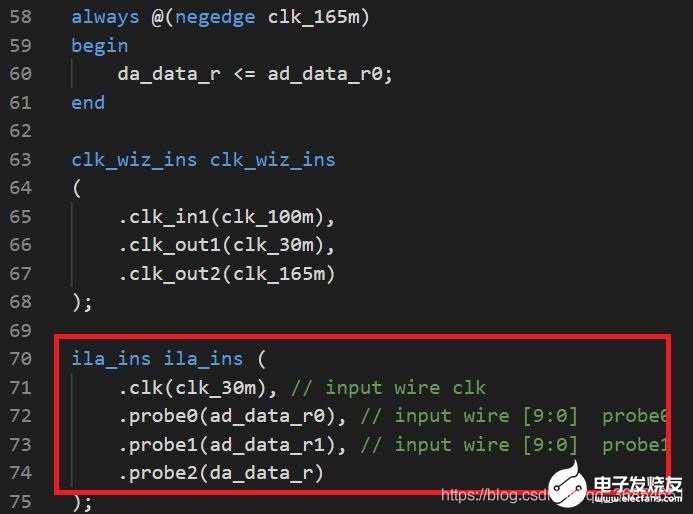

在代码中调用IP核

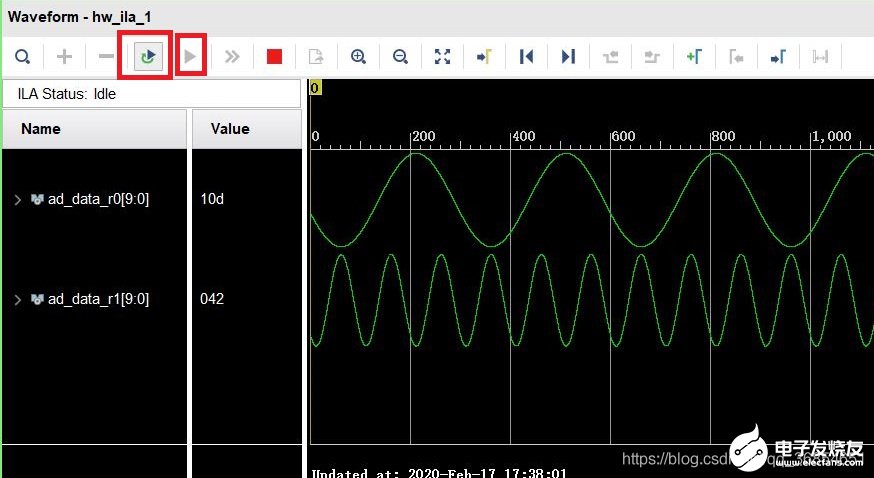

完成工程综合后,下载文件,点击运行和循环,开始观察

Block Memory

该IP核调用片内ROM,可以用来储正弦波,三角波等波形。该IP核引用文件的格式为.coe,因此我们需要先使用Matlab生成一个.coe文件。

打开matlab,新建一个.m文件,输入以下代码生成一个位宽10位,深度1024的正弦波

width=10; %rom的位宽

depth=1024; %rom的深度

x=linspace(0,2*pi,depth); %在一个周期内产生1024个采样点

y_sin=cos(x); %生成余弦数据

y_sin=round(y_sin*(2^(width-1)-1))+2^(width-1)-1; %将余弦数据全部转换为整数

fid=fopen(‘C:\Users\Leixx\Desktop\sin_coe.coe’,‘w’); %创建.coe文件

fprintf(fid,‘%d,\n’,y_sin); %向.coe文件中写入数据

fclose(fid); %关闭.coe文件

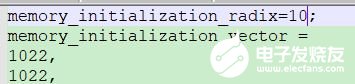

生成文件之后,用notepad++(或UltraEdit)打开,你会看见已经生成好的1024个数据,这时需要在文件的最开始添加下面两句:

memory_initialization_radix=10;

memory_initialization_vector =

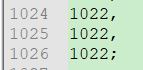

radix表示是十进制显示。之后,在文件的最末尾,将最后一个数据后面的逗号改成分号,点击保存。

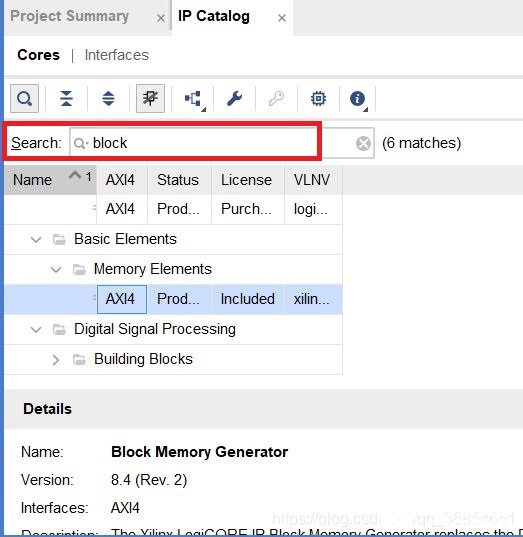

打开vivado,点击IP Catalog,输入block

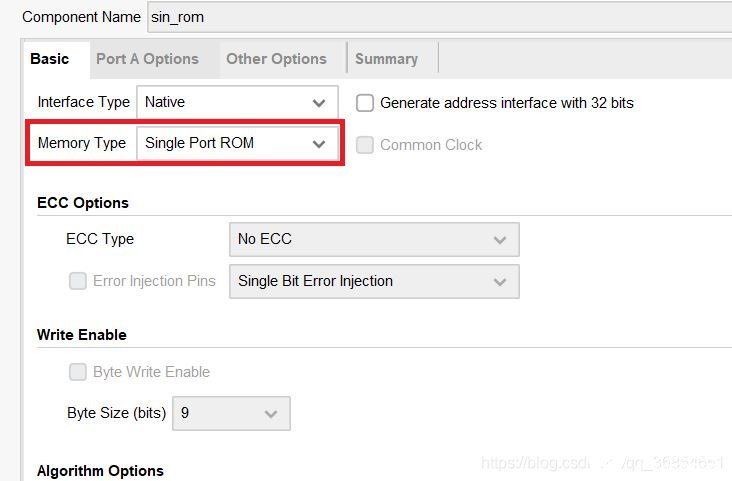

双击打开项目,选择Single port ROM

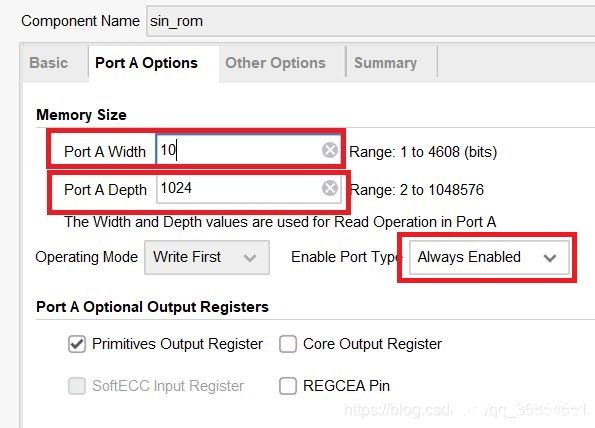

配置要存入的数据位宽和数据深度,我之前生成的是位宽10位,深度1024的数据

选择Always Enanbled,让IP核始终处于工作状态

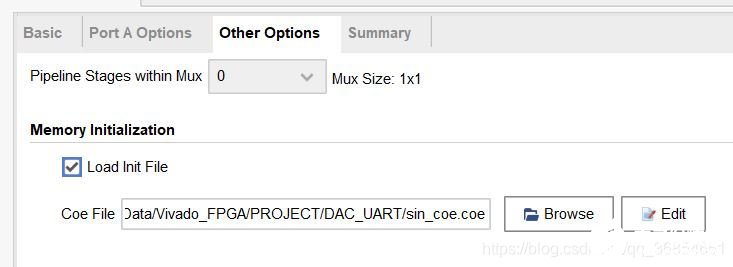

将之前生成好的文件载入IP核

点击OK和Generate,完成IP核配置

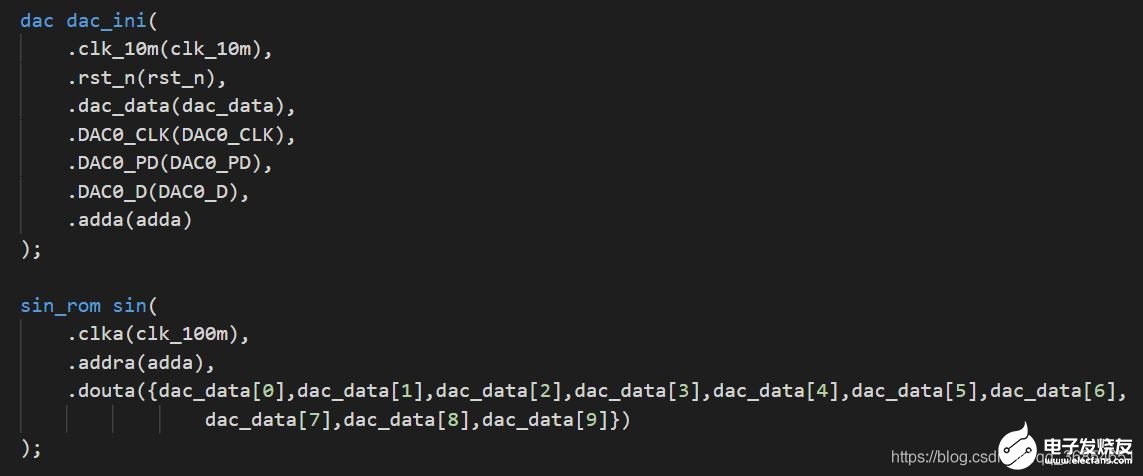

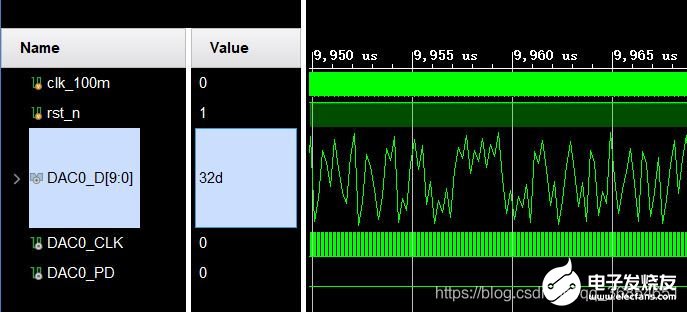

在代码中调用IP核,我这里DAC是低位在前

编写好Testbench后,可以在仿真中看到正弦波,我这里因为低位在前,所以波形杂乱。

以上,便是vivado三种常用IP核的调用。

编辑:lyn

-

ROM

+关注

关注

4文章

579浏览量

89372 -

IP核

+关注

关注

4文章

345浏览量

52096 -

实时仿真

+关注

关注

0文章

35浏览量

8956 -

Vivado

+关注

关注

19文章

860浏览量

71396

发布评论请先 登录

C语言中实现函数宏的三种方式

vcs和vivado联合仿真

Vivado浮点数IP核的握手信号

【干货】一文带你了解CAN、Modbus与LoRa三种通信协议的区别

关于Vivado三种常用IP核的调用详细解析

关于Vivado三种常用IP核的调用详细解析

评论