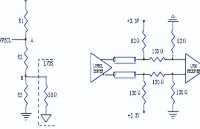

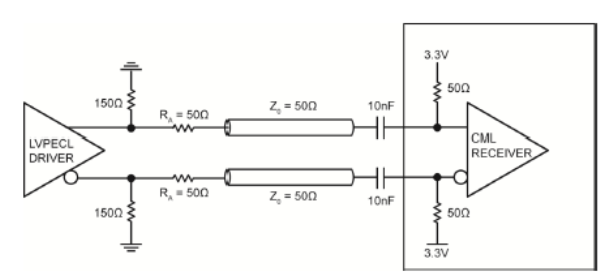

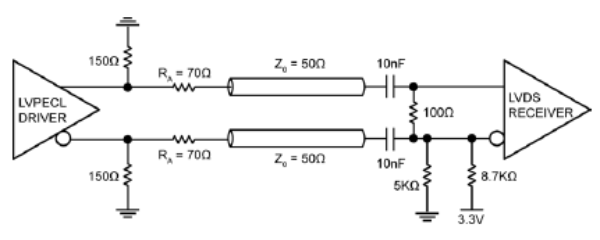

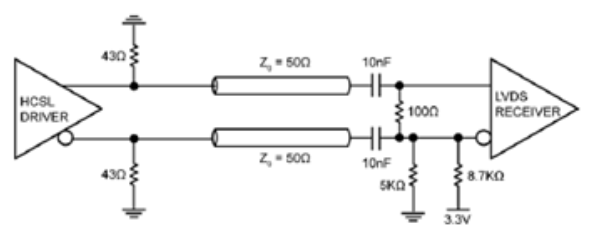

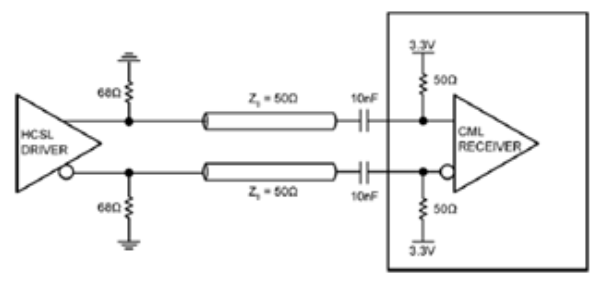

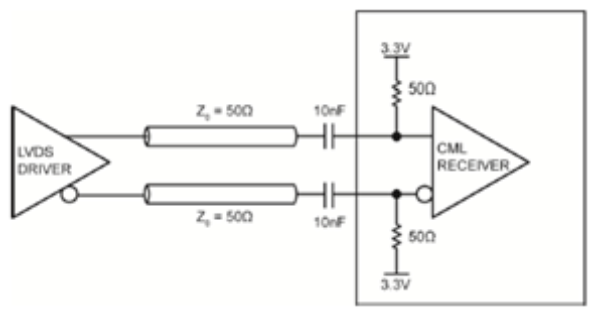

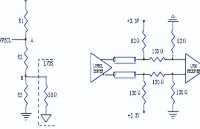

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。 下面详细介绍第二部分:不同逻辑电平之间的互连。 1、LVPECL的互连 1.1、LVPECL到CML的连接 一般情况下

2020-12-20 11:49:31 30005

30005

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。 下面详细介绍第一部分

2020-12-20 11:39:59 41054

41054

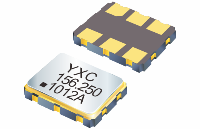

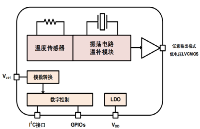

在晶振家族中有一种特殊晶振类型的存在,它就是差分晶振。除了产生单端的振荡信号之外,差分晶振还能输出差分信号。

2023-07-26 14:00:28 2597

2597

其实对于差分晶振的好处有很多,比如差分晶振可以外部电磁干扰(EMI)具有很高的免疫力。一个干扰源对差分信号的每一端的影响程度几乎相同。由于电压差决定了信号的值,两条导线上的任何干扰都将被忽略。

2023-12-25 16:26:40 1278

1278

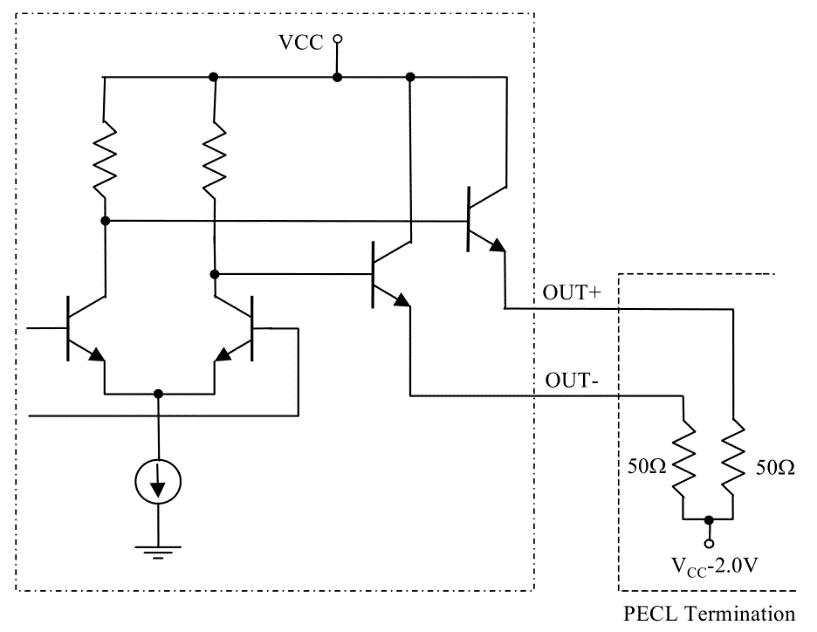

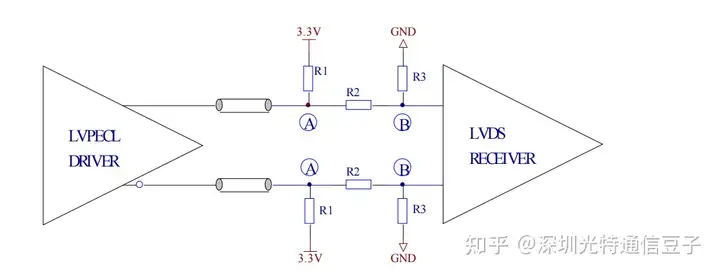

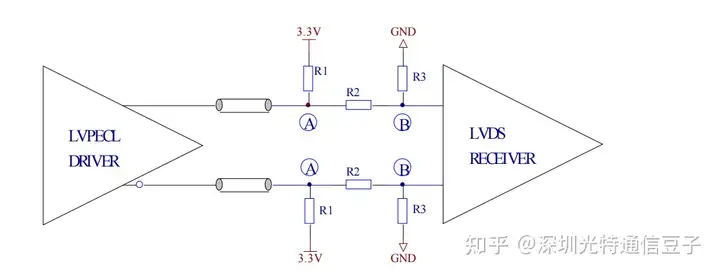

LVPECL电平的差分摆幅较大(典型值约800mV),共模电压较高(约1.3V-1.9V),需外部端接电阻匹配;而LVDS差分摆幅较小(350mV),共模电压较低(约1.2V),且LVDS接收端内置端接电阻。

2025-03-12 17:50:35 1882

1882

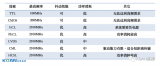

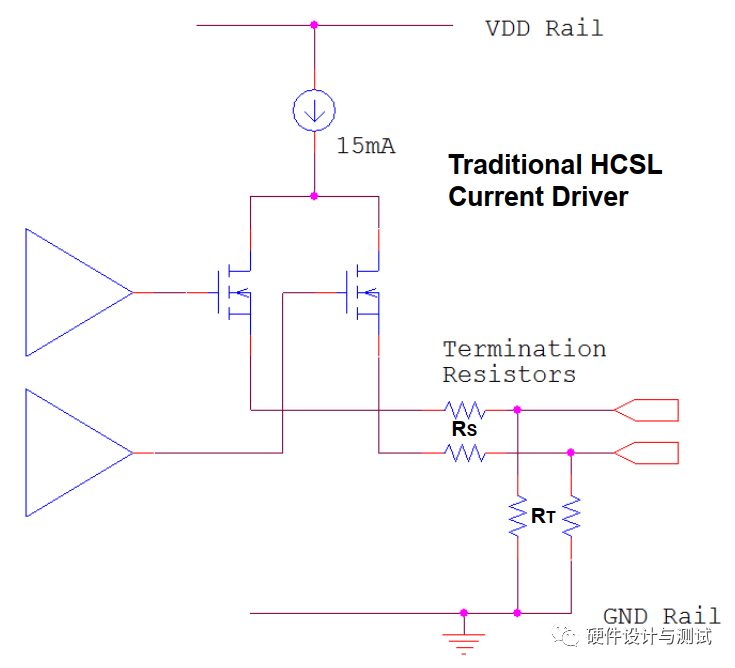

于高速网络系统中,在高速设计中,需要选择电平摆幅窄、支持远距离传输、功耗小的信号电平,LVDS、LVPECL、HCSL等电平具有这些特性,因此称为高速逻辑电平。高速电平一般采用差分技术。

2025-07-07 14:42:05 1305

1305

协议转换器设计中使用 TLK10232 的方法。本文我们将回过头来了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之间转换。系统当前包含 CML 与 LVDS 等各种接口标准

2018-09-13 14:28:38

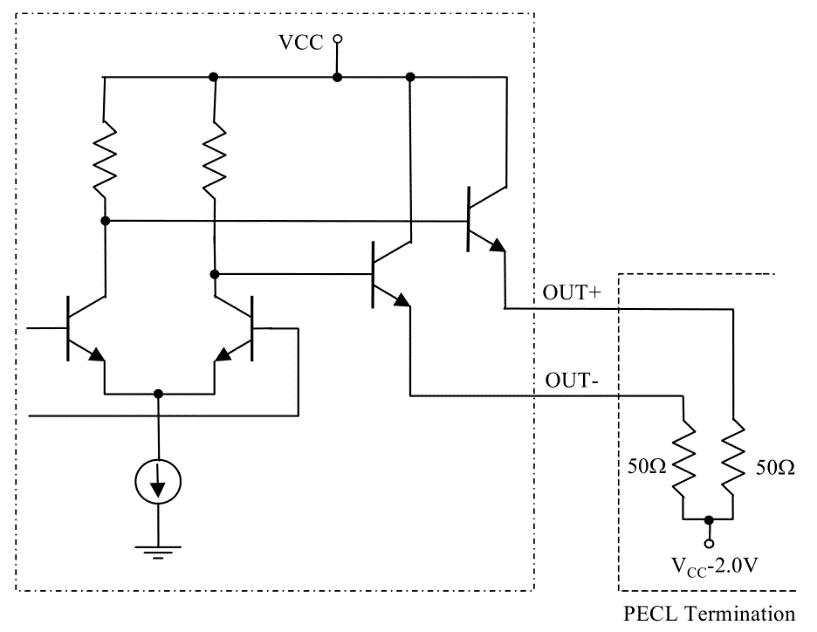

LVPECL(低压正射极耦合逻辑)是一种输入输出(I/O)技术,从半导体工艺无法集成高性能P 型设备与高性能N 型设备起就已出现。因此,在随后的HCSL 和LVDS等高速接口中,需要外部无源器件来

2019-07-08 07:05:43

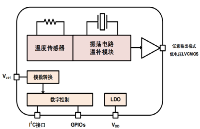

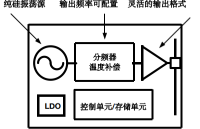

SiTime晶振采用全硅的MEMS技术,由两个芯片堆栈起来,下方是CMOS PLL驱动芯片,上方则是MEMS谐振器,以标准QFN IC封装方式完成。封装完成之后,进行激光打标环节,黑色晶振表面一般打

2017-04-06 14:22:11

SiTime的产品包括高性能差分振荡器、扩频振荡器、压控振荡器和多组输出式时脉产生器,服务于容错云端储存器、企业服务器、10兆以太网交换机等高性能电子系统,及数码相机、LCD高清晰电视、多功能打印机等大批量消费电子。

2019-10-29 09:01:18

模式之外,剩下的参数就和普通有源晶振差不多了.目前市场主流差分晶振都是6脚贴片封装,常见的尺寸有7050和5032,当然SiTime还可以提供更小的3225封装体积.3,差分晶振的好处:①能够很容易

2016-07-16 16:08:15

需要用到固定差分晶振的可以下载哦

2017-02-08 14:52:49

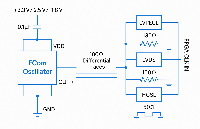

在数据通信、广播、工业控制与同步系统中,电压控制晶体振荡器(VCXO)起着关键频率调谐与时钟同步的作用。FCom富士晶振推出的FVC-3L-PG、FVC-5L-PG、FVC-7L-PG三款差分输出

2025-06-24 17:11:20

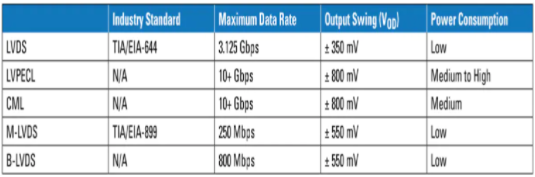

本篇主要介绍常用的差分逻辑电平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。

2021-07-17 19:37:39

各位专家好:近期在用AD9680做设计,资料中有提及时钟输入两种耦合方式:差分CML或者差分LVDS,现请问如果时钟为差分LVPECL的话,交流耦合如何接入呢,外部器件参数如何选择,盼复为谢!!!

2023-12-01 15:25:52

CDCLVP1208RHDR的差分输入管脚外接差分晶振,需要区分差分晶振时钟的P和N吗?

比如差分晶振的CLKP接到CDCLV1208RHDR的INN0, CLKN接到CDCLV1208RHDR的INP0,这样接会有问题吗?

2024-11-12 07:29:16

from 0.15Vpp to 1.3Vpp (50 Ω terminated) can be tied to either of the two differential clock inputs“,

因此想再次确认下,LMK00725是否支持LVDS或者LVPECL的差分交流耦合输入呢?

2024-11-11 07:42:43

出来的cml信号在还原成hdmi信号,接到显示器上。现在有几个问题:

1,hdmi是什么电平?第一次接触,hdmi信号里有几对差分还有几个单端的,差分的信号是不是cml电平?

2,如果差分的是cml电平

2024-12-24 06:34:16

中型数据中心对高频、低抖动、宽温与多电压晶振的需求日益提升,FCO系列差分晶体振荡器凭借丰富封装、输出逻辑选择与优异相位抖动性能,为网络、存储、服务器与边缘系统提供稳定的时钟解决方案。FCO-2L 到 FCO-7L 系列,已成为新一代数据中心关键平台时钟设计的重要支撑。联系我们

2025-07-10 14:11:01

FCom富士晶振针对SFP、QSFP、OSFP等高速光模块推出一系列稳定可靠的差分晶体振荡器,具备低抖动、宽温高精度等特性,满足现代高速通信设备的时钟需求。

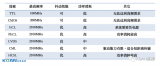

应用平台与参数对照表

模块类型

平台

2025-06-16 15:03:42

FCom FCO系列差分输出晶体振荡器涵盖2.5×2.0至7.0×5.0多种封装,提供LVPECL、LVDS与HCSL三种标准接口,频率支持13.5MHz至220MHz,并具有出色的相位抖动指标

2025-05-30 11:53:48

本文我们将回过头来了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之间转换。系统当前包含 CML 与 LVDS 等各种接口标准。理解如何正确耦合和端接串行数据通道或时钟通道

2022-11-21 07:59:56

如何实现了SPI/ASI的相互转换?

2021-06-08 06:32:48

请问一下如果ad9680的clk和sysref信号采用lvpecl格式输入,交流耦合的话前端网络如何设计。查看官方文档发现只介绍了cml和lvds的交流耦合模式,并没有提到lvpecl的交流耦合问题,希望版主或者设计过的大能给解决解决!!

2023-12-06 06:31:06

很惭愧,俺对基础的东西不是很了解,数字 1和字符 ‘1’ 怎么相互转换 ,因为在LCD1602和TFT彩屏显示涉及到相互转换,总是弄不清楚,请大虾给科普下,‘0’是代表字符 0 吗?

2014-05-26 11:22:18

专业提供各类石英晶体频率元件;1,SPXO可提供SMD7050,5032,3225,全尺半尺型,频率不限,可根据客户要求定制;2,TCXO专注推广GPS产品应用的产品3,差分有源晶体振荡器,专注

2011-03-29 20:50:35

初步设想是LVDS输出端AC耦合,HCSL输入端用端接电阻加偏置。目前HSCL的供电端是0.8V。想问一下这个电平转换电路具体怎么实现呢,还有LVDS的差分峰峰值是能够满足HCSL的输入要求的吧?

2021-08-19 14:50:00

。在选用晶振时,要考虑到电路需要的晶振输出类型,一般分电平输出和差分输出;电平输出:CMOS是最常用的一种输出类型,而差分输出:LVPECL,LVDS常用差分输出类型。不同的输出类型之间可不随便变换

2016-07-01 14:34:10

可编程差分振荡器1.150-2100MHz超宽频率范围,频率任意编程,并精确输出到小数点后6位2.交期灵活3.超低抖动:0.15ps typ.4.输出类型丰富(LVDS、LVPECL、HCSL

2023-07-14 13:42:20

可编程压控晶振(新品)1.可兼容多种电压(1.8V-3.3V)2.宽牵引范围3.输出种类丰富(LVDS、LVPECL、HCSL、CML)4.超低抖动,抗震性强

2023-07-14 13:42:22

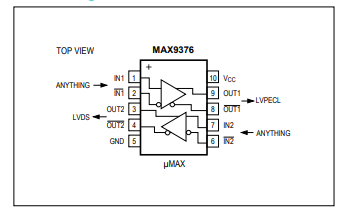

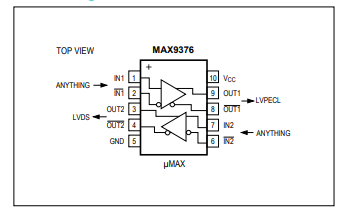

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器

概述

The MAX9376 is a fully differential

2009-12-19 12:11:39 1910

1910

各种进制相互转换

1、其它进制转换为十进制 方法是:将其它进制按权位展开,然后各项相加,就得到相应的十进制数。

2010-09-19 11:29:50 4145

4145

数模、模数相互转化数模、模数相互转化数模、模数相互转化

2016-01-15 15:07:17 8

8 顾名思义就是输出是差分信号的晶振,差分晶振是指输出差分信号使用2种相位彼此完全相反的信号,从而消除了共模噪声,并产生一个更高性能的系统。许多高性能的协议使用差分信号,如SATA,SAS,光纤通信,10G以太网等等。

2017-09-16 09:37:42 8

8 本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

2021-01-07 16:30:00 41

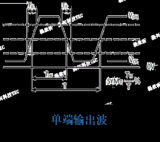

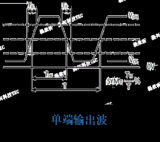

41 模式。单端一般是CMOS、TTL电平信号,只需要一根线输出就好了,优点是走线方便,但缺点也很明显,就是抗干扰能力差,不适合高速信号(100MHZ以上)。 差分一般是LVDS、LVPECL等信号,需要两根线输出。优点是抗干扰能力强,缺点是布线

2021-10-15 15:38:32 2191

2191 模式。单端一般是CMOS、TTL电平信号,只需要一根线输出就好了,优点是走线方便,但缺点也很明显,就是抗干扰能力差,不适合高速信号(100MHZ以上)。 差分一般是LVDS、LVPECL等信号,需要两根线输出。优点是抗干扰能力强,缺点是布线

2021-10-27 16:54:32 5841

5841 常规的差分晶振输出波形均属于方波,且输出功率比较大,驱动能力较强,但谐波分量非常多。这两种输出模式是差分晶振的输出逻辑,两者的相位刚好相反,因此它们能够组成更高性能的系统,同时还能消除共模噪声。差分

2021-10-26 16:40:25 2032

2032 的SOT23-5封装工作温度范围:商业级,工业级,汽车级以及航天或军工级输出:输出逻辑选项(单端TTL/COMS和差分LVDS/LVPECL)和输出使能、扩频、 关断、休眠控制模式提高系统性能以MEMS

2021-11-17 16:46:15 3479

3479

www.sitimechina.com,客户服务热线400-888-2483。SiT9121 是一种高度灵活的可编程差分晶振,支持 LVPECL 和 LVDS 输出信号类型。该差分振荡器覆盖 1 至 220 MHz 之间的任何频率

2021-11-18 18:13:05 3572

3572

的气流下持续运行。SiT9366低抖动差分晶振可解决石英晶振缺陷,满足上述环境需求。SiT9366低抖动差分晶振基于SiTime独特的Elite Platform™,在存在常见环境危害(例如冲击,振动

2021-11-29 15:20:41 2640

2640

www.sitimechina.com,客户服务热线400-888-2483。SiT3372 是SiTime推出的一款低抖动、可编程差分 VCXO(压控振荡器),支持 LVPECL、LVDS 和 HCSL 输出类型,具有高达 ±3145

2021-12-02 17:33:29 9058

9058

架构设计,可提供广泛的功能及快速配置,交货时间非常短。SiT912X 具有采用可编程LVPECL、LVDS、HCSL和CML信号级的差分输出。SiT8008和SiT1602高性能振 荡器具

2022-03-23 15:35:32 2516

2516 到 CML,但是最常用的差分输出信号类型主要包括 LVPECL、LVDS 和 HCSL。通 常,基于石英的差分振荡器的稳定度在±20ppm 至±100ppm 之间。MEMS 差分振荡器可以支持的稳定性低 至±2.5 ppm 的,这种器件的优点保证以太网设计时需要的频率偏移,从而产生最佳的吞吐量。

2022-04-26 13:56:52 5316

5316

关于作者--SiTime样品中心为了加速SiTime MEMS硅晶振产品的应用普及,让中国电子工程师能快速体验MEMS硅晶振的高稳定性、高可靠性、超小封装、超低功耗、超低抖动等更多优势,SiTime

2022-06-02 14:58:31 3002

3002 关于作者--SiTime样品中心为了加速SiTime MEMS硅晶振产品的应用普及,让中国电子工程师能快速体验MEMS硅晶振的高稳定性、高可靠性、超小封装、超低功耗、超低抖动等更多优势,SiTime

2022-06-14 10:23:37 3104

3104 获得连接:LVPECL、VML、CML、LVDS 与子 LVDS 之间的接口连接

2022-11-04 09:52:13 6

6 延迟时间慢,功耗较低,噪声容限大等优点。差分晶振我们常见的输出模式有LVDS,LVPECL,HCSL,CML。那么LVCMOS属于差分晶振的输出模式吗?答案是否定的,

2022-07-07 14:29:12 2949

2949

差分晶振(Differential Crystal Oscillator)是一种基于晶体谐振器的振荡器,具有独特的工作原理和广泛的应用领域。本文将详细解释差分晶振的工作原理、应用领域和参数。

2023-06-28 16:13:42 5257

5257

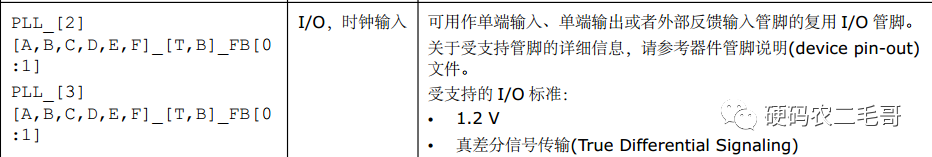

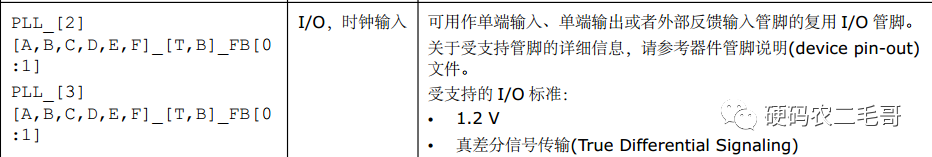

几年前FPGA时钟只需要连接一个单端输入的晶振,非常容易。现在不同了,差分时钟输入,差分信号又分为LVDS和LVPECL,时钟芯片输出后还要经过直流或交流耦合才能接入FPGA,有点晕了,今天仔细研究一下。

2023-08-21 11:28:44 14322

14322

晶振的输出波形为单端输出(Sine/Clipped Sine, CMOS/TTL) 和差分输出(LVPECL, LVDS, HCSL)。差分输出可以满足高速数据传输,应用于高速计算机,数字通信系统,雷达,测量仪器,频率合成器等。

2023-08-25 11:01:08 2732

2732

手机、广播,电视等方式接收信息。而在远离地球的地方,比如在船上、飞机上、山区或者荒凉的地区,网络通话就无法使用,而只能使用卫星通话。 下面将分别介绍卫星通话和网络通话的原理和特点,以及如何实现相互转换。 卫星通话

2023-08-30 17:27:10 2856

2856 HCSL:高速电流控制逻辑(High-speed Current Steering Logic)是Intel为PCIe参考时钟定义的差分时钟,用于PCIe2.0电气规范中定义对RefClk时钟所定义

2023-09-15 14:39:54 16119

16119

对于定制差分晶振应用电路方案定制细节方面要和开发公司一起协商,因为在定制的过程中应该确定企业的需求。尤其是差分晶振应用电路方案也是执行方案的,目前在执行的时候有能力的企业可以自己执行差分晶振应用电路方案

2023-10-24 18:03:58 1197

1197

作为整个设计中重要的时钟选择,FPGA调制过程是两个相位完全相反的信号,来消除共模噪声,所以一般采取外部晶体振荡器,来实现一个更高性能的系统。在高速设计中,需要选择电平摆幅窄、支持远距离传输、功耗小的信号电平,LVDS、LVPECL、CML、HCSL等电平具有这些特性,因此称为高速逻辑电平。

2023-11-14 16:11:42 2754

2754

,并将其差分输出,以提供高度稳定的时钟信号。差分晶振具有许多优点和实际作用,下面将详细介绍。 首先,差分晶振具有较低的相位噪声。晶体振荡器的相位噪声往往受到振荡器的供电电压和温度的影响。而差分晶振的两个振荡器采用差分方式输出信号,可以有效地抵消供电电压

2023-11-17 11:31:54 1355

1355 其实在制作差分晶振电路图的时候不同的公司技术也是不同的,一般在选择这列公司的时候应该注重技术,这也是选择一个合适的公司。在网上找差分晶振是比较常见的方式

2023-12-08 17:23:26 1073

1073

差分晶振顾名思义就是输出是差分信号的晶振,差分晶振是指输出差分信号使用两种相位彼此完全相反的信号,从而消除了共模噪声,并产生一个更高性能的系统.许多高性能的协议使用差分信号。

2023-12-28 10:39:02 1535

1535 什么是差分晶振 差分晶振的优势 差分输出与单端输出的差别 差分晶振,也被称为差模晶振或差分输出晶振,是现代电子设备中常用的一种晶振结构。它通过两个需配对的晶体振荡器单元来产生输出信号。差分晶振具有

2024-01-18 11:30:06 2361

2361 使用差分晶振有什么好处呢? 差分晶振是一种使用两个晶体来实现信号产生的技术。相比于传统的单端晶振,差分晶振具有以下几个优势: 1. 抗干扰能力强:差分晶振采用差分方式进行信号生成,因此对于环境中

2024-01-23 16:43:00 1103

1103 差分晶振电路图如何制作 影响差分晶振价格的原因 差分晶振电路图制作步骤: 差分晶振电路图可以用于电子设备的时钟电路、通信系统、射频收发模块等领域。以下是制作差分晶振电路图的步骤: 收集所需材料

2024-01-23 16:43:06 1472

1472 差分晶振怎么测量 差分晶振是一种用于产生高稳定性的时钟信号的器件,它广泛应用于各种电子设备中,包括计算机、通信设备和消费电子产品等。在设计和制造过程中,差分晶振的质量和性能测试非常关键,本文将详细

2024-01-23 16:43:08 1900

1900 差分晶振的输出波形解析 差分晶振是一种常用于数字电路中的时钟信号产生器,它能够提供稳定的、高精度的时钟信号。在本文中,我们将详细讨论差分晶振的输出波形,包括波形的特点、产生方式以及应用场景等方面

2024-01-25 13:51:33 2152

2152 电子发烧友网站提供《SN65CML100D 1.5 Gbps LVDS/LVPECL/CML-TO-CML转换器/中继器数据表.pdf》资料免费下载

2024-06-27 10:47:16 0

0 为:100.000000MHz,小体积晶振尺寸:7.0x5.0x1.6mm,14垫脚贴片品振,HCSL输出差分晶振,有源晶振,电源电压2.5V/3.3V,石英晶振

2024-07-02 17:24:17 0

0 爱普生LVDS差分晶振MG7050VAN,X1M0004210003,高频振荡器6G无线晶振,日本进口晶振,EPSON爱普生晶振型号:MG7050VAN,编码为:X1M0004210003,频率

2024-07-04 11:28:10 0

0 电子发烧友网站提供《SN65LVELT23 3.3双通道差分LVPECL/LVDS缓冲器至LVTTL转换器数据表.pdf》资料免费下载

2024-07-08 14:37:02 0

0 电子发烧友网站提供《SN65EPT23 3.3V ECL差分LVPECL/LVDS至LVTTL/LVCMOS转换器数据表.pdf》资料免费下载

2024-07-08 10:18:51 0

0 替代SiTime,国产高性能晶振/温补晶振用于定位器

2024-07-30 09:58:53 1091

1091

固态硬盘SSD最重要的不同之处在于可靠性,企业级SSD就是固态硬盘SSD,它可以在企业级硬盘领域发挥具有7*24小时不间断作业的能力,由于企业级SSD需要提供一种低功耗差分晶振,价格便宜,输出

2024-08-02 16:32:44 0

0 国产高性能晶振/温补晶振兼容SiTime用于可穿戴设备

2024-08-15 09:55:34 953

953

兼容SiTime,国产高性能晶振/温补晶振交换机应用方案

2024-08-30 09:55:30 927

927

差分晶振全称是Differential Output Crystal Oscillator,高频差分多路输出的振荡器。差分晶振是一种输出差分信号的有源晶振,差分信号输出2路相位完全相反的信号,从而

2024-09-06 11:36:41 1416

1416 替代SiTime,国产差分硅振在光电转换器中的应用

2024-09-11 09:55:05 988

988

差分晶振是一种有源晶体振荡器,通过将晶体振荡器中的振荡信号分成两个相位相反的输出信号,并通过差分放大电路进行放大和处理,产生稳定的差分输出信号。差分晶振具有较好的抗干扰能力,能提供更稳定、更精确的时钟信号,广泛应用于通信网络、数据中心、汽车电子、工业自动化、测试测量、医疗设备等领域。

2024-09-20 11:05:31 2930

2930

差分晶振是一种特殊的晶体振荡器,它通过输出两个相位相反的信号来消除共模噪声,从而实现更高性能的系统。这种设计使得差分晶振在高频高速网络电子设备中特别受欢迎,因为它们能够提供高性能、低功耗和低噪声

2024-09-25 16:54:08 0

0 国产晶振/温补晶振兼容SiTime广泛用于工业机器视觉

2024-10-22 09:46:52 947

947

差分硅振替换SiTime产品应用于SSD,相位抖动低于350fs

2024-11-08 09:41:23 845

845

国产晶振/温补晶振替换SiTime用于商业显示屏

2025-03-18 10:02:52 738

738

MAX9376是全差分、高速、LVDS/任何输入至LVPECL/LVDS双通道转换器,适用于高达2GHz的信号速率。一个通道是LVDS/任何输入至LVPECL转换器,另一个通道是LVDS/任何输入至LVDS转换器。MAX9376具有超低的传播延迟和高速度,因此非常适合各种高速网络路由和背板应用。

2025-05-16 14:57:07 881

881

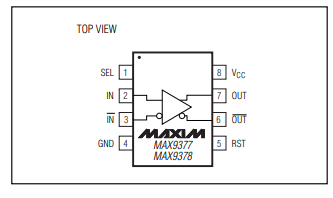

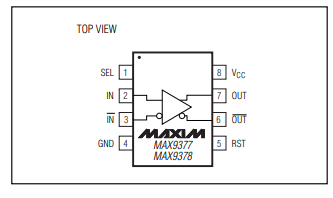

MAX9377/MAX9378是一种全差分、高速、低抖动的任意电平到LVPECL/LVDS的转换器,具有有四分频选择引脚。其极低的传输延迟和高速等特性,尤其适合于多种高速网络路由和背板应用,在非分频模式下工作速度高达2GHz。

2025-05-16 15:12:45 3942

3942

MAX9374和MAX9374A是为电讯应用而设计的2.0GHz差分LVPECL到LVDS电平转换器,具有250ps的传输延迟。差分输出信号符合ANSI TIA/EIA-644 LVDS标准。输入

2025-05-19 10:43:28 742

742

FCom FCO系列差分输出晶体振荡器涵盖2.5×2.0至7.0×5.0多种封装,提供LVPECL、LVDS与HCSL三种标准接口,频率支持13.5MHz至220MHz,并具有出色的相位抖动指标

2025-06-09 14:57:20 2300

2300

FCom富士晶振提供FVC-3L/5L/7L-PG系列差分VCXO,支持LVPECL/LVDS输出,低相位抖动,适用于光通信、工业控制、数据存储等领域的高精度时钟应用。

2025-06-26 11:00:00 1205

1205

在高速光通信系统中,LVPECL(低压正射极耦合逻辑)、PECL(正射极耦合逻辑)与 LVDS(低压差分信号)是常用的高速接口电平标准。LVPECL/PECL 以高速度、低噪声特性广泛应用于光模块

2025-08-08 10:48:46 1088

1088

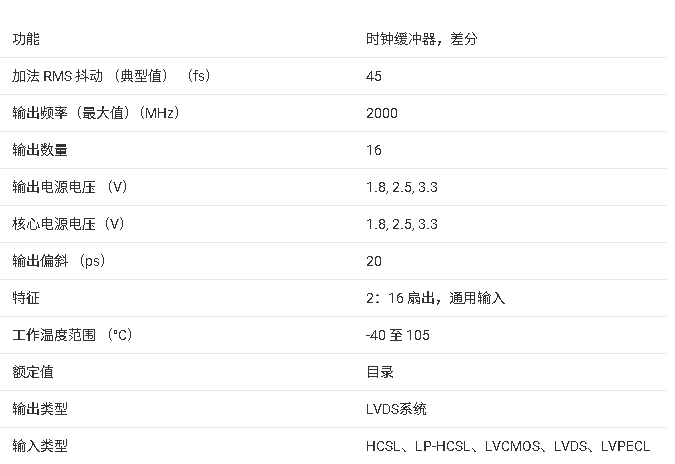

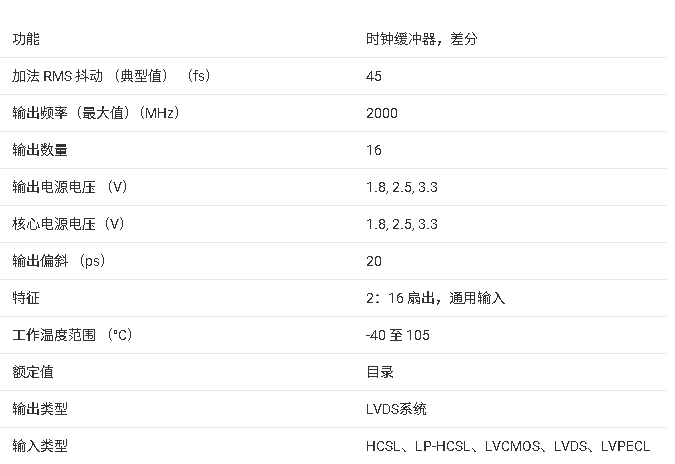

(OUT0至OUT15)。LMK1D121x 系列可以接受两个时钟源进入输入多路复用器。输入可以是LVDS、LVPECL、LP-HCSL、HCSL、CML或LVCMOS。

2025-09-11 14:45:27 701

701

(OUT0至OUT15)。LMK1D121x 系列可以接受两个时钟源进入输入多路复用器。输入可以是LVDS、LVPECL、LP-HCSL、HCSL、CML或LVCMOS。

2025-09-11 14:59:56 769

769

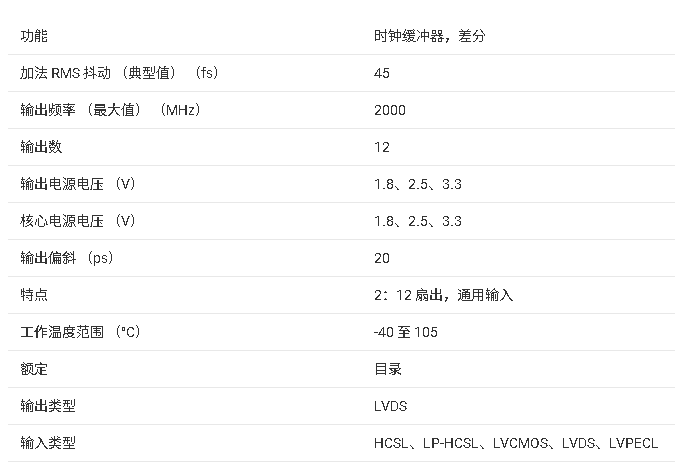

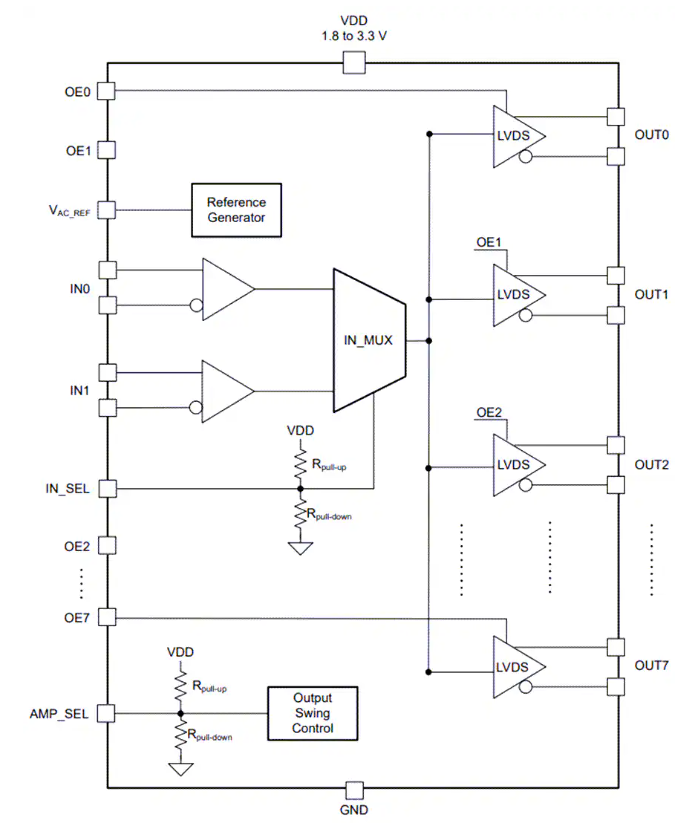

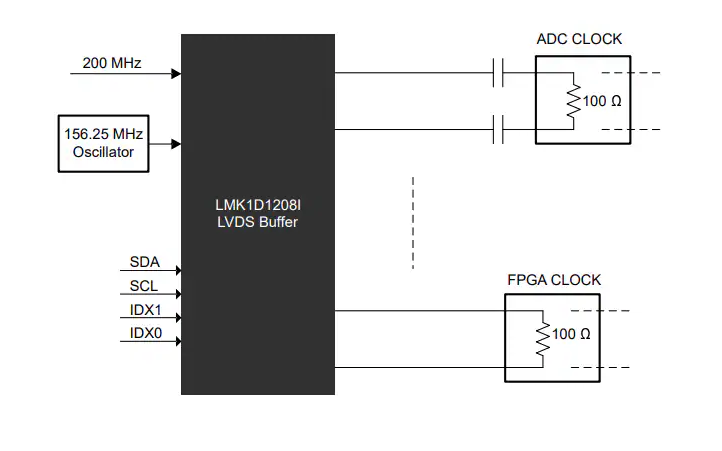

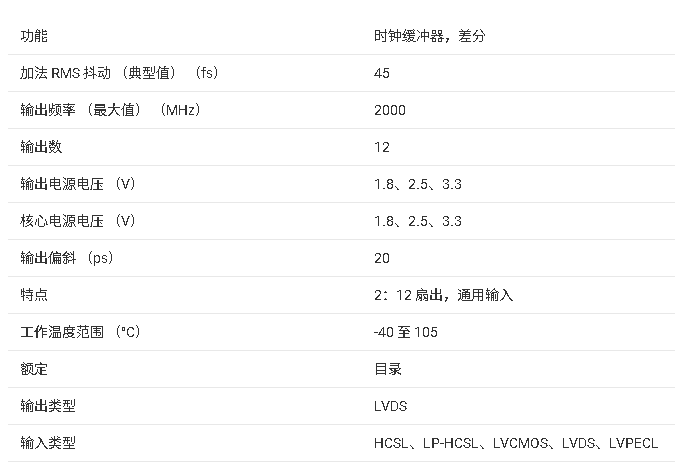

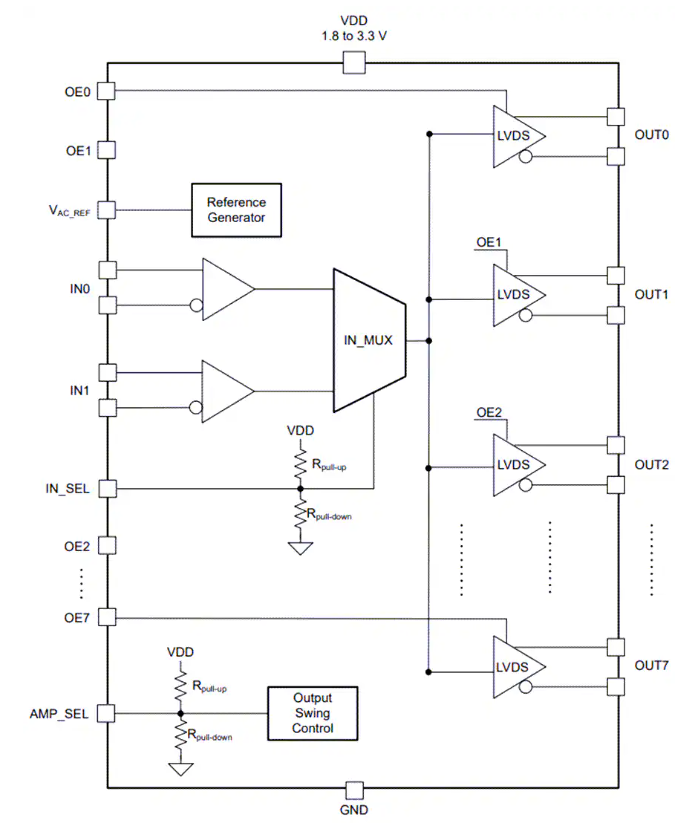

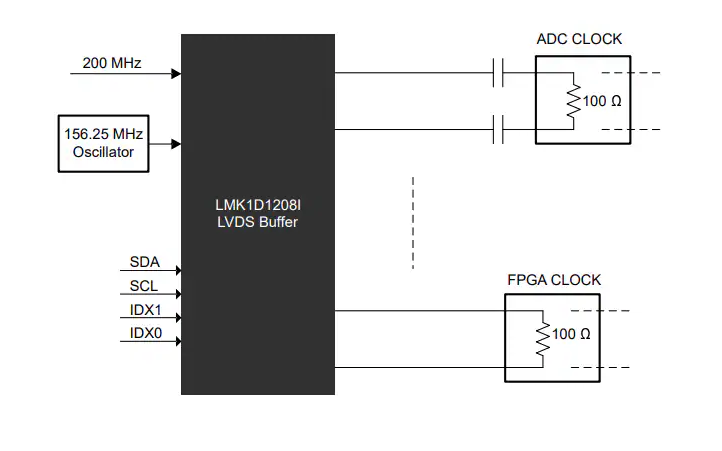

Texas Instruments LMK1D1208P 8通道输出LVDS时钟缓冲器将两个中的一个可选时钟输入(IN0和IN1)分配给八对差分LVDS时钟输出(OUT0至OUT7)。通过超小延迟实现时钟分配。输入可以为LVDS、LVPECL、LVCMOS、HCSL或CML。

2025-09-18 09:52:54 651

651

Texas Instruments LMK1D1208I I^2^C低附加抖动 LVDS缓冲器具有两个输入和八对差分LVDS时钟输出(OUT0到OUT7),且时钟分配偏差最小。输入可以为LVDS、LVPECL、LVCMOS、HCSL或CML。

2025-09-19 09:55:23 753

753

差分晶振,也被称为差模晶振或差分输出晶振,是现代电子设备中常用的一种晶振结构。它通过两个需配对的晶体振荡器单元来产生输出信号。差分晶振具有许多优势,而其差分输出与单端输出也有一些明显的区别。

2025-09-24 09:22:40 1008

1008 1、首先是管脚封装不同,普通晶振是4脚、差分晶振是6脚。

2、其次是输出信号不同,普通是单端输出,差分则是差分输出。

2025-11-24 16:57:03 588

588

深入解析SN65EPT23:3.3V ECL差分LVPECL/LVDS到LVTTL/LVCMOS转换器 在电子设计领域,信号电平转换是一个常见且关键的需求。今天我们来详细探讨德州仪器(TI

2025-12-24 17:45:12 480

480 SN65CML100具备强大的电平转换功能,能够将LVDS或LVPECL信号转换为CML信号,同时实现CML信号的中继。其高达1.5 Gbps的信号速率,足以满足大多数高速

2025-12-30 14:15:02 89

89

电子发烧友App

电子发烧友App

评论