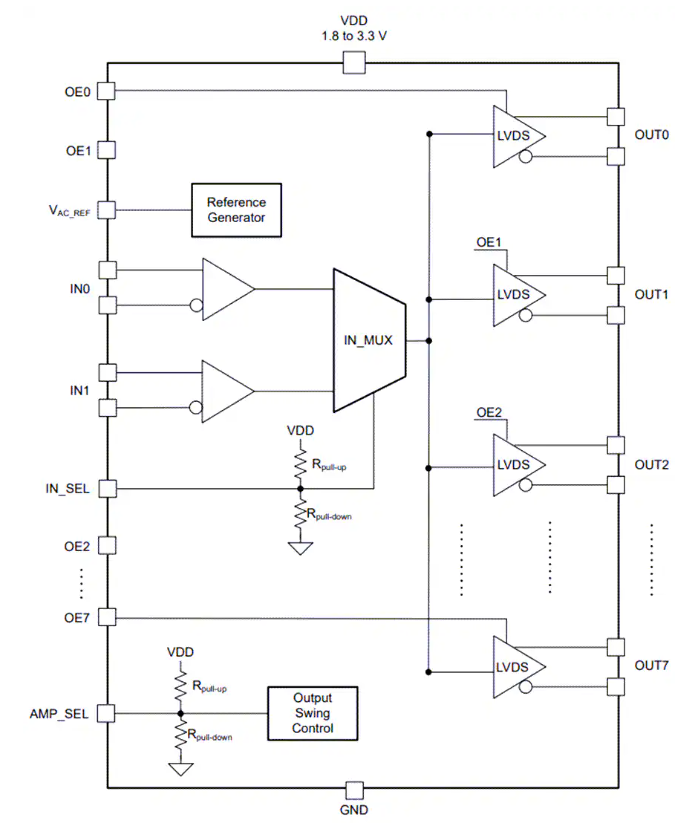

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。

下面详细介绍第二部分:不同逻辑电平之间的互连。

1、LVPECL的互连

1.1、LVPECL到CML的连接

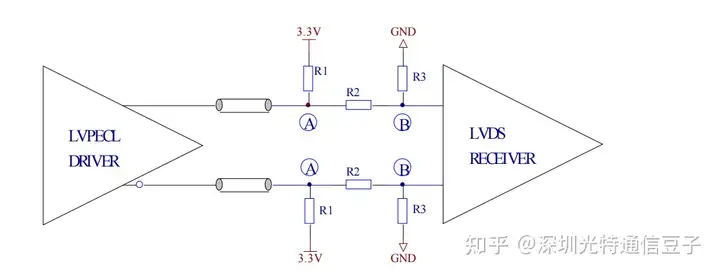

一般情况下,两种不同直流电平的信号(即输出信号的直流电平与输入需求的直流电平相差比较大),比较提倡使用AC耦合,这样输出的直流电平与输入的直流电平独立。

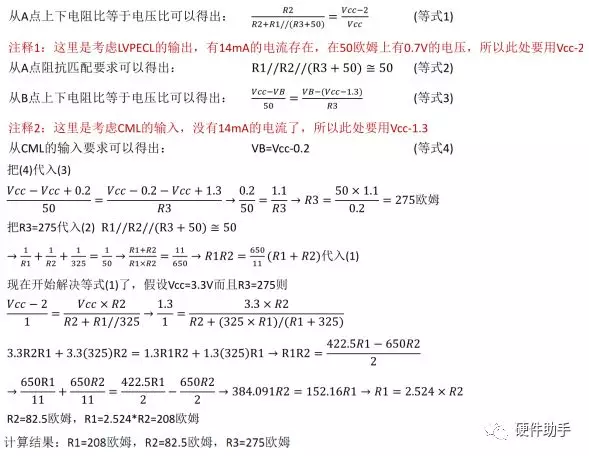

1.1.1、直流匹配

在LVPECL到CML的直流耦合连接方式中需要一个电平转换网络。该电平转换网络的作用是匹配LVPECL的输出与CML的输入共模电压。一般要求该电平转换网络引入的损耗要小,以保证LVPECL的输出经过衰减后仍能满足CML输入灵敏度的要求;另外还要求从LVPECL端看到的负载阻抗近似为50Ω。

直流耦合

如果要连接LVPECL到CML,需要增加如上图所示的电阻网络来进行电平转换,从而同时满足LVPECL的输出和CML的输入要求。下一步计算同时满足LVPECL的输出和CML的输入要求的R1、R2和R3的数值。

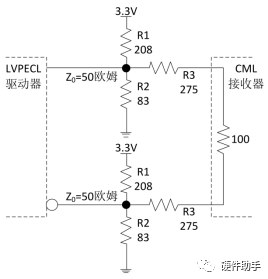

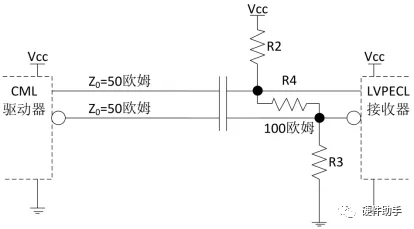

1.1.2、交流匹配

在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取范围可以从142Ω到200Ω。如果LVPECL的输出信号摆幅大于CML的接收范围,可以在信号通道上串一个25Ω的电阻,这时CML输入端的电压摆幅变为原来的0.67倍。(LVPECL输出摆幅600-1000mV,CML输入摆幅400-1000mV)

如果LVPECL输出800mV>CML输入400mV,需要用额外的电阻降低电压幅度,此时需要R2≈50Ω。

交流耦合

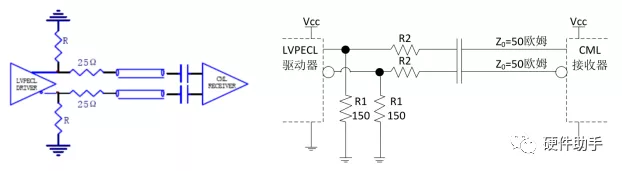

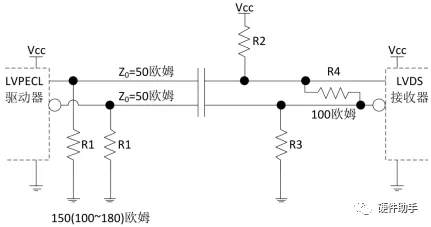

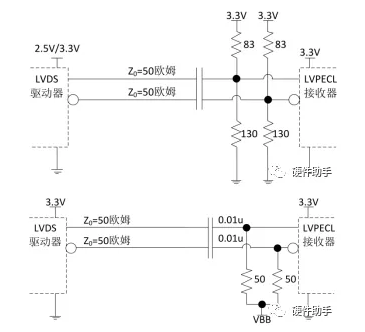

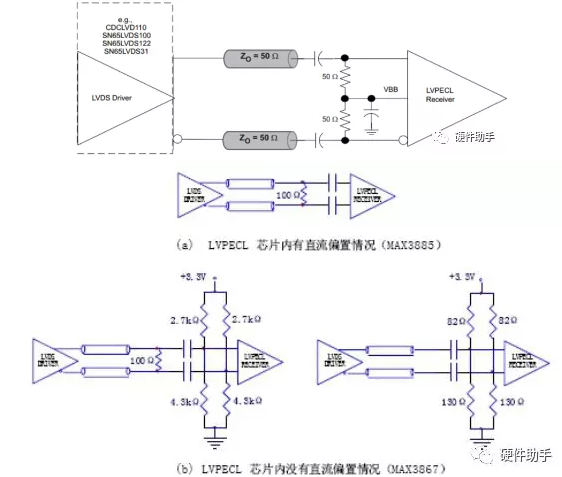

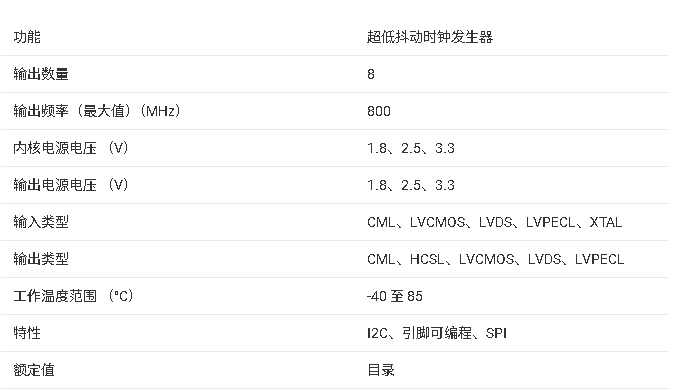

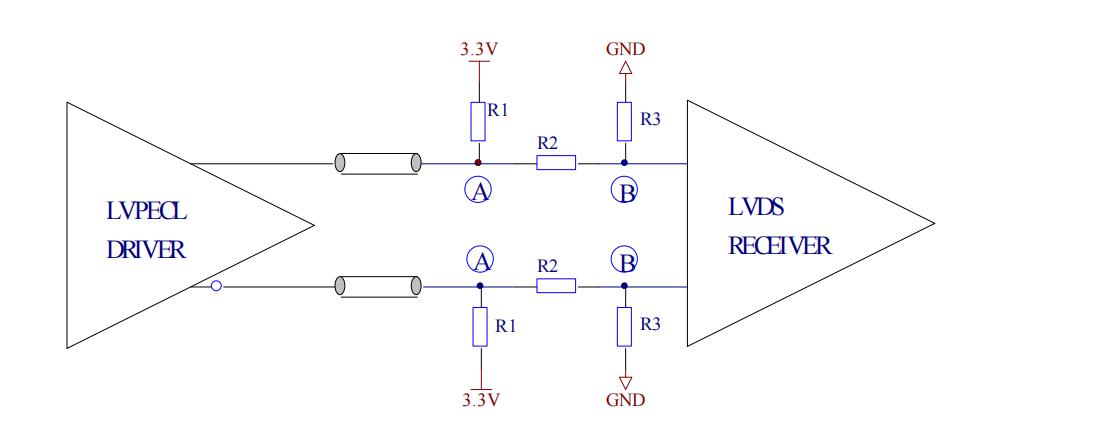

1.2、LVPECL到LVDS的连接

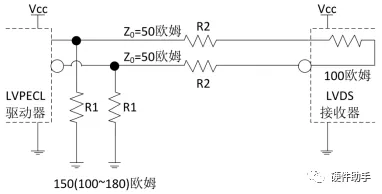

1.2.1、直流匹配

LVPECL到LVDS的直流耦合结构需要一个电阻网络,设计该网络时有这样几点必须考虑:首先,我们知道当负载是50Ω接到Vcc-2V时,LVPECL的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL输出信号经衰减后仍能落在LVDS的有效输入范围内。注意LVDS的输入差分阻抗为100Ω,或者每个单端到虚拟地为50Ω,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等。

直流耦合

沿用130欧姆和83欧姆的模式,由于LVPECL的差分幅度一般大于LVDS的输入要求,所以对83欧姆进行了分压。这个电路既减少了交流摆幅到LVDS能承受的范围,也把直流偏置电压到LVDS需要的1.2V左右。

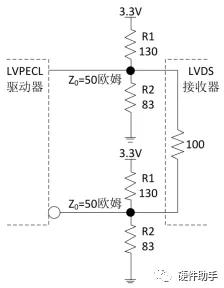

直流耦合

还有一种分压方式如下,摆幅被压缩了,但是直流偏置电压依然是LVPECL的VCC-1.3V。

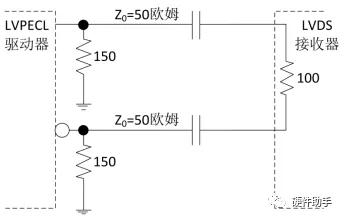

直流耦合

如果LVDS输入端可以承受比较大得差分电压(大部分LVDS接收器可以承受LVPECL输出的信号幅度),而且能承受VCC-1.3V的直流偏置电压,则不需要电阻分压了。

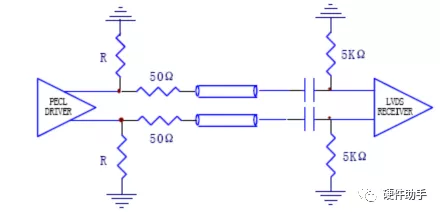

1.2.2、交流匹配

由于LVDS芯片一般内置100欧姆匹配和偏置,直接下拉后加电容即可。

交流耦合

如果LVDS接收端没有内置偏置和匹配电阻,就需要外接提供100欧姆匹配和K级别电阻提供1.25V的直流偏置。

交流耦合

交流耦合

在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取范围可以从142Ω到200Ω。同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS的输入端到地需加5KΩ电阻,以提供共模偏置。

交流耦合

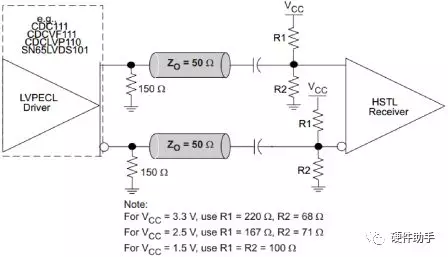

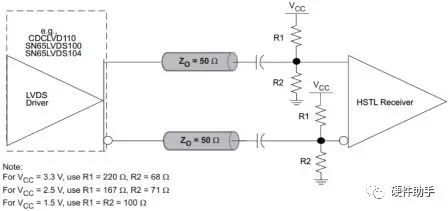

1.3、LVPECL到HSTL的连接

150Ω电阻用作LVPECL输出的直流偏置(VCC-1.3V),也提供了一个源电流的直流通路。在HSTL接收端,R1和R2被用作戴维南端接,阻抗为50Ω(R1//R2),同时也设定了共模电压(VCM=0.75V)。

2、CML的互连

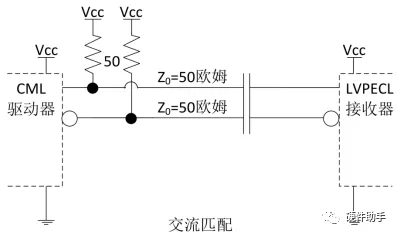

2.1、CML到LVPEL的连接

通常情况下,建议CML驱动LVPECL时采用交流匹配,不采用直流匹配。

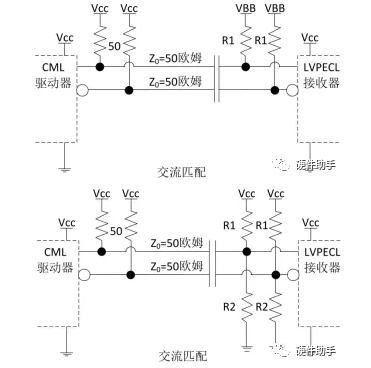

2.1.1、50欧姆上拉匹配

如果LVPECL接收器的输入带有偏置,则可以通过电容直连。CML输出上拉50欧姆作为直流偏置。

2.1.2、50欧姆上拉+偏置

如果LVPECL接收器的输入不带有偏置,则需要用外部电阻提供偏置电压。

推荐使用的交流匹配方式如下:

交流耦合

交流耦合

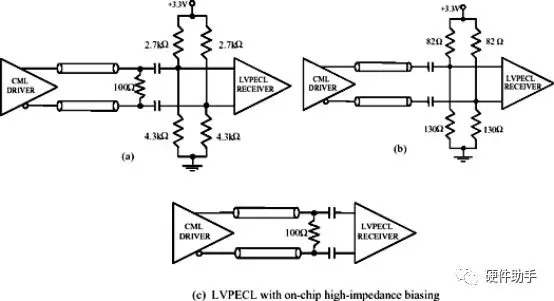

2.2、CML到LVDS的连接

2.2.1、直流匹配

LVDS的输入侧支持1.25±1V的直流电平,如果CML的输出在这个范围内则可以直接连接。

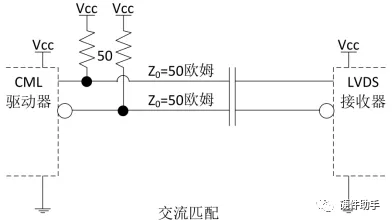

2.2.2、交流匹配

如果LVDS输入内置直流偏置则如图连接。

如果LVDS输入没有内置直流偏置则需要增加直流偏置。

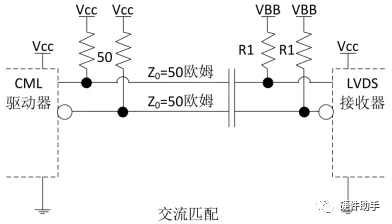

2.3、CML到HSTL

CML和HSTL的互连推荐采用交流耦合。

3、LVDS的互连

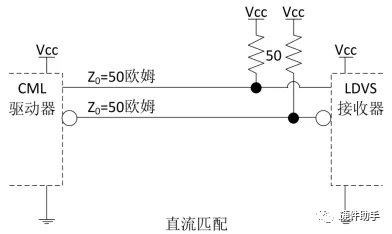

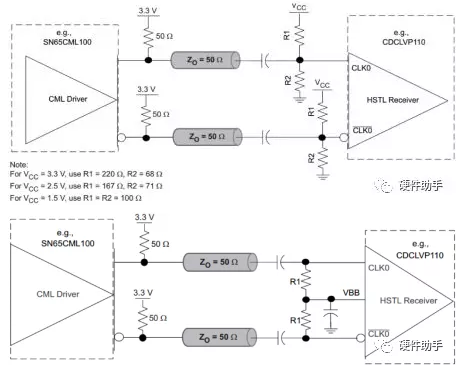

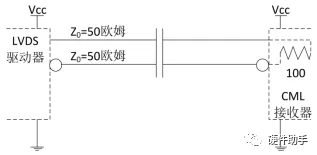

3.1、LVDS到CML的连接

一般情况下,不会存在LVDS与CML之间的对接,因为CML电平一般用在高速信号,如2.5G/10G等场合。而LVDS一般很难用在那么高的速率。

通常情况下,建议LVDS驱动CML时采用交流匹配。确保输出的交流幅度是否落在输入交流幅度之内。

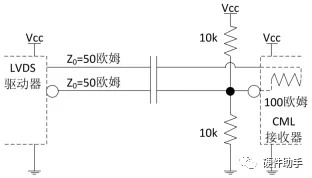

CML一般都内置了匹配电阻。如果CML的输入没有直流偏置,则需要2个10K电阻。

交流耦合

交流耦合

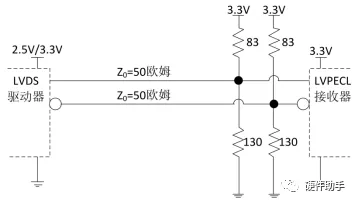

3.2、LVDS到LVPECL的连接

LVDS的输出幅度比较小,如果后端LVPECL的输入能够接受才可以连接,否则要加转换芯片。

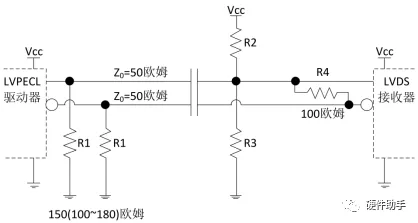

3.2.1、直流匹配

LVDS到LVPECL的直流耦合结构中需要加一个电阻网络,该电阻网络完成直流电平的转换。LVDS输出电平为1.2V,LVPECL的输入电平为Vcc-1.3V。LVDS的输出是以地为基准,而LVPECL的输入是以电源为基准,这要求考虑电阻网络时应注意LVDS的输出电位不应对供电电源敏感;另一个问题是需要在功耗和速度方面折中考虑,如果电阻值取的较小,可以允许电路在更高的速度下工作,但功耗较大,LVDS的输出性能容易受电源的波动影响;还有一个问题就是要考虑电阻网络与传输线的匹配。

直流耦合

直流耦合

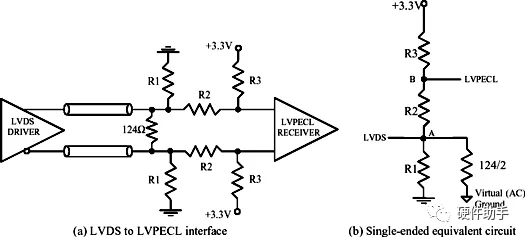

3.2.1、交流匹配

接收端电阻网络中间接入一电容到地,这样可以消除差分线上的共模噪声。

交流耦合

3.3、LVDS到HSTL的连接

CML和HSTL的互连推荐采用交流耦合。

编辑:hfy

-

lvds

+关注

关注

2文章

1244浏览量

70239 -

逻辑电平

+关注

关注

0文章

205浏览量

15150 -

HSTL

+关注

关注

0文章

4浏览量

9920

发布评论请先 登录

探索SY58621L:高性能CML/LVPECL背板收发器的卓越性能

SN65CML100:超高速信号转换与中继的理想选择

LVPECL、CMOS和LVDS 核心区别对比

深入解析SN65EPT23:3.3V ECL差分LVPECL/LVDS到LVTTL/LVCMOS转换器

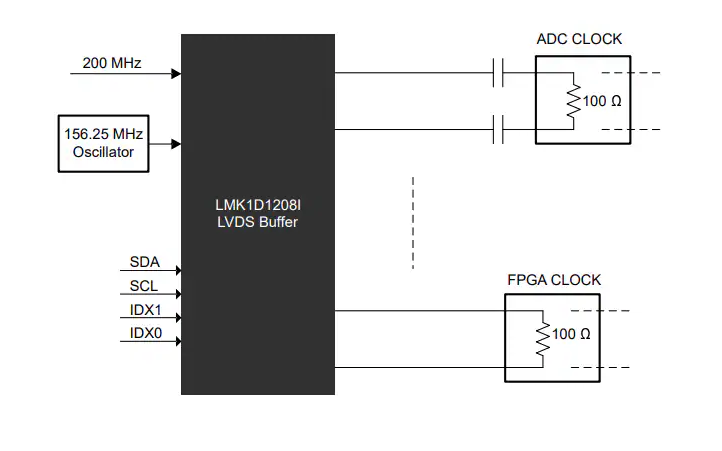

高性能LVDS时钟缓冲器LMK1D1208I技术解析

LMK1D1208P LVDS时钟缓冲器技术解析

CDCM6208V1F 时钟发生器与抖动清除器技术文档总结

CDCM6208V2G 2:8时钟发生器与分数分频器的抖动清除器产品摘要

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析

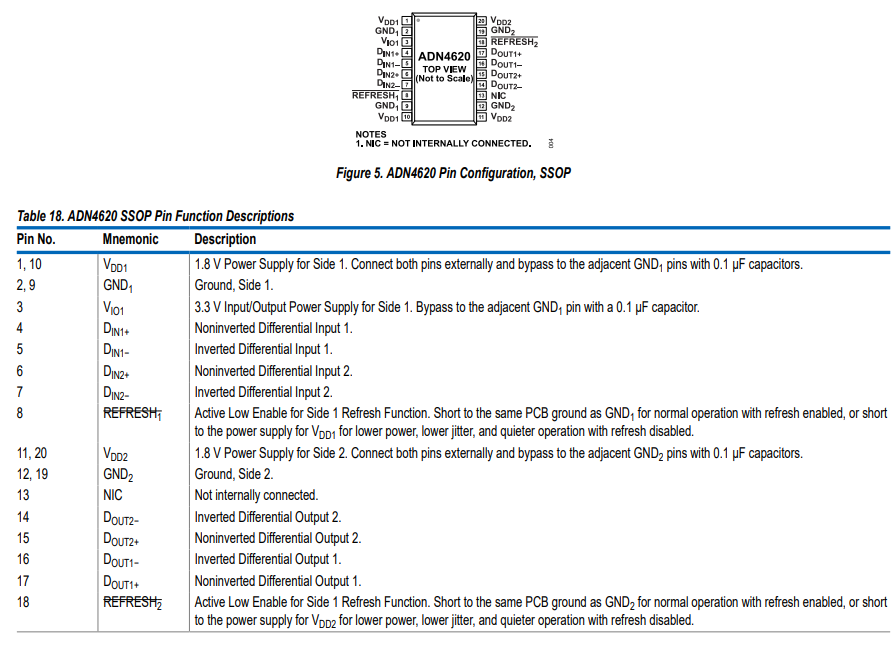

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms双通道LVDS 2.5 Gbps隔离器技术手册

MAX9374/MAX9374A差分LVPECL至LVDS变换器技术手册

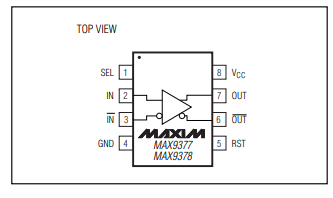

MAX9377/MAX9378任意逻辑至LVPECL/LVDS转换器,引脚可设置四分频电路技术手册

MAX9375单LVDS/任意逻辑至LVPECL转换器技术手册

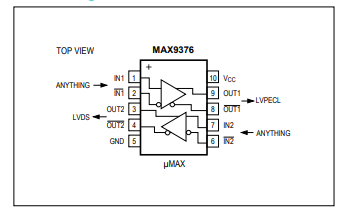

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器技术手册

LVDS、CML、LVPECL不同逻辑电平之间的互连(二)

LVDS、CML、LVPECL不同逻辑电平之间的互连(二)

评论