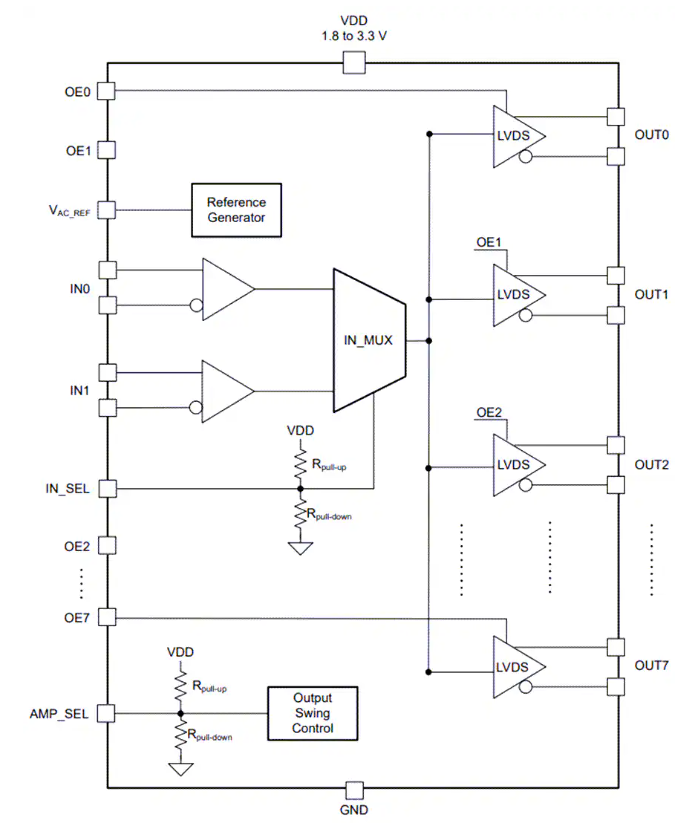

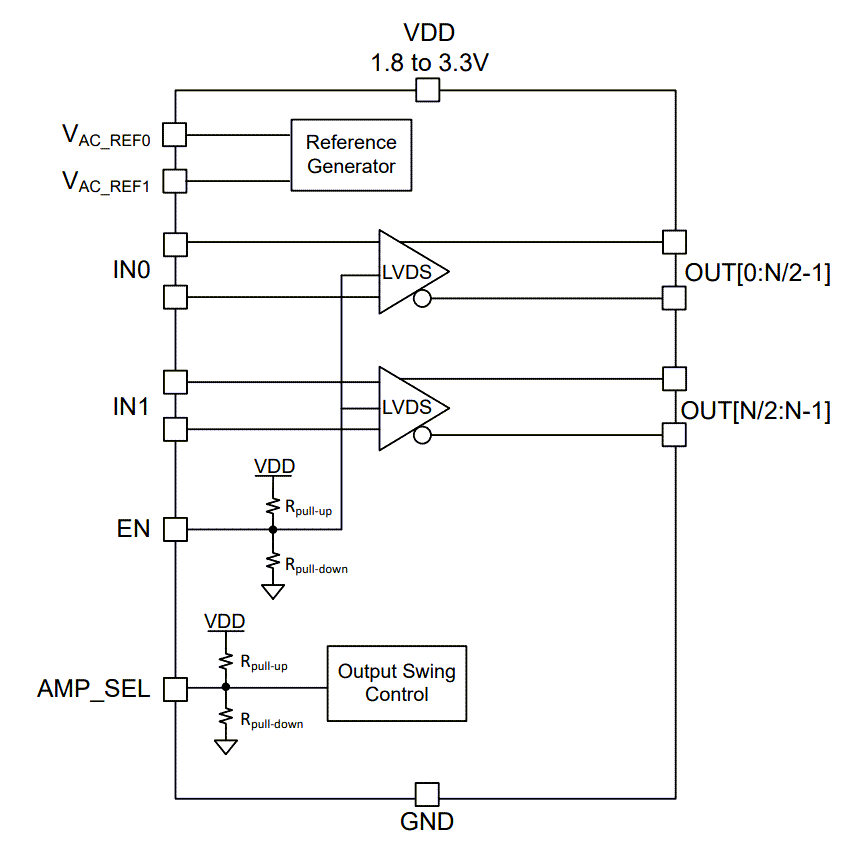

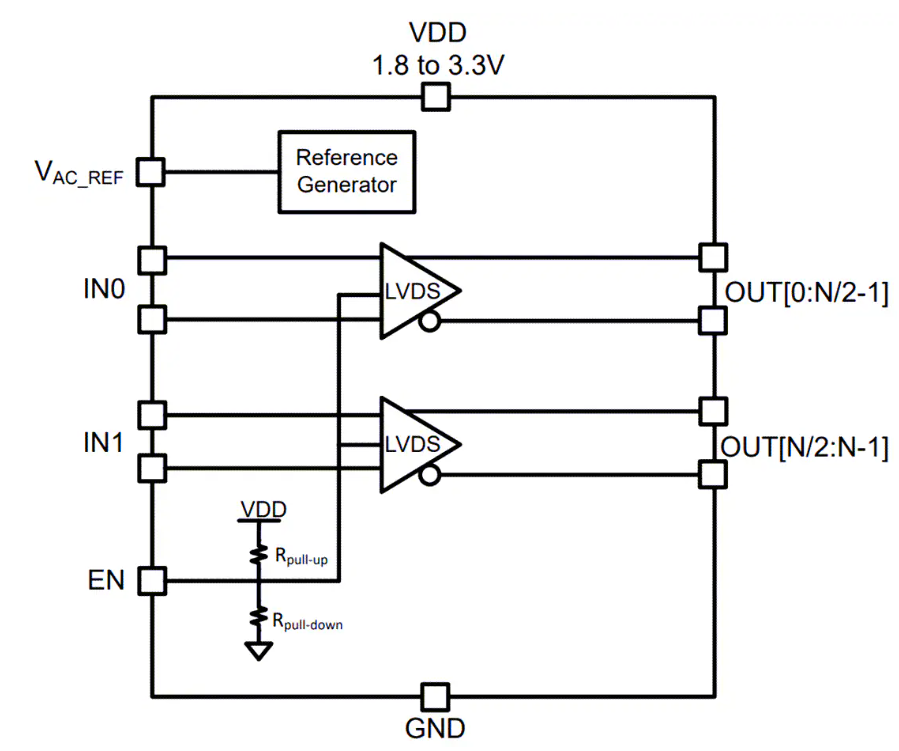

Texas Instruments LMK1D1208P 8通道输出LVDS时钟缓冲器将两个中的一个可选时钟输入(IN0和IN1)分配给八对差分LVDS时钟输出(OUT0至OUT7)。通过超小延迟实现时钟分配。输入可以为LVDS、LVPECL、LVCMOS、HCSL或CML。

数据手册:*附件:Texas Instruments LMK1D1208P 8通道输出LVDS时钟缓冲器数据手册.pdf

Texas Instruments LMK1D1208P专为驱动50Ω传输线路而设计。在单端模式下驱动输入时,对未使用的负输入引脚施加适当的偏置电压。IN_SEL引脚选择输入,输入路由至输出。该器件支持失效防护输入功能。该器件还集成了输入迟滞,可防止在没有输入信号的情况下输出随机振荡。

各个LVDS差分输出均可通过将对应的OEx引脚设置为逻辑高电平“1”来实现。如果此引脚设置为逻辑低电平“0”,输出将被禁用,呈现高阻态,从而降低功耗。该器件可在1.8V、2.5V或3.3V电源环境下工作,额定温度范围是–40°C至105°C(环境温度)。

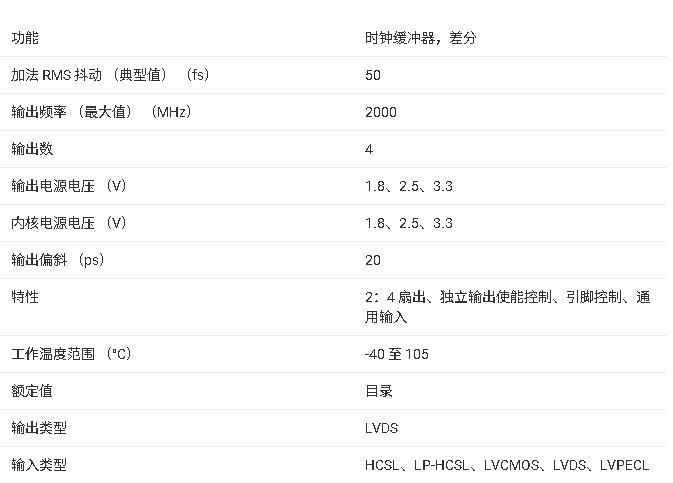

特性

- 具有2路输入和8路输出 (2:8) 的高性能LVDS时钟缓冲器系列

- 输出频率最高可达2GHz

- 通过硬件引脚实现启用/禁用独立输出

- 电源电压:1.8V/2.5V/3.3V ± 5%

- 低附加抖动:156.25MHz下小于12kHz至20MHz范围内的60fs rms最大值

- 超低相位噪底:-164dBc/Hz(典型值)

- 超低传播延迟:<575ps(最大值)

- 输出偏移:20ps(最大值)

- 故障安全输入

- 通用输入接受LVDS、LVPECL、LVCMOS、HCSL和CML

- LVDS基准电压VAC_REF,适用于容性耦合输入

- -40°C 至 105°C 工业温度范围

- 6mm × 6mm 40引脚VQFN封装

功能框图

LMK1D1208P LVDS时钟缓冲器技术解析

一、产品概述

LMK1D1208P是德州仪器(TI)推出的一款高性能8通道LVDS时钟缓冲器,具有以下核心特性:

- 2输入8输出架构:支持从2个输入源中选择1个进行8路分配

- 超低抖动性能:典型值45fs RMS(12kHz-20MHz频段)

- 宽工作电压:1.8V/2.5V/3.3V ±5%供电

- 高频率支持:输出频率最高达2GHz

- 灵活控制:硬件引脚实现独立输出使能/禁用

二、关键参数与性能

2.1 电气特性

| 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 供电电流(静态) | 所有输出使能未端接 | - | 75 | - | mA |

| 供电电流(工作) | 100MHz, 100Ω负载 | - | 87 | 110 | mA |

| 差分输出电压 | 100Ω负载 | 250 | 350 | 450 | mV |

| 传播延迟 | - | - | 0.3 | 0.575 | ns |

| 输出间偏斜 | - | - | - | 20 | ps |

| 随机附加抖动 | 156.25MHz | - | 45 | 60 | fs RMS |

2.2 封装信息

- 封装类型:40引脚VQFN (RHA)

- 封装尺寸:6mm × 6mm

- 热阻参数:

- 结到环境(θJA):30.3°C/W

- 结到外壳(θJC):4.5°C/W

三、功能特性详解

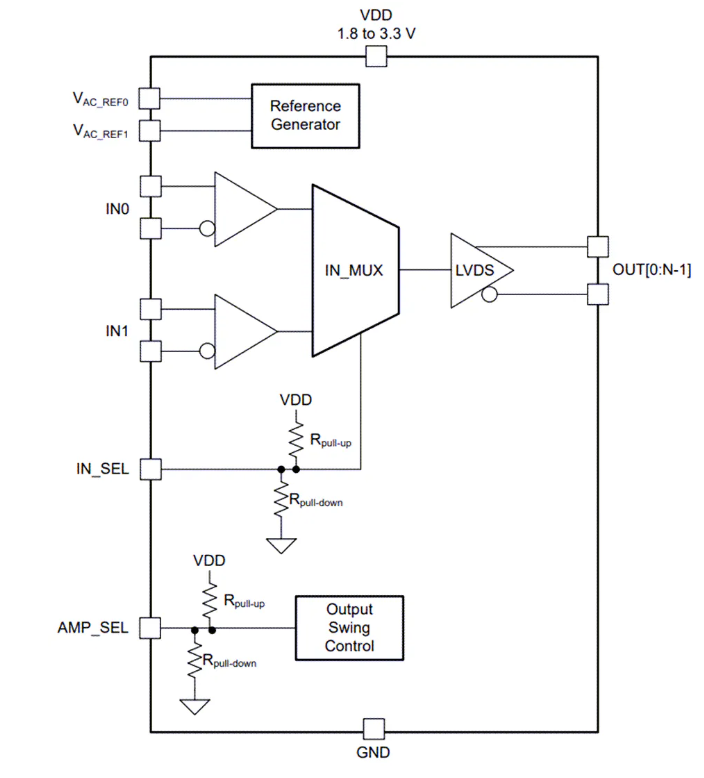

3.1 输入选择与配置

LMK1D1208P提供两路差分输入(IN0和IN1),通过IN_SEL引脚选择:

- IN_SEL=0:选择IN0输入

- IN_SEL=1:选择IN1输入

- IN_SEL悬空:禁用所有输入缓冲器

输入支持多种信号类型:

- LVDS/LVPECL/HCSL/CML差分信号

- LVCMOS单端信号(0.4V至3.465V)

3.2 输出控制

每个LVDS输出通道可独立控制:

- OEx=1(默认):使能输出

- OEx=0:禁用输出(高阻态)

输出幅度可通过AMP_SEL引脚调节:

- AMP_SEL=0:Bank0增强摆幅(500mV),Bank1标准摆幅(350mV)

- AMP_SEL悬空:所有通道标准摆幅(350mV)

- AMP_SEL=1:所有通道增强摆幅(500mV)

四、典型应用设计

4.1 推荐电路设计

- 电源设计:

- 每个VDD引脚需配置0.1μF去耦电容

- 建议增加1μF和10μF大容量电容

- 可选添加磁珠隔离电源噪声

- 输入接口设计:

- LVDS输入:100Ω端接电阻

- LVPECL输入:需75Ω/150Ω电阻网络

- LVCMOS输入:需设置合适偏置电压

- 输出接口设计:

- 推荐100Ω差分端接

- 未使用输出应禁用(OEx=0)

4.2 PCB布局要点

- 热设计:

- 裸露焊盘(DAP)必须焊接至PCB地平面

- 建议使用多个过孔连接至内部地层

- 信号完整性:

- 保持差分对长度匹配

- 避免直角走线

- 关键信号远离噪声源

五、应用场景

-

时钟缓冲器

+关注

关注

2文章

221浏览量

51786 -

lvds

+关注

关注

2文章

1216浏览量

69116 -

时钟输入

+关注

关注

0文章

7浏览量

2084

发布评论请先 登录

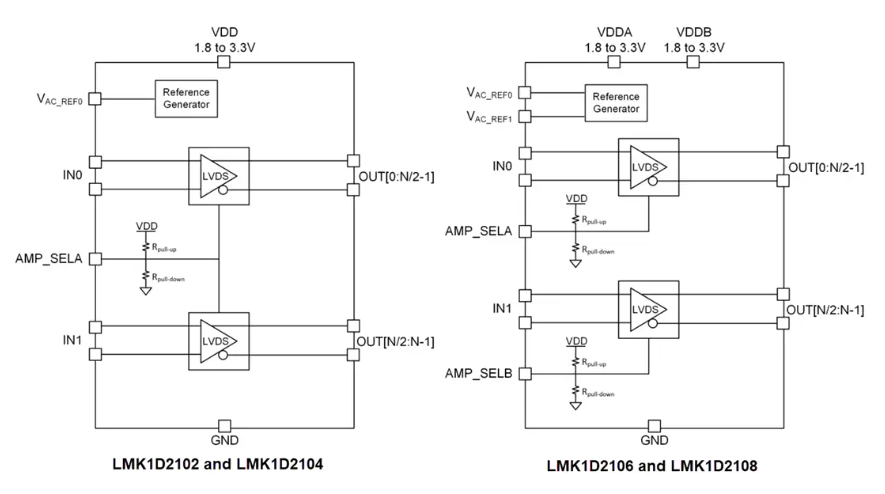

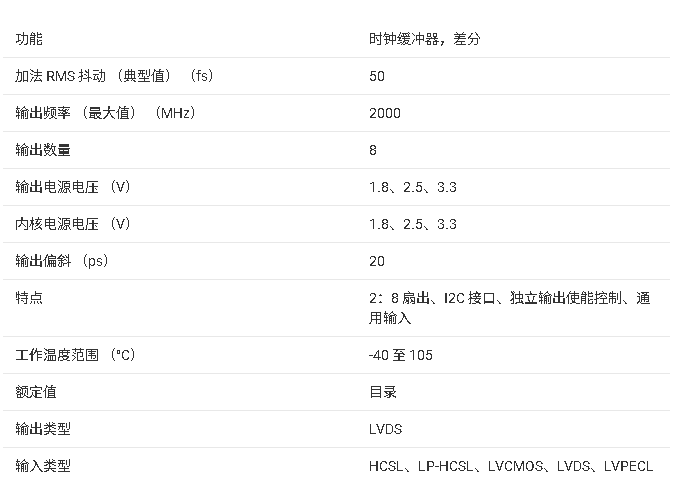

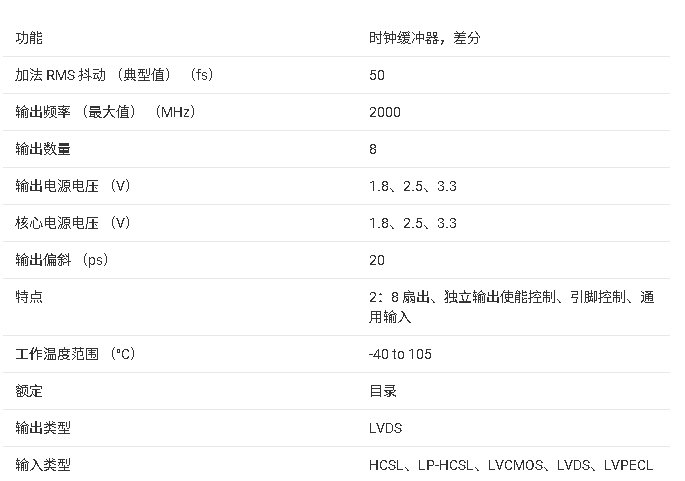

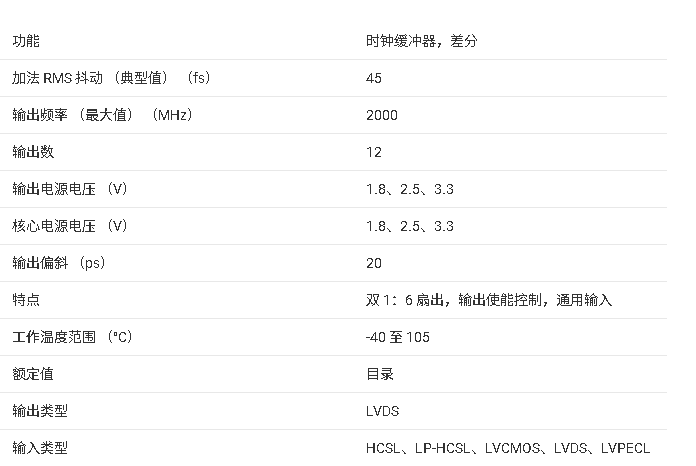

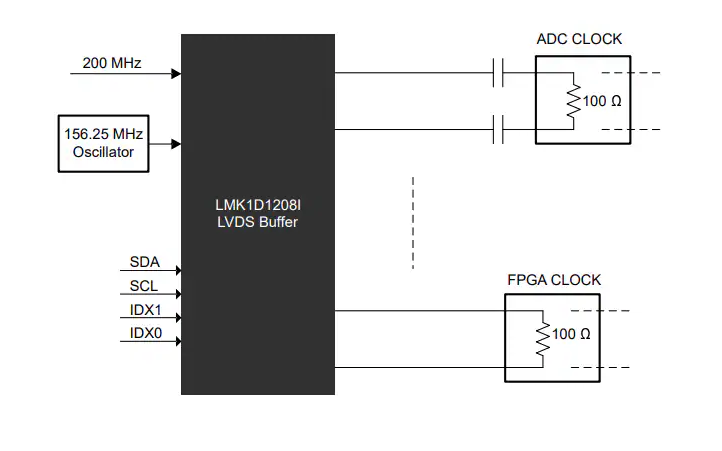

LMK1D1208I I2C可配置低附加抖动LVDS缓冲器数据表

LMK1D1204P引脚控制型OE低附加抖动LVDS缓冲器数据表

LMK1D1208P引脚控制型OE低附加抖动LVDS缓冲器数据表

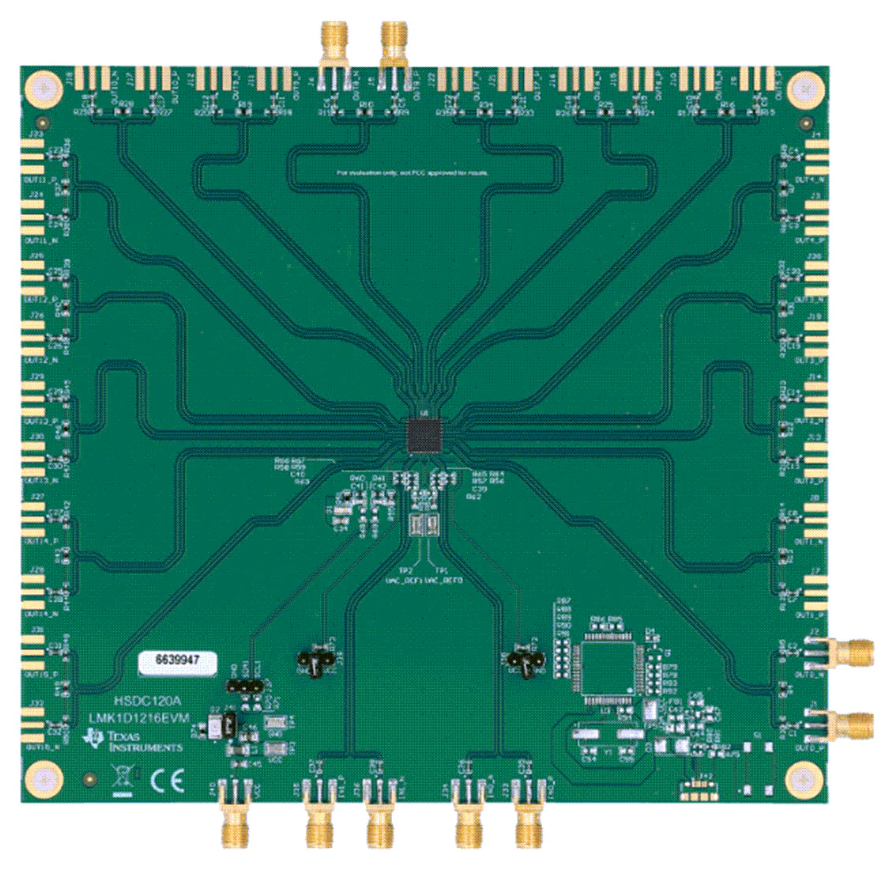

LMK1D1208低附加抖动、八路LVDS输出时钟缓冲器评估板

Texas Instruments LMK1D210xL低附加LVDS缓冲器数据手册

LMK1D121x低附加抖动LVDS时钟缓冲器技术解析与应用指南

LMK1D1216EVM缓冲器评估模块技术解析与应用指南

LMK1D2106/LMK1D2108 LVDS时钟缓冲器技术解析与应用指南

LMK1D1208P LVDS时钟缓冲器技术解析

LMK1D1208P LVDS时钟缓冲器技术解析

评论