本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

下面详细介绍第一部分:同种逻辑电平之间的互连。

| 输入 | ||||

| CML | PECL | LVDS | ||

| 输出 | CML | √ | √直流、交流耦合 | √直流、交流耦合 |

| PECL | √直流、交流耦合 | √直流、交流耦合 | √直流、交流耦合 | |

| LVDS | √直流、交流耦合 | √直流、交流耦合 | √ | |

1、LVDS到LVDS的连接

1.1、直流匹配

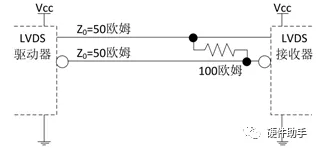

LVDS直接是可以直接连接的,不论是2.5V还是3.3V,无非是否在外部再放一个100欧姆匹配电阻。端接电阻要靠近接收端输入引脚!!!

内置100Ω端接电阻的连接方式

外接100Ω端接电阻的连接方式

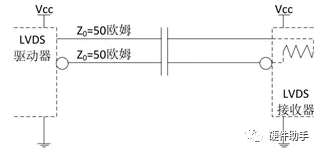

1.2、交流匹配

如果接收器输入端内置直流偏置,交流匹配也就是带不带100欧姆匹配的问题。

内置100Ω端接电阻的连接方式

外接100Ω端接电阻的连接方式

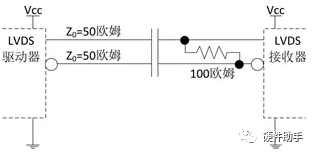

如果芯片没有内置直流偏置电压,就需要外接电阻到参考电压(1.2V)。为了支持传输线上的长0和长1数据序列,耦合电容的值不能太小,一般取0.1uF。C1、C2尽量靠近接收端放置,但不用像端接电阻那样紧贴输入管脚。

2、CML到CML的连接

CML到CML之间连接分两种情况,当收发两端的器件使用相同的电源时,CML到CML可以采用直流耦合方式,这时不需加任何器件;当收发两端器件采用不同电源时,一般要考虑交流耦合,注意这时选用的耦合电容要足够大,以避免在较长连0或连1情况出现时,接收端差分电压变小。

2.1、直流匹配

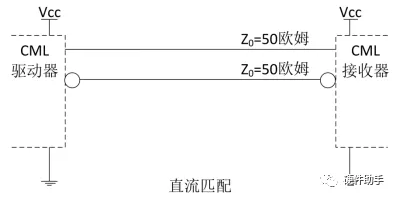

如果接收器的输入有内置匹配,如果接收器与发送器之间采用相同的VCC电源,CML驱动器输出可以直流耦合到CML接收器输入,无需额外的元件,可以直连。

直流匹配——直连

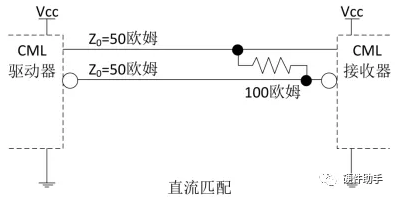

如果接收器的输入没有内置匹配,则需要在终端并接100欧姆匹配电阻。

直流匹配——100欧姆匹配

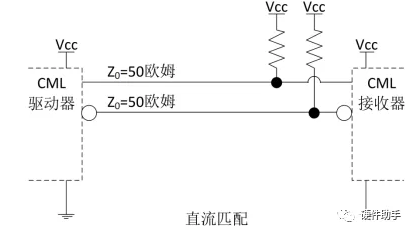

如果接收器的输入没有内置匹配,也可以通过在终端上拉50欧姆匹配电阻进行互连。

直流匹配——50欧姆上拉匹配

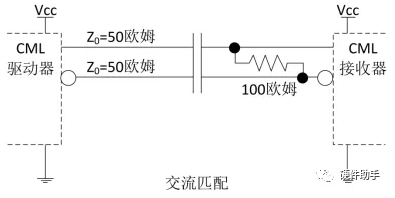

2.2、交流匹配

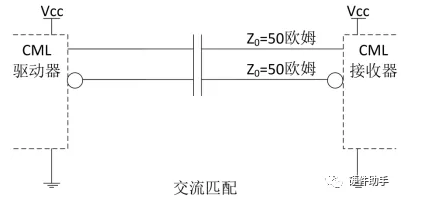

如果接收器与发送器采用不同的电源,系统需要用交流耦合方式。交流耦合情况下,耦合电容应足够大,以避免信号包含一长串相同数字时导致过大的低频衰减。

交流匹配——直连

如果接收器的输入没有内置匹配,则需要在终端并接100欧姆匹配电阻。

交流匹配——100欧姆匹配

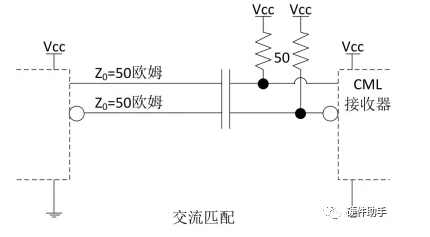

如果接收器的输入没有内置匹配,也可以通过在终端上拉50欧姆匹配电阻。

交流匹配——50欧姆上拉匹配

3、LVPECL到LVPECL的连接

3.1、直流匹配

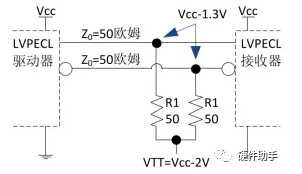

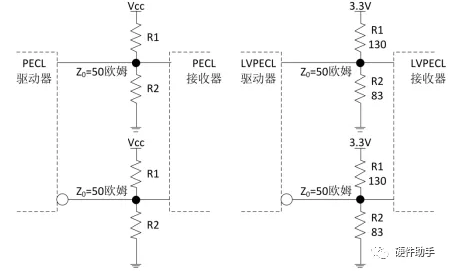

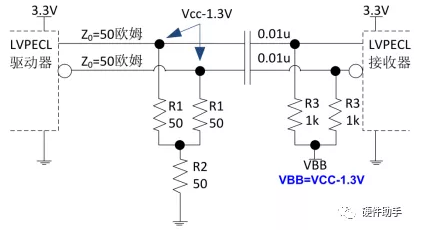

3.1.1、50欧姆匹配到参考电压

最简单的LVPECL匹配方式就是在接收器的输入侧需要一个参考电压,参考电压要比Vcc低2.0V,额外的电源需求会增加电路的复杂度和成本。Vcc-2.0V的偏置电压是考虑到ECL的14mA在50欧姆上的0.7V压降,在总线上的中间电平依然是Vcc-1.3V。

3.1.2、三电阻匹配

一种减少附加成本的方式就是增加一个电阻,两个50欧姆电阻提供信号匹配,另一个电阻连接到地给这两个电阻提供直流偏置到VTT。

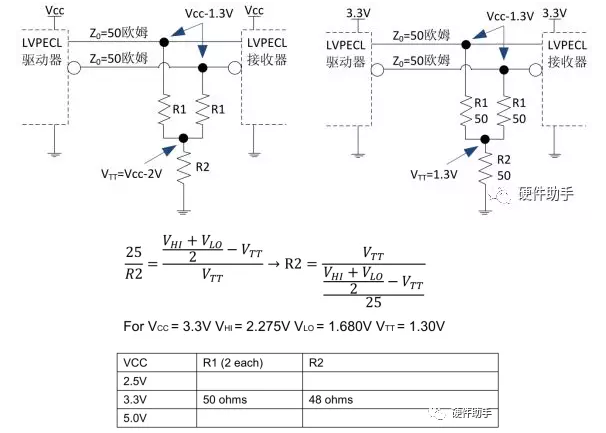

3.1.3、四电阻匹配

这是使用最多的LVPECL匹配方式,采用四电阻戴维南匹配。

四个电阻匹配的计算步骤如下:

a、从阻抗匹配要求可以得出:

R1||R2=50

b、电阻比等于电压比可以得出:

(R1+R2)/R2=VCC/(VCC-2)

Vcc-2.0V的偏置电压是考虑到ECL的14mA在等效50欧姆上的0.7V压降,在总线上的偏置电压依然是Vcc-1.3V。

于是可以得到:

R1=50*Vcc/(Vcc-2)

R2=25*Vcc

4个电阻都必须放在离输入端很近的地方,对PCB布板造成困难。匹配电阻功耗比较大,如果路数很多的话,对单板的功耗来说是一个比较大的问题(静态电阻很小)。所以,在实际的布板过程中,一般不提倡使用这种电路。

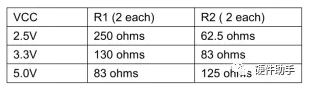

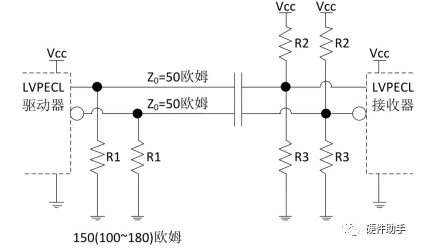

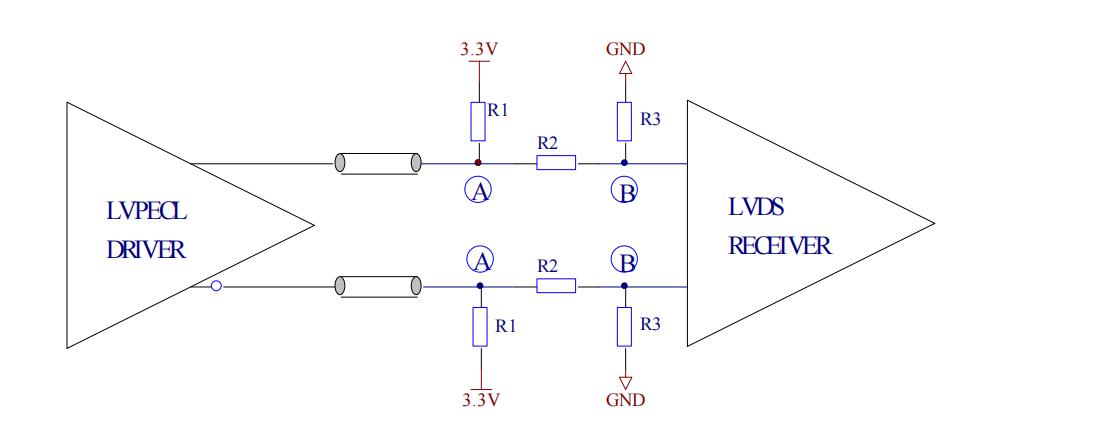

3.1.4、下拉+100欧姆跨接

这是最常用,最简洁的直流匹配方式,特别适合同电压PECL之间的对接。

R1=140~200欧姆(3.3V),R1=270~330欧姆(5V),R2=100欧姆。

R1为输出门提供偏置电流,R2为交流信号提供匹配。输入门的直流电平偏置直接利用输出门的直流电平(Vcc-1.3V),并不需要外来的上下拉电阻来提供。

此匹配电路电阻个数很少,只有3个。只有R2一个电阻必须放在离输入门比较近的地方,R1放置的地方可以比较随便,只要不引入过长的线头(过长的线头会导致反射)就可以了。PCB布板比较容易处理。这种电路是一个优选电路。

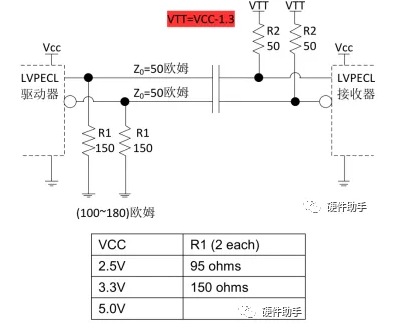

3.1.5、下拉+50欧姆匹配到参考电压

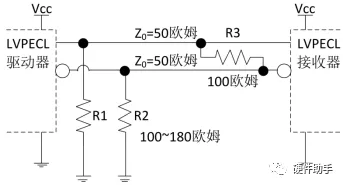

3.2、交流匹配

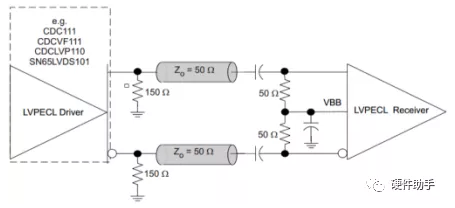

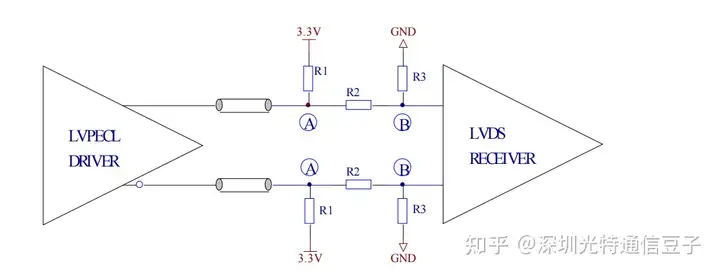

PECL在交流耦合输出到50Ω的终端负载时,要考虑PECL的输出端加一直流偏置电阻。PECL的输出共模电压需固定在Vcc-1.3V,在选择直流偏置电阻时仅需该电阻能够提供14mA到地的通路,这样R1=(Vcc-1.3V)/14mA。在3.3V供电时,R1=142Ω,5V供电时,R1=270Ω。然而这种方式给出的交流负载阻抗低于50Ω,在实际应用中,3.3V供电时,R1可以从142Ω到200Ω之间选取,5V供电时,R1可以从270Ω到350Ω之间选取,原则是让输出波形达到最佳。

R3和R2的选择应考虑如下几点:

PECL输入直流偏压应固定在Vcc-1.3V;

输入阻抗应等于传输线阻抗;

低功耗;

外围器件少。

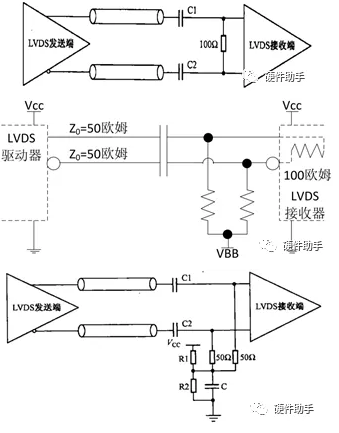

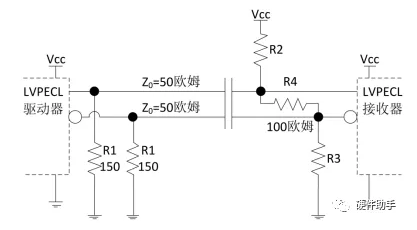

3.2.1、三电阻匹配

3.2.2、两电阻+100欧姆跨接

这是最常用,最简洁的交流匹配方式,也常用于PECL/LVPECL/2.5VPECL之间的对接,推荐使用。

R1=140~200欧姆,属于直流偏置电阻。

C1为耦合电容,可以放在线上的任何一个地方,不一定在源端,也不一定要在末端。

R4=100欧姆,属于交流匹配电阻,一定要放在末端。

R2、R3为K级别的电阻,必须满足R3/(R2+R3)=(VCC-1.3V)/VCC的比值就可以了,这两个电阻是为输入端提供直流电平,所以对PCB上的位置没有特殊要求,只需要不引入长线头就可以了。

对于交流耦合来说,阻容器件的个数算是比较少的了;只对一个电阻的位置(R4)有要求,其他的没有要求;功耗也比较小。这种电路还带来另外一个优点,那就是当LVPECL输出没有交流信号的时候,那么输入端却可以依靠100欧姆的电阻,使得P/N维持一个电压差,从而保证输入端的稳定。

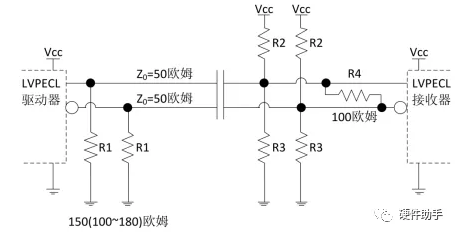

3.2.3、四电阻匹配

3.2.4、五电阻匹配

此处有了100欧姆电阻,R2和R3只是提供直流偏置而已,阻值需要选大一些,从而保证R2||R3||(R4/2)基本上还是50欧姆。

3.3V情况下可以选择R2=2.2K,R3=3.3K,参考电压为大约为2V(Vcc-1.3V)。

两个50Ω电阻中点接入一电容,是为了消除差分线上信号偏移而产生的共模噪声(2个50Ω是差模阻抗匹配,VBB电容是共模滤波电容)。

以上是针对两个同种类型逻辑电平之间的互连。

编辑:hfy

-

lvds

+关注

关注

2文章

1244浏览量

70233 -

逻辑电平

+关注

关注

0文章

205浏览量

15150 -

LVPECL

+关注

关注

2文章

77浏览量

18900 -

CML

+关注

关注

0文章

35浏览量

20627 -

欧姆电阻

+关注

关注

0文章

71浏览量

15996

发布评论请先 登录

SN65CML100:超高速信号转换与中继的理想选择

深入解析SN65EPT23:3.3V ECL差分LVPECL/LVDS到LVTTL/LVCMOS转换器

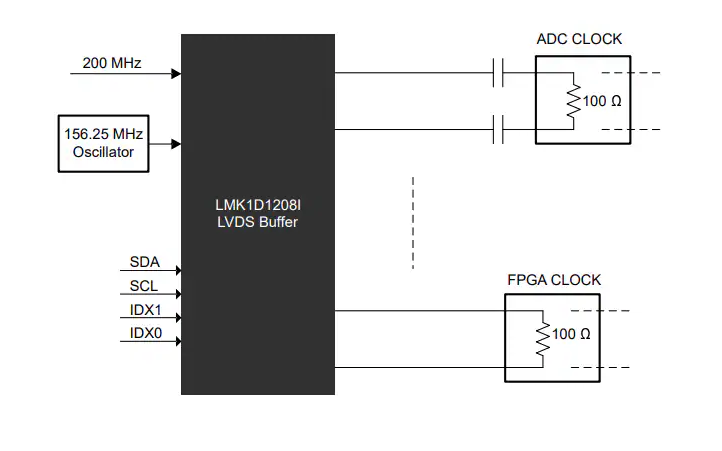

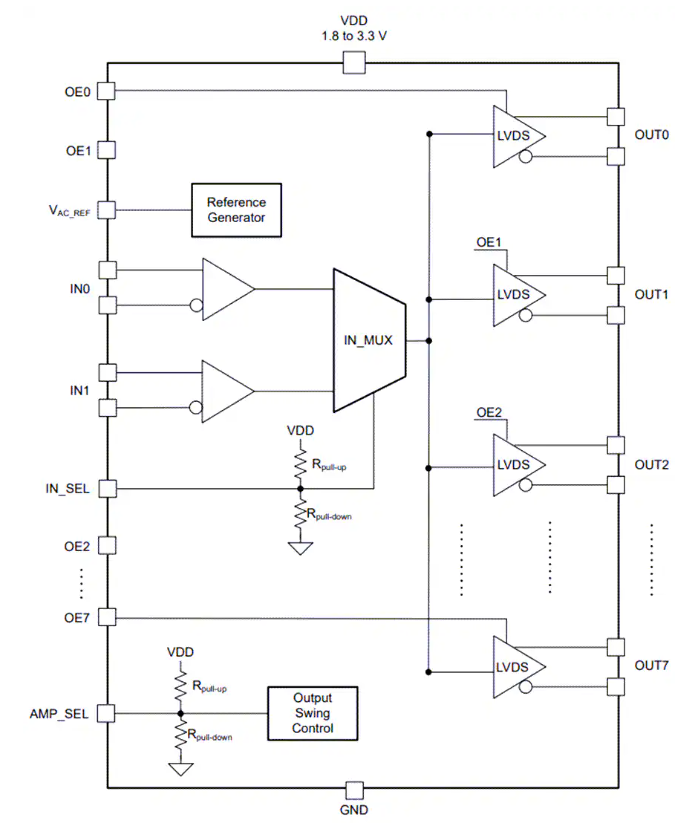

高性能LVDS时钟缓冲器LMK1D1208I技术解析

LMK1D1208P LVDS时钟缓冲器技术解析

【电子元件】FCO-3L差分输出晶体振荡器:3.2×2.5mm封装的高频低抖动特性及应用

从SerDes到SoC,全场景适配的FCom差分晶振设计全解

从SerDes到SoC,全场景适配的FCom差分晶振设计全解

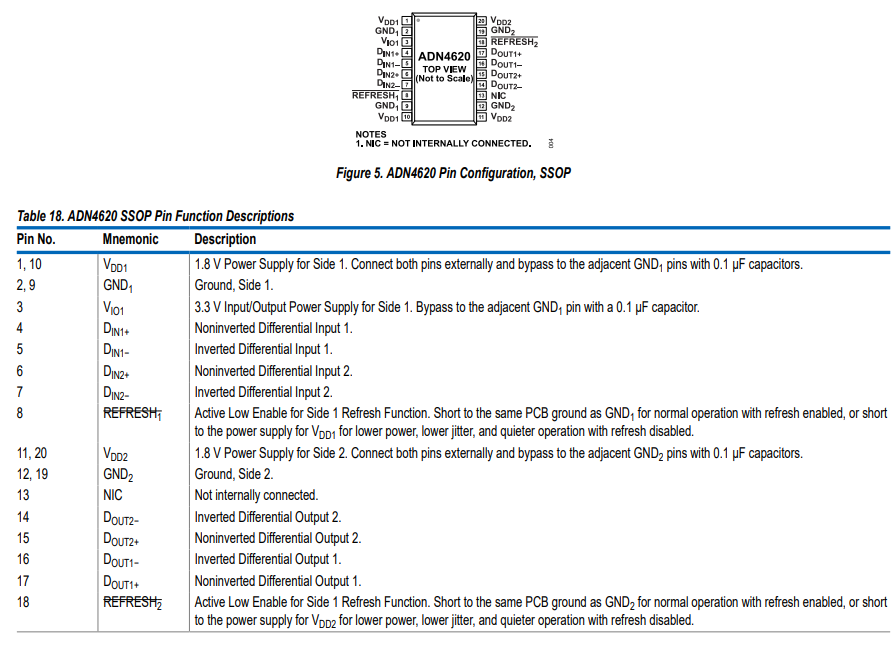

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms双通道LVDS 2.5 Gbps隔离器技术手册

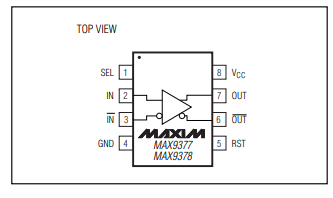

MAX9374/MAX9374A差分LVPECL至LVDS变换器技术手册

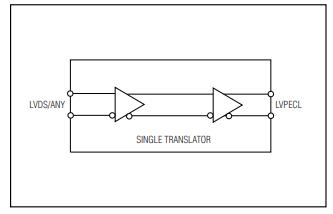

MAX9375单LVDS/任意逻辑至LVPECL转换器技术手册

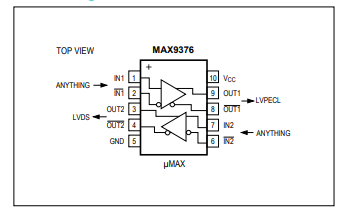

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器技术手册

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连

评论