资源利用率、逻辑层次和时序约束。 2时序基线设定:在每个实现步骤后检查并解决时序违例,从而帮助布线后收敛时序。 3时序违例解决:识别建立时间违例或保持时间违例的根源,并解决时序违例。 01 初始设计检查详细介绍 在赛灵思器件上实现设计,是一个自动化程度相当

2021-11-05 15:10:26 4603

4603

大家好,我正在使用Virtex 5,并试图实现我的设计的时序收敛。速度等级为-2,为150Mhz。从.srp报告中,我的设计的最大频率非常接近。但是,我想我必须在那里保留一些余量以防止P&amp

2019-04-11 12:13:44

的负载和金属线网的延迟l增加Tskewn在时钟路径上,插入buffer,增加时钟路径的延迟,但是不能影响hold timing。 Holdtime violation:保持时间在静态时序分析时必须满足

2018-11-26 14:39:04

:FTM0_Ch0_Ch1_IrqHandler 第 287 行: 如果 (chan0IntFlag && g_ftmChannelRunning[0][0]) { TIMING_Ftm_IrqHandler(0U, 0U

2023-03-29 08:20:52

见 AD5700 DatsSheet Page9,Carrier Detect Off Timing:请问图中红圈标记的RXD波形是如何来的呢?在示波器上也观察到了此现象,这个波形对于UART

2018-12-14 09:22:48

知道“时间分析器”和“planahead”可以帮助我,但我无法理解它的报告。我该怎么做才能解决时间问题。我找不到一些材料来帮助我理解“时序分析”,“代码风格”,“如何纠正时间问题” ','时序收敛'等等

2019-03-18 13:37:27

ISE Timing Anlayzer report 是看post-map 还是 post-place&route我现在有个工程 post-map 有错post-place&route 通过这该以哪个为准

2017-08-24 14:15:26

本帖最后由 beHancock 于 2020-3-8 16:14 编辑

如题。补充几个图//-----------------------------------------这个目录上Static Timing的图标都和其它的不一样了。。。

2020-03-07 22:43:51

最近用到sopc,设计片外ram,故整理“SOPC中SDRAM controller 的Timing配置”一文以备忘。Timing选项:CAS latency cycles(CAS等待时间):即为

2012-03-01 10:20:50

在使用库函数(3.5版本),将通用定时器选用TIM_OCMode_Timing模式,同时使能4个通道中断,可是进不了定时器的中断函数。当选择TIM_OCMode_Toggle模式时,就能进入到中断

2019-09-19 17:42:20

Setup/Hold Time ProblemConclusionIf the Setup/Hold time error happen on the Input Register (Example

2008-09-11 09:23:30

fpga_timing技术文档 xilinx官方

2016-08-17 09:02:16

niScope Configure Horizontal Timing 的说明中,参数number of records,根据我的测试,应该是设置获取信号的通道数。但min record

2018-01-09 15:44:28

: Timing requirements not met这个错误,之前那些正常的工程全都报这个错误,别人电脑里的工程我软件打开还是报错,我的给别人编译又能通过,然后我quartus已经卸载重装好多次了,版本也从10.0 到11.0,然而还是没有什么卵有,请问有大神知道这个应该怎么搞么?难道重装系统?!

2016-01-15 10:51:47

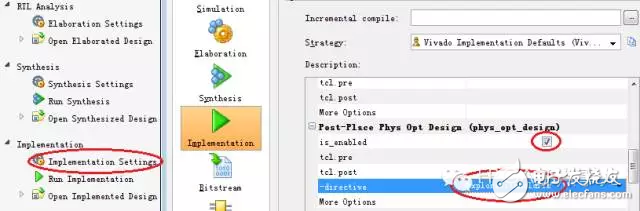

窗口里面可以查看相关的时序违例信息,这里只显示了10个,可以在report timing summary中选择要查看的个数,比如选择100个五:我们可以打开setting ->synthesis

2018-08-22 11:45:54

to!! ---------------+---------+---------+---------+---------+ Timing summary: --------------- Timing errors: 0Score: 0(Setup/Max: 0, Hold: 0) Constraints

2019-02-26 10:15:03

Until now, verifying that timing in 33 MHz 64-bit PCI designs met the setup and hold specification

2019-04-28 06:35:34

如果出现了时序违例,我们会关注两点: 为什么会出现时序违例? 如何解决? 首先我们要搞清楚时序是在哪个阶段违例: 在综合阶段或者post opt阶段出现了时序违例,那么很有可能的原因如下

2021-01-08 17:10:25

如图所示,在TC397的ASCLIN SPI Master Timing表格中,控制器所需要的最小setup time大于最小clock period,这是不满足时序要求的,请问datasheet是否有误?

2024-01-29 08:00:24

嗨,如何消除负面松弛?如果我把时间忽略约束放到松弛路径上,它会破坏逻辑吗?谢谢你以上来自于谷歌翻译以下为原文Hi, How to remove negative slack?. If i put

2019-03-29 12:48:58

the concepts of timing analysis such as setup hold time, skew , transport delay, other timing violation etc.

2019-02-14 08:16:03

). I mean, how to measure the setup or hold time of input signal in FPGA andcompare with the values given from static timing report. FPGA freak

2019-01-15 11:07:15

FPGA开发板,工程编译后,Timequest timing analyzer 显示红色,是否是错误,需要改正?编译结果中,messages框中,并没有错误,只是有一些警告,这样看来,是不是那个timequest并不需要改正,也不会影响工程烧录和运行?(见下图)求指点

2019-04-22 15:37:41

您好,如果我想为我的设计获得最佳时序收敛,我应该使用什么实施策略?例如,如果我想改善设置和保持的松弛度,我应该选择哪种最佳策略?以上来自于谷歌翻译以下为原文Hello,If i want

2018-11-05 11:40:14

喜我在Windows XP上安装了xilinx ISE 10.1。我在地图中遇到了一些时间问题,所以我在ISE的tcl窗口中将xil_timing_allow_impossible设置为1。地图经历

2019-03-05 07:48:54

玩转Vivado之Timing Constraints特权同学,版权所有最近在熟悉Xilinx已经推出好几年的Vivado,虽然特权同学之前已经着手玩过这个新开发工具,但只是简单的玩玩,没有深入

2016-01-11 16:55:48

刚开始学vhdl,想写一个波形发生器的代码,但过程中编译老是出现Critical Warning (332148): Timing requirements not met的警告,想用

2016-12-10 15:43:14

在AD80370的datasheet里面有SYSREF± Setup and Hold Timing 这个时序图,但是为什么图中标示的holdup time是负值,如果这样的话那device

2018-10-09 16:09:24

MIPI CS2 input timing和CX3 mipi interface configuration 的关系是什么?

CX3 mipi interface configuration中的值设置成什么是合理的?

2024-02-29 07:25:02

在quartus的仿真里面有两种选项,functional simulation和timing simulation,请问他们的区别是什么?

2019-07-29 05:52:59

Timing Summary is from "Phase 6.1 Hold Fix Iter", but there is no hold violation

2018-11-01 16:13:49

Monitor Timing Standard

VESA and Industry Standards and Guidelinesfor Computer Display Monitor

2008-08-08 13:21:30 507

507 timing and jitter measurements have become crucial

in the design, verification, characterization, and application of electron

2009-07-21 10:21:09 0

0 Without Timing Constraints• This design had no timingconstraints or pin assignments– Note

2010-01-11 08:54:44 6

6 Timing Groups and OFFSET Constraints:

•Use the Constraints Editor to create groups of path

2010-01-11 08:55:47 4

4 Achieving Timing Closure:Timing Reports• Timing reports enable you to determine how and why

2010-01-11 08:56:19 0

0 Path-Specific Timing Constraints:Constraining Between Risingand Falling Clock Edges•

2010-01-11 08:56:50 10

10 IntroductionUntil now, verifying that timing in 33 MHz 64-bit PCI designs met thesetup and hold

2010-07-13 09:39:34 4

4 Implement Master-Slave Timing-Card Redundancy Using Maxim Timing ICs

Abstract

2009-04-07 23:43:36 666

666

Timing Con

2009-04-24 09:12:31 740

740

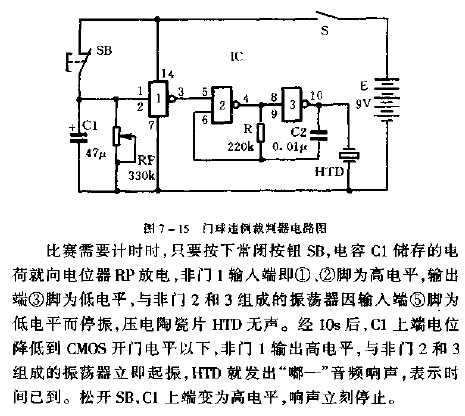

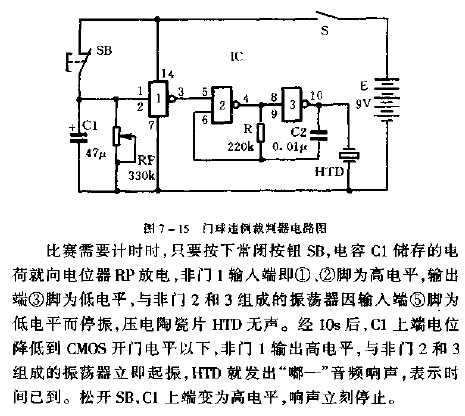

门球违例裁判器电路图

2009-07-29 09:53:35 494

494

The DS31415 is a flexible, high-performance timing IC for diverse frequency conversion

2011-08-01 16:27:04 25

25 本内容介绍了逻辑分析仪中Timing-State存储方式的应用

2011-09-22 14:26:50 14

14 TimeQuest_Timing_Analyzer快速入门教程

2015-12-14 14:21:13 22

22 Timing,PCB学习好资料,欢迎下载学习。

2016-03-23 10:06:24 0

0 随着FPGA规模越来越大,设计本身的复杂度也同样增加。Xilinx UFDM中也经常提到了Design Complexity这样一个概念。Timing/Complexity/congestion

2017-02-08 05:46:09 3042

3042

Perfect Timing II Book

2017-10-27 09:23:52 6

6 时序分析基本概念介绍——Timing Arc

2018-01-02 09:29:04 23487

23487

来维持吗? 1、Vivado基本操作流程 2、时序基本概念 3、时序基本约束和流程 4、Baselining时序约束 5、CDC时序约束 6、I/O时序 7、例外时序约束 8、时序收敛优化技术

2018-08-06 15:08:02 400

400 上述四个数值,无论是在timing report(通过report_timing_summary生成)还是design analysis report(通过report_design_analysis生成)中都有所体现。以timingreport为例,如下图所示,可清晰地显示上述四个数值。

2018-10-19 10:32:39 5175

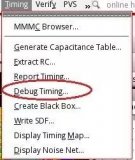

5175 然后会出现如下窗口, 使用GTD前, 需要有一个machine readable格式的timing report文件, 该文件可以通过report_timing -machine_readable

2020-05-19 16:14:47 7022

7022

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Setup、Hold和Pulse Width的总体信息,但凡WNS、WHS或WPWS有一个小于0,就说明时序未收敛。

2020-08-31 13:49:10 5370

5370

生成时序报告后,如何阅读时序报告并从时序报告中发现导致时序违例的潜在问题是关键。 首先要看Design Timing Summary在这个Summary里,呈现了Setup、Hold和Pulse Width的总体信息,但凡WNS、WHS或WPWS有一个小于0,就说明时序未收敛。

2020-08-31 13:52:36 3098

3098

- 低脉冲宽度违例 - 高脉冲宽度违例 如需了解脉冲宽度违例的详情,请参阅报告时序汇总(Report Timing Summary) 的TPWS部分。 最严重的脉冲宽度违例在报告中显示为 WPWS。 如需了解

2020-11-19 13:48:45 4673

4673

AD9928:双通道、14位CCD信号处理器,内置垂直驱动器和Precision Timing发生器

2021-03-19 01:16:56 7

7 AD9923A: CCD 信号处理器,内置垂直驱动器和Precision Timing发生器 数据手册

2021-03-19 06:53:40 0

0 如果你参加过IC校招面试,自然会被问到“setup/hold的概念,以及setup/hold违例怎么办?”

2021-04-27 14:15:54 3875

3875

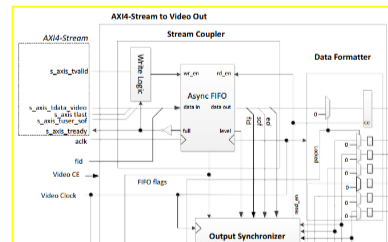

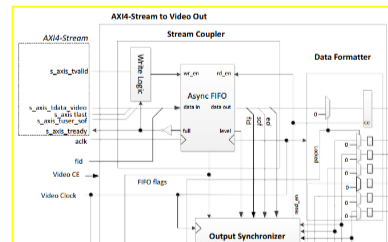

本文对Video out IP和Video Timing Controller IP进行简要介绍,为后文完成使用带有HDMI接口的显示器构建图像视频显示的测试工程做准备。

2021-05-08 10:03:16 5452

5452

VIVADO中时序报告中WNS,WHS,TNS,THS含义运行“report_timing”或“report_timing_summary”命令后,会注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

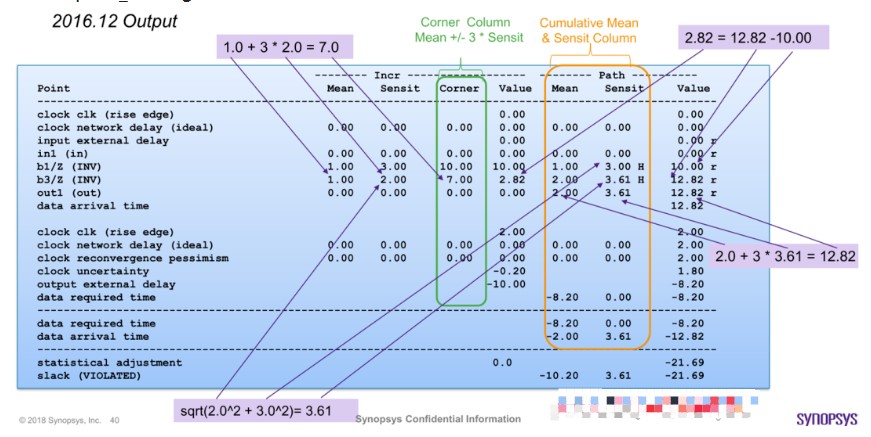

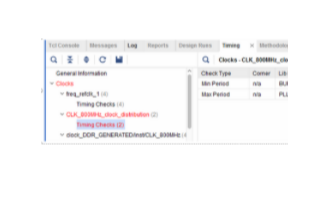

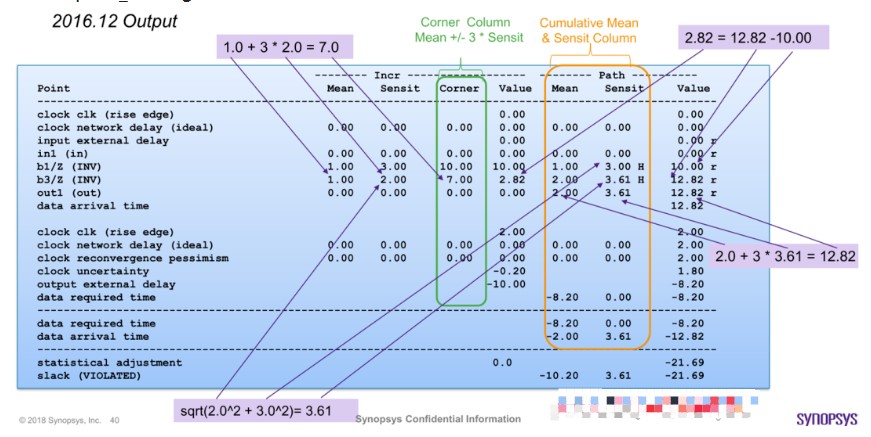

Corner: 高斯分布3个(具体几个是可以设置的)Sigma边界的最差值,比如Setup的话就是Mean+3*Sensit,如果是Hold的话就是Mean-3*Sensit。

2022-10-12 17:37:41 2295

2295

Path1容易出现hold问题,path2容易出现setup问题;如果在path1和path2的commen part修timing就会导致另外一个path的恶化;所以应该分别在path1的非commen part修hold,在path2的非commen part修setup。

2022-10-18 09:36:22 2679

2679 在Place Design之后再去看Hold Time,如果此时Hold Time的违例比较小(比如-0.05ns),还是不需要理会的

2023-01-11 09:05:41 2397

2397 就是SRAM MBIST_CLK延时下来刚好和SRAM测试地址TADDR的跳变完全对齐了,造成了SRAM的memory model的建立/保持时间违例,SRAM model在timing违例情况下Q端输出为X态。下文具体内容请移步知识星球查看。

2023-02-08 16:09:02 1994

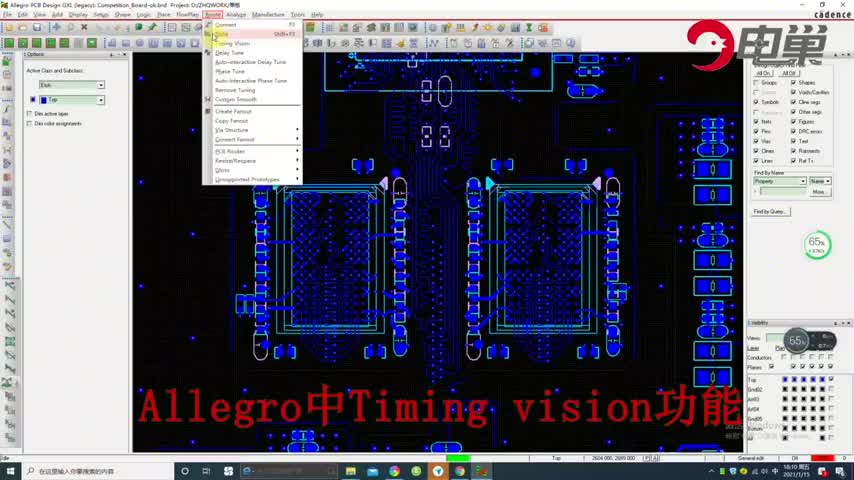

1994 包括shape 和re-shape 、 cell density map 、pin density map 、timing map 、timing chart 、highlight timing

2023-02-12 11:13:49 10107

10107 SDF后仿中往往生成的log中会有一些违例信息,Timing violation路径或者$setuphold违例,这些信息混杂在后仿log中。

2023-03-07 14:55:20 567

567 Timing Commander 硬件 Interfaces 用户指南

2023-03-15 19:24:19 1

1 9FGV1005 PhiClock PCIe Timing Commander 软件 用户指南

2023-03-21 19:28:49 2

2 9FGV1006 Timing Commander 用户指南

2023-03-21 19:29:17 1

1 9FGV100x Timing Commander 用户指南

2023-03-21 19:29:27 0

0 Timing Commander 软件 for VersaClock 3S - 5P3502x

2023-03-23 19:42:47 1

1 VersaClock 6 Timing Commander 用户指南

2023-03-29 19:02:31 1

1 默认report_timing中会出现换行的情况,如下图所示,如何避免换行呢?

2023-04-15 10:20:33 2089

2089 今天这期小编将继续与大家一起学习DFT的相关知识和流程代码,在开始之前,先解决一下上期DFT学习的章节最后留下的问题—DFT工程师在收敛时序timing的时候经常遇到的hold的问题,即不同时钟域的两个SDFF(扫描单元的SI端hold违例问题。

2023-04-16 11:34:59 4291

4291 Timing Commander 软件 for Programmable Buffers

2023-05-15 19:16:04 0

0 今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54:43 985

985

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00:02 1397

1397

Timing Commander 硬件 Interfaces 用户指南

2023-07-06 18:35:05 0

0 9FGV1005 PhiClock PCIe Timing Commander 软件 用户指南

2023-07-07 19:27:28 0

0 9FGV1006 Timing Commander 用户指南

2023-07-07 19:28:06 0

0 9FGV100x Timing Commander 用户指南

2023-07-07 19:28:21 0

0 Timing Commander 软件 for VersaClock 3S - 5P3502x

2023-07-10 19:34:18 0

0 VersaClock 6 Timing Commander 用户指南

2023-07-11 19:27:17 1

1 Timing Commander 软件 for Programmable Buffers

2023-07-11 20:27:38 0

0 积 (PPA)。 通过采用 Tempus Timing Solution,Realtek 将生产力提升了 2 倍,与之前使用的方法相比,设计收敛周转时间缩短了 50%。此外,Realtek 的计算成本和内存占用

2023-11-06 10:10:01 206

206 今天想来聊一聊timing model。Top层在做STA的时候,为了速度的考量,有的时候不会把所有block都做flatten(展平化)处理

2023-12-06 14:03:13 270

270

电子发烧友App

电子发烧友App

评论