如果你参加过IC校招面试,自然会被问到“setup/hold的概念,以及setup/hold违例怎么办?”

这时候,你肯定会立马在脑海中从打拍或者插buffer两个答案中选一个。但是在实际项目中,往往没有这么简单。举一个实际的场景:

AXI master和AXI slave这一簇信号出现setup时序违例怎么办?

1、从AXI master 到AXI slave 出现setup违例;

2、从AXI slave 到AXI master出现setup违例;

3、两者都出现setup时序违例。

所以AXI master和AXI slave之间的打拍会存在4中模式:

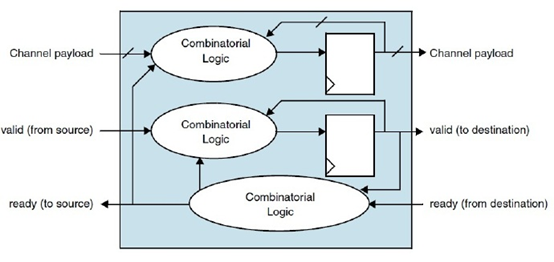

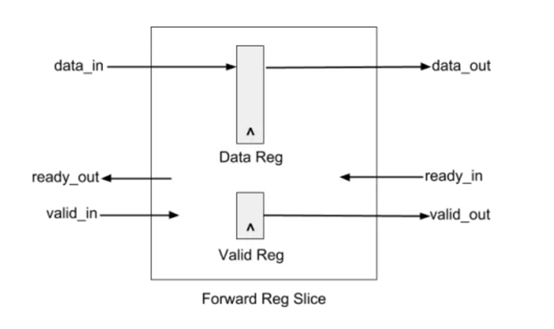

Forward Registered :对valid和payload路打拍

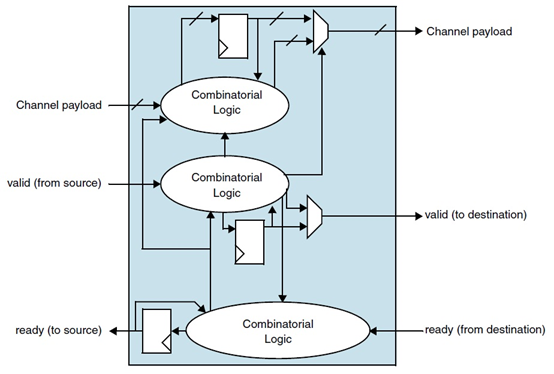

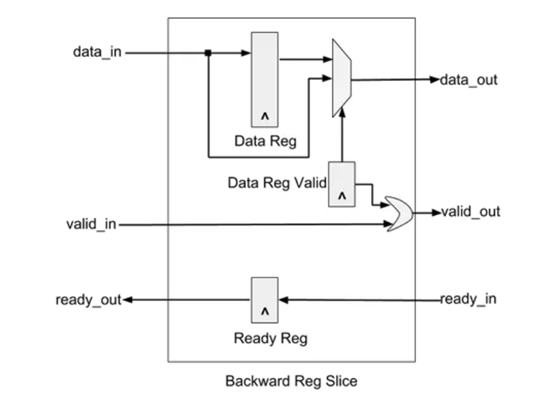

Backward Registered :对ready路打拍

Fully Registered :同时对valid/payload路和ready路打拍

Pass Through Mode:Bypass,均不打拍

这个问题没那么容易或者说不能够直接打拍,是因为这一簇信号遵循valid-ready协议,需要打拍的信号间存在时序的耦合。

所以问题就简化成如何在遵循valid -ready协议的master和slave 之间完成“打拍”,或者说在打拍的同时处理valid-ready协议。

Forward Registered

always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) valid_dst 《= 1’d0; else if (valid_src == 1‘d1) valid_dst 《= #`DLY 1’d1; else if (ready_dst == 1‘d1) valid_dst 《= #`DLY 1’d0;end always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) payload_dst 《= ’d0; else if (valid_src == 1‘d1 && ready_src == 1’d1) payload_dst 《= #`DLY payload_src;end ready_src = (~valid_dst) | ready_dst

现在来分析下上述Forward Registered 打拍代码的几个输出端口:

valid_dst:在master发请求(拉高valid_src)时拉高valid_dst,直到当前master没有valid请求并且slave可以接收请求(拉高ready_dst)时拉低valid_dst,表示一次传输完成。

payload_dst:在master发请求(拉高valid_src),并且前面没有请求、请求已经被接收或者正在被接收时将payload_src打拍赋给payload_dst。

其实master本身也会遵循valid-ready协议,payload_src和valid_src做同样处理就行,即也可以在(valid_src == 1‘d1 && ready_src == 1’d0)时进行赋值,因为此时payload_src输入应该约束保持原始数据。

ready_src:register slice或者slave可以接收数据时拉高ready_src.

Backward Registered

always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) valid_tmp0 《= 1’d0; else if (valid_src == 1‘d1 && ready_dst == 1’d0 &&valid_tmp0 == 1‘d0) valid_tmp0 《= #`DLY 1’d1; else if (ready_dst == 1‘d1) valid_tmp0 《= #`DLY 1’d0;end always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) payload_tmp0 《= ’d0; else if (valid_src == 1‘d1 && ready_dst == 1’d0 &&valid_tmp0 == 1‘d0) payload_tmp0 《= #`DLY payload_src;end assign payload_dst = (valid_tmp0 == 1’d1) ?payload_tmp0 : payload_src; always @(posedge clk or negedge rst_n)begin if (rst_n == 1‘d0) ready_src 《= 1’d0; else ready_src 《= #`DLY ready_dst;end

Backward Registered 打拍相比较Forward Registered 会复杂点,因为存在slave没有ready时master发来请求,需要暂存payload的场景。

现在来分析下上述Backward Registered打拍代码的几个输出端口:

ready_src:对ready通路直接进行打拍。

valid_dst:当slave没有ready,master发来请求时拉高标志位valid_tmp0,表示下一次slave准备好之后应该从register slice内暂存的payload拿数据

payload_dst:当slave没有ready,master发来请求时暂存payload到payload_tmp。最终的payload_dst根据标志位valid_tmp0从payload_tmp和payload_src之间选择

Fully Registered

类似于,简单理解就是个乒乓BUFFER,使用非空信号做valid_dst;payload的非满信号做ready_src

Pass Through Mode

直接相连

通过上述分析,可以使用register slice mode参数化的库,在后端要求AXI BUS打拍时直接调用,而无需重复造轮子。

编辑:lyn

-

IC

+关注

关注

36文章

6465浏览量

186296 -

时序

+关注

关注

5文章

411浏览量

38998 -

Setup

+关注

关注

0文章

30浏览量

12456 -

MASTER

+关注

关注

0文章

112浏览量

12244

原文标题:打拍优化时序不像听起来那么简单

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

内置氮化镓成主流?AHB技术你又了解多少?

数字IC/FPGA设计中的时序优化方法

SLM2004SCA-13GTR 200V高压半桥驱动芯片的可靠性与时序优化设计

网络接口:数字世界的“门铃”,你了解多少?

vivado时序分析相关经验

NVMe高速传输之摆脱XDMA设计22:PCIe的TLP读优化处理

NVMe高速传输之摆脱XDMA设计16:TLP优化

科普|关于GPS和GNSS,你了解多少?

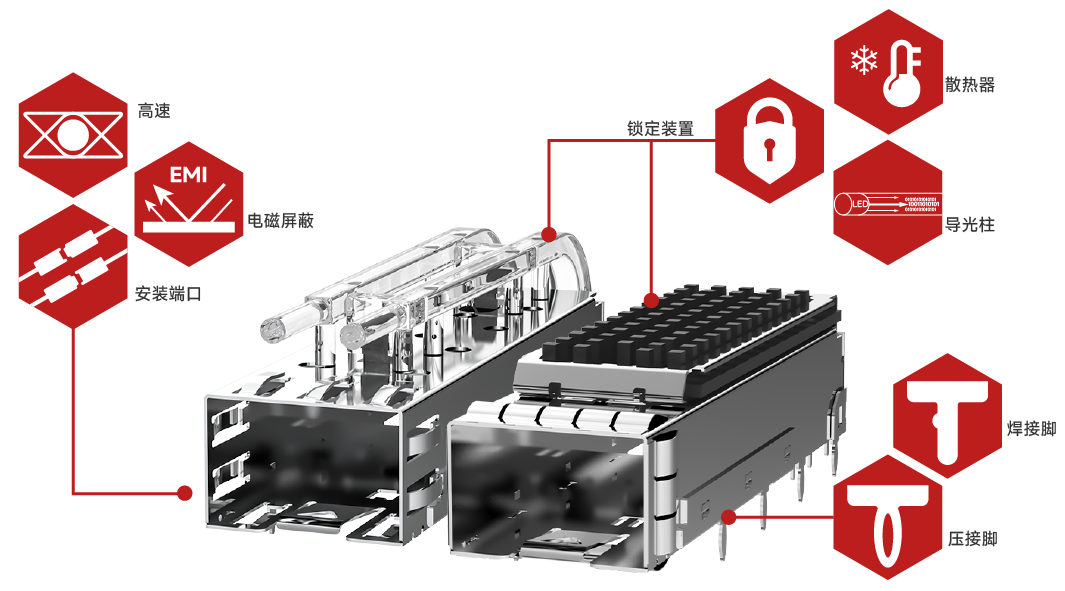

关于SFP连接器你必须了解的那些知识

鸿蒙5开发宝藏案例分享---性能优化案例解析

EMI电源滤波器:你真的了解它吗?

充电接口你真的了解吗?

FPGA时序约束之设置时钟组

关于打拍优化时序你真的全面了解吗?

关于打拍优化时序你真的全面了解吗?

评论